Einsatz der Vektor-Interrupt-Baugruppe

Nach Vermittlung der Grundlagen der Mikrocomputer-Technik kann die hier beschriebene Vektor-Interrupt-Baugruppe im Rahmen der Interface-Technik für Einstieg in die Interrupt-Technik und für eine

Vertiefung benutzt werden. Um den Einstieg für den Lernenden überschaubar zu gestalten, kann man mit einer Minimalkonfiguration arbeiten:

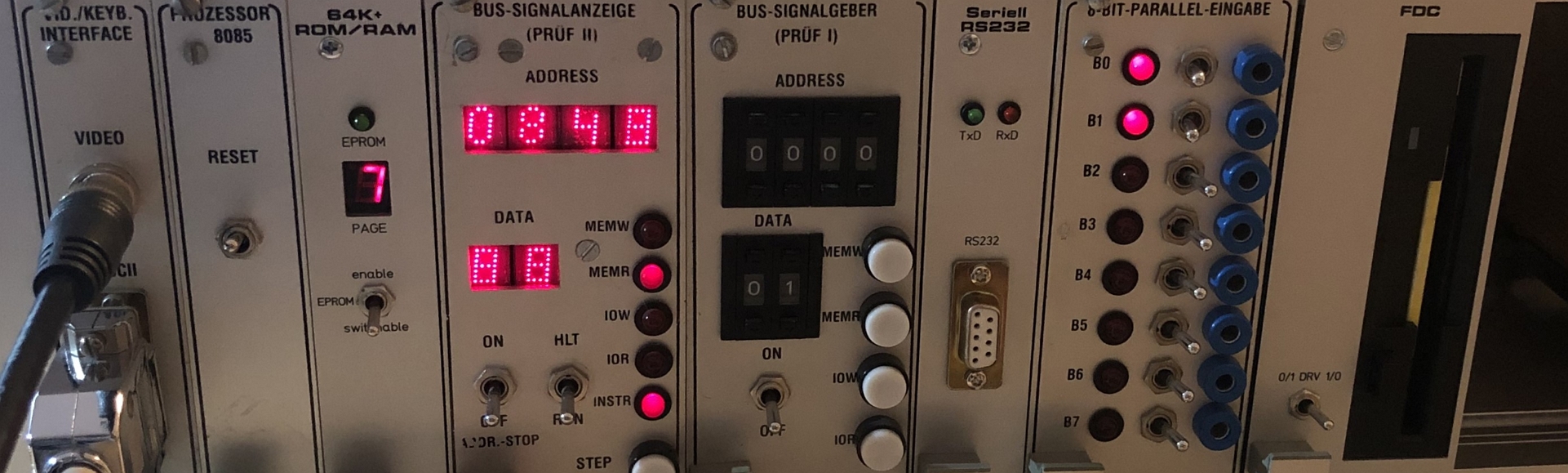

- CPU-Baugruppe

- BK-RAM-Baugruppe

- Bus-Signalgeber

- Bus-Signalanzeige (Adresse: 0000)

(zur Programmeingabe und für den Einzelschrittbetrieb)

Mittels der aufgeführten Konfiguration können die Grundlagen der Interrupt-Technik anhand kleiner Beispiele/ Anwendungen erarbeitet werden. In dieser Einstiegsphase kann beim Einsatz der Vektor-Interrupt-Baugruppe vorerst auf folgende tiefergehende Vorkenntnisse verzichtet werden:

- tiefere Kenntnisse über das Betriebsprogramm

- tiefere Kenntnisse über erweiterte Hardware-Strukturen, die unter Umständen “interruptgesteuert“

arbeiten (siehe Floppy-Disk) - Kenntnisse über weitere Interrupt-Eingänge sowie über Priorität, Maskierung und Schachtelung

von Interrupt-Eingängen.

Eine Vertiefung der Interrupt-Technik kann danach unter dem Betriebsprogramm MAT85 (inklusive Erweiterung) erfolgen. Hier können dann die weiteren Interrupt-Eingänge RST 5.5, RST 6.5, RST 7.5 und TRAP behandelt werden. In diesem Rahmen eröffnen sich weitere Anwendungsgebiete unter Zuhilfenahme der bereits -vorhandenen Baugruppen und Modelle. Einige Beispiele und weitergehende Anregungen sind in der folgenden Beschreibung der Baugruppe zu finden.

Einleitung

Beim Einsatz eines Mikrocomputers im Bereich der Steuer-, Mess- und Regelungstechnik ist es notwendig, dass der Mikrocomputer auf externe Ereignisse sofort reagieren muss.

Ein Beispiel hierzu ist der Einsatz in der chemischen Industrie. In einem chemischen Prozess muss zum Beispiel die Prozesstemperatur und der Druck geregelt und auf Grenzwerte hin überwacht werden. Der Zeitpunkt, an dem eine bestimmte Temperatur bzw. ein bestimmter Druck erreicht wird, ist unbestimmt. Bedingungen wie Umgebungstemperatur oder Heizleistung beeinflussen den Prozessablauf, so dass die genannten Zeitpunkte nicht durch ein vorgegebenes Programm erfasst werden können. Der Prozess und die vom Programm vorgegebene Arbeitsweise des Mikrocomputers verlaufen nicht synchron – sie sind also asynchron. Wie erreicht man nun, dass der Mikrocomputer prozesssynchron arbeitet?

Um dem Mikrocomputer eine Möglichkeit zu geben, während seiner Programmabarbeitung auf externe Ereignisse reagieren zu können, besitzen alle Mikroprozessoren Interrupt-Eingänge (Unterbrechungseingänge).

Bei einem Signal an einem Interrupt-Eingang unterbricht der Mikroprozessor seine momentane, durch das Programm Vorgegebene . Arbeit und bearbeitet das Programm für den Interrupt auslösenden Prozess. Nach dieser prozesssynchronen Bedienung setzt der Mikroprozessor seine unterbrochene Tätigkeit fort. Wie eine dafür notwendige Interrupt-Logik aufgebaut sein muss und wie der Mikroprozessor seine eigentliche Arbeit geordnet unterbricht und auch wieder aufnimmt, soll im folgenden aufgezeigt und erarbeitet werden. Die Beschreibung der Vektor-Interrupt-Baugruppe erfolgt nach einer grundlegenden Einführung in die Interrupt-Technik.

Grundlagen der Interrupt-Technik

Abfrage-Technik – polling –

Mikrocomputer arbeiten taktgesteuert nach einem vorgegebenen Programm, d. h., der Programmierer legt durch das Programm die Arbeit des Mikroprozessors und die Reihenfolge der Bedienung von externen Geräten fest. Die externen Geräte / Prozesse werden in der vorn Programm vorgegebenen Reihenfolge bedient. Ob eine Bedienung erfolgen soll, kann z.B. über ein Status-Bit bei programmierbaren IO-Port’s, an welche die Geräte angeschlossen sind, ermittelt werden. Diese Vorgehensweise bezeichnet man als

polling: Abfrage-Technik.

Nachteil dieser beschriebenen Abfrage-Technik ist die durch das Programm fest vorgegebene Reihenfolge, wobei unvorhergesehene, wichtige Ereignisse unter Umständen zu spät erkannt und bedient werden. Auch wenn keine kritischen Ereignisse auftreten, so wird der Prozessor die meiste Zeil mit der Abfrage nach Geräte-Bedienung verbringen.

Diese Abfrage-Technik ist rein programmgesteuert und daher einfach. Aus diesem Grund lassen sich evtl. Fehler in der Erstellungsphase oder später im Betrieb leichter lokalisieren und beheben.

Beispiel für ein Programm nach dem Polling-Verfahren:

Bild 1 Flussdiagramm „Polling-Methode“

Wie dieses Beispiel zeigt, ist die Struktur des Programms zwar übersichtlich, aber fest vorgegeben.

Für fast alle Anwendungen des Mikrocomputers benötigt man variable Strukturen und Reaktionen, die sich den Anforderungen durch die Peripherie anpassen.

Unterbrechungstechnik – interrupt –

Wie es der Name „Unterbrechungstechnik“ schon sagt, wird der Mikroprozessor in seiner programmgesteuerten Arbeit durch ein externes Ereignis unterbrochen. Solche Ereignisse kommen von den an den Mikrocomputer angeschlossenen Geräten ( Floppy Disk, Drucker, Maus, Terminal, Lichtgriffel, … ) oder von einem anderen Mikrocomputer (Informationsaustausch) bzw. von der Prozessperipherie, Schalter, Sensoren und Grenzwertmeldern für Wege, Füllstände, Temperatur, Drehzahl, Druck, … ). Die Verbindung Mikrocomputer/ Peripherie erfolgt über ..

- parallele Ein-/Ausgabe-Schnittstellen,

- serielle Ein-/Ausgabe-Schnittstellen,

- Analog-Digital-Wandler,

- Digital-Analog-Wandler und

- spezielle Schnittstellen (IEC-Bus, Floppy-Bus, .. ).

Beispiele:

- Ein digitaler Drehzahlgeber sendet einen Impuls, der erfasst werden muss

- Bei einer Datenübertragung zwischen zwei Mikrocomputern ist der Eingabe-Puffer der Schnittstelle voll, d.h., das empfangene Zeichen muss gelesen werden.

- Von einer Floppy-Disk-Station kann das nächste Zeichen gelesen werden.

- Zeitsteuerung durch einen Uhr-Impuls.

Um zu wissen, wie die Melde- bzw. die Bedienungslogik in einem Mikrocomputer hard- und softwaremäßig aussehen muss, sind verschiedene Kriterien zur Beurteilung zu beachten:

- Welche Priorität (Wichtigkeit) hat ein Ereignis?

(Wird ein Temperatur-Grenzwert gemeldet, so hat diese Meldung sicherlich Vorrang vor einem Datenaustausch mit einem Drucker. - Wann tritt ein Ereignis auf?

a) zeitlich regelmäßig (z.B.: Uhrimpulse)

b) zeitlich unregelmäßig (z.B.: Sollwert-Temperatur erreicht) - Häufigkeit von Ereignissen

a) häufig: Uhrimpulse

b) selten: Sollwert-Temperatur erreicht

Aus den genannten Kriterien sieht man schon, wie komplex eine interruptgesteuerte Arbeit durch den Mikrocomputer sein kann.

In den folgenden Kapiteln soll jedoch auf eine einfache Art und Weise in dieses Thema eingeführt werden.

Mikrocomputer haben für die Interrupt-Steuerung mindestens einen Interrupt-Eingang, dieser wird

- INTR: interrupt bzw.

- IRQ: interrupt request (Interrupt-Anforderung)

genannt.

Bild 2 Interrupt-Eingang

Ablauf einer Interrupt-Bearbeitung:

Beim Eintreffen eines Interrupt-Signals läuft folgendes Schema ab:

- Der von der CPU gerade bearbeitete Befehl wird zu Ende geführt, da die CPU sich nicht merken kann, wie weit sie einen Befehl bereits abgearbeitet hat.

- Die Adresse des nächsten Befehls wird automatisch im Stack (Stapelspeicher, RAM-Bereich für die CPU) gespeichert – wie bei einem Unterprogrammaufruf.

- Die CPU setzt ihre Arbeit bei dem zur Unterbrechungsanforderung gehörenden Programm (interrupt-service-routine, ISR) fort.

- Ist das Unterbrechungsprogramm bearbeitet, so holt sich die CPU durch einen RETURN-Befehl (der letzte Befehl in der ISR muss ein RET-Befehl sein) die Rückkehradresse vom Stack und setzt ihre Arbeit in dem unterbrochenen Programm fort.

Der hier beschriebene Ablauf zur Bedienung eines Interrupts gleicht dem eines Unterprogrammaufrufs (CALL-Befehl). Bei der Interrupt-Bedienung handelt es sich um einen asynchron hardware-gesteuerten Unterprogrammaufruf. In der Interrupt-Service-Routine müssen die im Programm verwendeten Parameter (Werte, Registerinhalte) gerettet und vor der Rückkehr in das unterbrochene Programm wieder zurückgespeichert werden.

Interrupt-Freigabe und Sperrung

Interrupt-Eingänge verbessern die Anpassung an interne und externe Gegebenheiten – erschweren aber die Erstellungs- und Testphase eines interruptgesteuerten MC-Systems. Weiterhin ist manchmal in wichtigen Befehlssequenzen eine Unterbrechung nicht erwünscht, wenn es sich z.B. um zeitkritische Befehlssequenzen handelt.

Beispiel: Ein Drehzahlzähler muss ausgelesen werden, sonst erfolgt ein Überlauf. Die folgende Befehlsseguenz muss ohne Unterbrechung ablaufen.

IN CNT1LO ;Zähler 1 LOW-Byte lesen

STA DREZLO ;abspeichern

IN CNT1HI ;Zähler 1 HIGH-Byte lesen

STA DREZHI ;abspeichern

Aus den genannten Gründen heraus lassen sich Interrupt-Anforderungen

durch einen Programm-Befehl sperren.

Eine Sperrung der Interrupt-Annahme erfolgt durch:

DI disable interrupt (Interrupt verhindern).Dieser Zustand „gesperrter Interrupt“ ist nach dem Einschalten des MC-Systems automatisch eingestellt und erm6glicht eine unterbrechungsfreie Initialisierung (Grundeinstellung von Speicher und 10-Ports) des MC-Systems. Jedes RESET-Signal erzeugt auch den Interruptzustand „gesperrt“.

Damit anstehende Interrupt-Signale angenommen und bearbeitet werden, muss vorn Programm her der Befehl:

EI enable interrupt (Interrupt ermöglichen}gegeben werden.

Kommt nun bei freigegebenem Interrupt ein Interrupt-Signal, so wird in der CPU automatisch der Zustand „DI“ eingenommen. Erst durch eine ausdrückliche Freigabe über den Befehl „EI“ kann ein weiterer Interrupt erkannt und bearbeitet werden. Diese Freigabe kann -wenn notwendig- direkt am Anfang einer Interrupt-Service-Routine vorgenommen werden. Üblich ist eine Freigabe vor dem letzten Befehl „RET“ in der ISR. Der RET-Befehl wird dann noch von der CPU ausgeführt und erst danach erfolgt die Interrupt-Freigabe.

Merke:

- Interrupte sind nach dem Einschalten des MC-Systems gesperrt.

- Jedes RESET-Signal sperrt die Interrupt-Annahme.

- Eine Interrupt-Annahme wird erst durch den Befehl „EI“ ermöglicht.

- Jede Interrupt-Annahme sperrt eine weitere Annahme; sie muss

durch den Befehl „EI“ wieder freigegeben werden. - Es ist jederzeit m6glich, durch den Befehl „DI“ eine InterruptFreigabe

wieder zu sperren.

Interrupt, Polling

Es stellt sich nun die Frage: „Wieviele Interrupt-Eingänge benötigt eine CPU oder kann man an einen Interrupt-Eingang mehrere Interruptsignale anschließen?“ Zu dieser Frage bieten die MikroprozessorHersteller mehrere Lösungen an bzw. der Hard-/Software-Entwickler muß diesbezüglich Hardware-Erweiterungen vornehmen.

Hardware-Erweiterung

Eine einfache Erweiterung eines Interrupt-Eingangs an der CPU lässt sich mit Hilfe eines ODER-Gatters vornehmen (siehe Bild 3).

Bild 3 Erweiterung eines INTR-Eingangs

Die Auffächerung des Interrupt-Eingangs an der CPU mittels eines ODER-Gatters erlaubt nun, von mehreren Geräten Interrupt-Signale anzuschließen. Wie aber kann unterschieden werden, durch welches Gerät ein Interrupt ausgelöst wurde? In der Interface-Technik ergeben sich immer drei grundsätzliche Lösungen:

- die Hardware-Lösung (z.B. interrupt}

- die Software-Lösung (z.B. polling)

- eine Mischung von Hard-/Software-Lösung (z.B. interrupt/polling)

Software-Lösung: Polling

Im Fall eines eintreffenden Interrupts setzt die CPU ihre Arbeit an einer zu dem Interrupt-Eingang gehörenden Programm-Adresse fort. Diese Adresse ist vom Hersteller der CPU festgelegt. Ab dieser Adresse kann der Anwender ein kurzes Identifikationsprogramm schreiben, das alle angeschlossenen Geräte abfragt und überprüft, welches der Geräte einen Interrupt ausgelöst hat. Dazu besitzen die programmierbaren Schnittstellen-Bausteine, über welche die Peripheriegeräte angeschlossen sind, ein Statusregister (Zustandsregister). In diesem Statusregister wird ein Bit (z.B. Bit 7) bei einer Interruptanforderung gesetzt.

Zu der Hardware-Lösung „Gerätebedienung durch Interrupt“ kommt nun eine Software-Lösung „Suchen des interruptauslösenden Gerätes durch polling“.

Dazu ein Beispiel:

PROGRAMM

:

EI ; Interrupt erlauben

:

:

: <- (1) Interrupt trift ein

:

(2) IDENT: IN GER1 ;Status von Geraet 1 lesen

ANI 80 ;Interrupt-Bit gesetzt?

JNZ ISR1 ;ja, Interrupt bedienen

IN GER4 ;nein, weiter suchen

ANI 80 ;

JNZ ISR4 ;

IN GER2 ;

ANI 80 ;

JNZ ISR2 ;(3) ja, Geraet 3 hat den

;Interrupt ausgeloest

usw.

ISR1: : ;Bedienung von Gerät 1

:

:

EI ;Interrupt wieder zulassen

RET ;zurueck

(3) ISR2: : ;Bedienung von Gerät 2

:

:

EI ;Interrupt wieder zulassen

RET ;zurueck

ISR3: : ;Bedienung von Gerät 3

:

:

EI ;Interrupt wieder zulassen

RET ;zurueck

Ablauf:

Trifft in dem normalen „Programm“ ein Interrupt ein (1), so führt die CPU den gerade bearbeiteten Befehl zu Ende und speichert die Rückkehradresse des nächsten auszuführenden Befehls im Stack. Danach arbeitet die CPU an der Interrupt-Adresse weiter, wo die Identifikationsroutine steht (2). Bei dem Gerät, das einen Interrupt ausgelöst hat, erfolgt eine Verzweigung zu der entsprechenden Interrupt-Service-Routine (ISR .. ) (3). Am Ende der ISR wird der Interrupt wieder freigegeben. Durch den Befehl „RET“ wird die CPU veranlasst, die Rückkehradresse vom Stack zu lesen (4) und an der unterbrochenen Stelle (5) weiter zu arbeiten.

Durch die Reihenfolge der Abfrage der Schnittstellen-Statusregister kann der Programmierer eine bestimmte Priorität in der Reihenfolge der Bedienung festlegen (siehe Beispiel: Gerät 1, Gerät 4, Gerät 2). Eine Gerätebedienung wie zum Beispiel „Drehzahlimpuls“ kommt in der Identifikationsroutine als eine der ersten Abfragen. Das Gerät, dessen Status zuerst abgefragt wird, hat die höchste Priorität. Nachteilig bei diesem Verfahren ist das Suchen nach dem anfordernden Gerät. Dadurch entstehen unterschiedlich lange Reaktionszeiten bei der Bedienung eines Interrupts.

Vektor-Interrupt

Hardware-Lösung

Eine Möglichkeit, das Suchverfahren bei der Interrupt/ Polling-Methode zu umgehen, bietet der „Vektor-Interrupt“. Bei dieser Methode sind einem Interrupt-Eingang mehrere Interrupt-Adressen im Speicher zugeordnet. Zusätzlich zu dem Interrupt-Eingang „INTR“ steht ein Quittungsausgang „INTA“ (interrupt-acknowledge, Interrupt bestätigen bzw. angenommen) zur Verfügung (siehe Bild 4).

Bild 4 Vektor-Interrupt-Erzeugung

Ablauf: Nach der Annahme des Interrupts (1) durch die CPU sendet diese ein Quittungssignal INTA „Interrupt angenommen“ (2). Mit diesem Signal kann das anfordernde Peripheriegerät veranlasst werden, eine Geräte-Kennung auf den Datenbus zu senden (3). Die CPU liest diese Kennung und kann direkt zu der entsprechenden Interrupt-Service-Routine verzweigen.

Bei der Vektor-Interrupt-Methode gibt sich das anfordernde Gerät durch eine „Kennung“ – hervorgerufen durch das Lesesignal INTA der CPU – selbst zu erkennen.

Intel als Hersteller der 8080/85-CPU und auch die Firma Zilog als Hersteller der Z80-CPU bieten die Möglichkeit, maximal 8 Adressvektoren zu bilden. Diese Adressvektoren (Zieladressen) sind in der folgenden Tabelle dargestellt.

| Kennung (durch INTA gelesen) binär | hex | Zieladresse hex |

|---|---|---|

| 1 1 0 0 0 1 1 1 | C7 | 0 0 0 0 |

| 1 1 0 0 1 1 1 1 | CF | 0 0 0 8 |

| 1 1 0 0 1 1 1 1 | D7 | 0 0 1 0 |

| 1 1 1 0 1 1 1 1 | DF | 0 0 1 8 |

| 1 1 0 1 1 1 1 1 | E7 | 0 0 2 0 |

| 1 1 1 0 1 1 1 1 | EF | 0 0 2 8 |

| 1 1 1 1 0 1 1 1 | F7 | 0 0 3 0 |

| 1 1 1 1 1 1 1 1 | FF | 0 0 3 8 |

Interrupt-/Prioritätskodierung

Für eine funktionierende Hardware zur Interruptsteuerung benötigt man eine Schaltung, die die Kennung und die – wie bei der Software-Lösung eine Priorität bei mehreren Interrupten erzeugt.

Das folgende Bild zeigt die dazu notwendige Schaltung.

Bild 5 Vektor-Interrupt und Prioritätskodierung

Die von den externen Geräten kommenden Interruptsignale gelangen über eine Prioritätskodierung (UND-Gatter) zum einen über das ODER-Gatter an den Interrupteingang, zum anderen wird aus ihnen über den 1 aus 8 in dual Prioritätskodierer ein Teil der Kennung gebildet (Datenleitungen D3, D4, D5). Die restlichen Datenleitungen bei der Kennung (D0, D1, D2 und D6, D7) führen laut vorhergehender Tabelle 1-Signal. Durch den Tristate-Treiber gelangt die Kennung beim Lesen durch die CPU mit dem INTA-Signal auf den Datenbus. Je nach eintreffendem Interrupt verzweigt die CPU zu der entsprechenden Zieladresse und der dazugehörenden Interrupt-Service-Routine.

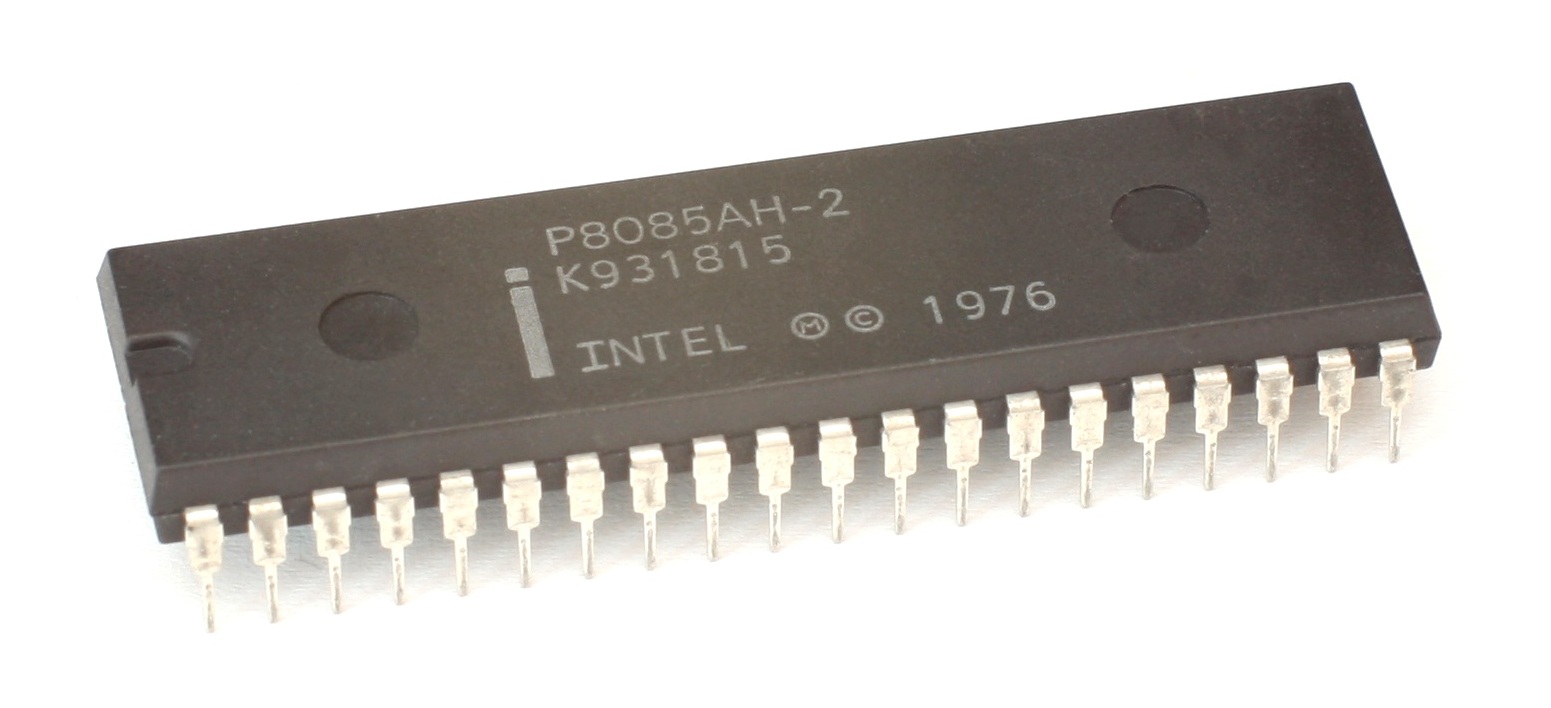

Interruptsystem CPU 8085

Interrupt-Anschlüsse

Die CPU 8085 von INTEL bietet ohne Hardwareerweiterung ein gut ausgebautes Interruptsystem. Sie hat mehrere Interrupteingänge und die in den vorhergehenden Kapiteln besprochene Interrupt-/Prioritätskodierung (interrupt controller, Unterbrechungsteuerung).

Bild 6 Interrupt-Anschlüsse CPU 8085

Außer dem Interrupteingang INTR hat die CPU 8085 noch die Interrupteingänge:

- TRAP (Falle, nicht maskierbarer Interrupt)

- RST 7.5 (Restart 7.5)

- RST 6.5 (Restart 6.5)

- RST 5.5 (Restart 5.5)

Interrupt-Adressen

Die zu den Interrupteingängen gehörenden Zieladressen sind in der folgenden Tabelle zusammengestellt.

| Interrupt-Anschluss | Zieladresse |

|---|---|

| TRAP (RST 4.5) | 0 0 2 4 |

| RST 7.5 | 0 0 3 C |

| RST 6.5 | 0 0 3 4 |

| RST 5.5 | 0 0 2 C |

| INTR | hängt von der gelesenen Kennung ab (Siehe Tabelle Interrupt Vektor Erzeugung) |

Hinweis: Die Zieladresse läßt sich über die Interrupt-Nr. berechnen.

Beispiel: RST 4.5 —-> ADR = 4.5 * 8 = 36/10 = 24/16

Interner Interrupt-Controller

Von dem internen Interrupt-Controller der CPU 8085 ist in dem folgenden Bild 7 ein vereinfachtes Prinzipschaltbild dargestellt.

Bild 7 Vereinfachte Interrupt-Steuerung CPU 8085

Wie aus der Prinzipschaltung zu ersehen ist, kann ein eintreffender Interrupt (H-Pegel an INTR) von der CPU nur dann erkannt werden, wenn das Interrupt-Enable-Flipflop (INTE-FF) gesetzt ist. Das Setzen des Flipflops erfolgt über den Maschinen-Befehl „EI“ (enable interrupt, FB/16, siehe Befehlsliste). Wird der Interrupt angenommen, so wird von der Control-Unit (CU, Steuereinheit in der CPU) das Lesesignal INTA (interrupt acknowledge, Interrupt angenommen, L-Pegel) zum Lesen des Interrupt-Vektors ausgegeben.

Das INTE-FF wird über das RESET-Signal oder einen angenommenen Interrupt oder durch den Befehl „DI“ (disable interrupt, F3/16, siehe Befehlsliste) zurückgesetzt. Dadurch ist eine Interrupt-Annahme gesperrt.

In dem folgenden Prinzipbild ist die gesamte Interrupt-Steuerung der CPU 8085 zu sehen.

Bild 8 Erweiterte Interrupt-Steuerung CPU 8085

Die höchste Priorität hat der Interrupt-Eingang TRAP (RST 4.5) und die niedrigste der Interrupt-Eingang INTR – diese Aussage gilt bei gleichzeitigem Anstehen mehrerer Interrupt-Anforderungen. Wie in dem Bild zu sehen ist, sind die Interrupt-Eingänge TRAP und RST 7. 5 flankengesteuert – gleichzeitig werden Interrupt-Signale – bis auf TRAP- in den Flipflops gespeichert.

Die restlichen Interrupt-Eingänge sind H-Pegel-gesteuert ohne Eingangssignal-Speicherung, d.h., Anforderungen müssen bis zur Annahme anstehen. Alle Interrupt-Eingänge bis auf den TRAP lassen sich über das INTE-Flipflop sperren.

Interrupt-Masken-Register

Bei der Anzahl von Interrupt-Eingängen der CPU 8085 muss es außer der generellen Freigabe über den EI-Befehl eine weitere Möglichkeit geben, die Interrupt-Anforderungen individuell zu sperren und freizugeben. Diese Forderung ergibt sich einmal von den verschiedenen Aufgabenstellungen her, zum anderen ist dies bei der Test- bzw. Inbetriebnahmephase notwendig. Bei der CPU 8085 ist eine solche individuelle Behandlung der Interrupt-Eingänge über das Interrupt-Masken-Register {I-Register) möglich.

Das Setzen einer Interrupt-Maske erfolgt durch den Maschinen-Befehl SIM (30/16, set interrupt mask, Interrupt Maske setzen). Bedeutung der Bit beim Schreiben in das I-Register:

| BIT | Register | Bedeutung |

|---|---|---|

| 7 | SOD | SOD-Ausgang der CPU |

| 6 | SOD EN | Freigabe: H |

| 5 | X | nicht verwendet |

| 4 | RES 7.5 | Rücksetzen des RST 7.5-Flip-Flops durch H-Pegel |

| 3 | MSE | Maske L: wird ignoriert H: wird gesetzt |

| 2 | M 7.5 | Unterbrechungsmaske: L: Interrupt erlaubt H: Interrupt gesperrt |

| 1 | M 6.5 | Unterbrechungsmaske: L: Interrupt erlaubt H: Interrupt gesperrt |

| 0 | M 5.5 | Unterbrechungsmaske: L: Interrupt erlaubt H: Interrupt gesperrt |

Anmerkung

Die Interrupt-Maske muss vor dem SIM-Befehl im Akkumulator stehen und wird durch ihn in das I-Register kopiert.

Beispiel:

MVI A,1B ; Maske:0 0 0 1 1 0 1 1/2

; Ruecksetzen RST 7.5-FF

; Maske freigeben, RST 7.5 freigeben

SIM ; Maske setzenSOD: seriell output data (serieller Datenausgang, Anschluss 4 an der CPU)

Das Bit 6 (SODEN, SOD enable, seriellen Ausgang freigeben) und das Bit 3 ( MSE, mask set enable, Maske setzen freigeben) werden aufgrund der zwei Funktionen des SIM-Befehls benötigt:

Interrupt-Maske setzen:

SOD-EN: L und MSE: H

Bit seriell ausgeben:

SOD-EN: H und MSE: L

Außer der Möglichkeit, eine Maske mit dem SIM-Befehl zu setzen, ist es möglich, den aktuellen Zustand des Interrupt-Systems mit dem Maschinen-Befehl RIM ( 20/16 , read interrupt mask, Interrupt Maske lesen) zu lesen. Nach dem RIM-Befehl steht das Zustands-Bitmuster im Akku.

ACHTUNG: Die oberen 4 Bit (Bit 4 bis Bit 7) haben beim Lesen des I-Registers eine andere Bedeutung als beim Schreiben.

Bedeutung der Bit beim Lesen des I-Registers:

| BIT | Register | Bedeutung |

|---|---|---|

| 7 | SID | Pegel am Eingang SID der CPU |

| 6 | I 7.5 | Flags für anstehende Unterbrechungen |

| 5 | I 6.5 | Flags für anstehende Unterbrechungen |

| 4 | I 5.5 | Flags für anstehende Unterbrechungen |

| 3 | IE | Unterbrechungs-Freigabe-Bit H: Maske ist freigegeben |

| 2 | M 7.5 | Aktuelle Unterbrechungsmaske: L: Interrupt erlaubt H: Interrupt gesperrt |

| 1 | M 6.5 | Aktuelle Unterbrechungsmaske: L: Interrupt erlaubt H: Interrupt gesperrt |

| 0 | M 5.5 | Aktuelle Unterbrechungsmaske: L: Interrupt erlaubt H: Interrupt gesperrt |

Anmerkungen:

SID: seriell input data (serieller Dateneingang, Anschluss 5 an der CPU).

Durch Bit 4 bis Bit 6 kann ermittelt werden, ob Interrupt-Signale an den Anschlüssen RST 5.5, RST 6.5 und RST 7.5 anstehen. Dies ist auch bei zeitweise gesperrtem Interruptsystem möglich.

Bild 9 Zusammenfassung Interrupt-Controller/-Masken-Register

Nutzung der Interrupte im BFZ/MFA-Mikrocomputer

Ein Teil des Interrupt-Systems wird von dem Betriebsprogramm MAT85 bzw. von der Erweiterung SP1 und MINI-DOS genutzt. Welche Interrupte es sind und wie sie genutzt werden, zeigt die folgende Tabelle.

| Interrupt-Eingang | Zieladresse | Nutzung durch das Betriebsprogramm |

|---|---|---|

| TRAP (RST 4.5) | 0 0 2 4 | MAT85, MONITOR RESTART, initialisiert den oberen RAM-Bereich neu |

| RST 7.5 | 0 0 3 C | Verzweigung in den RAM-Bereich: FC9E (1) Nutzung vom SPS-Interpreter (timer) |

| RST 6.5 | 0 0 3 4 | Verzweigung nach FC9B (wird von SPS und BASIC zum Programmabbruch über die Tastatur genutzt) |

| RST 5.5 | 0 0 2 C | Verzweigung nach FC95 (wird vom MINI-DOS genutzt, Floppy Disk) |

| INTR | Kennung | Adresse | Nutzung durch das Betriebsprogramm |

|---|---|---|---|

| 0 | C7 | 0 0 0 0 | MAT85, *RESET* |

| 1 | CF | 0 0 0 8 | MAT85, USER, Benutzer-Einsprung |

| 2 | D7 | 0 0 1 0 | frei, Verzweigung in den RAM-Bereich nach FC8C (1) |

| 3 | DF | 0 0 1 8 | frei, Verzweigung in den RAM-Bereich nach FC8F (1) |

| 4 | E7 | 0 0 2 0 | MAT85, BREAKPOINT |

| 5 | EF | 0 0 2 8 | frei, Verzweigung in den RAM-Bereich nach FC92 (1) |

| 6 | F7 | 0 0 3 0 | frei, Verzweigung in den RAM Bereich nach FC98 (1) |

| 7 | FF | 0 0 3 8 | MAT85, PROGRAM ABORT |

1) im RAM sind inklusive der angegebenen Adresse 3 Byte frei für einen Sprung in die Anwender-ISR frei für den Anwender

Ausblick:

Von den CPU-Herstellern werden externe Interrupt-Controller angeboten, die eine Erweiterung des Interruptsystems erlauben. Ein Beispiel sei hier der Interrupt-Controller von INTEL, der sehr weit verbreitet ist. Hinweise hierzu bei der Inbetriebnahme der Baugruppe.

Vektor-Interrupt-Baugruppe

Basisschaltung

Die in dem Kapitel 3.2.2 beschriebene Hardware-Erweiterung (ODER-Gatter) für den INTR-Eingang erfordert

- ein ODER-Gatter auf der CPU-Baugruppe und

- acht Bus-Leitungen als Interrupt-Leitungen.

In der realisierten Schaltung wird die ODER-Verknüpfung durch eine „wired-or-Verknüpfung“ (verdrahtetes ODER) erreicht. Die Ausgänge der einzelnen Interrupt-Quellen sind in „open-collector-Technik“ ausgeführt; der notwendige „pull-up-„Widerstand“ befindet sich auf der Bus-Aufsteckplatine, ebenso der notwendige Inverter als Schmitt-Trigger. Die verdrahteten ODER-Ausgänge liefern ein aktives Low-Signal. Da der Interrupt-Eingang INTR der 8085-CPU aber High-aktiv ist, wird ein Inverter benötigt. Die Aufsteckplatine muss deshalb bei Betrieb der Vektor-Interrupt-Baugruppe auf dem Bus aufgesteckt sein. Eine Busleitung INTRoc ( 24 c ) wird für das verdrahtete ODER benötigt, die zweite Busleitung (25c) ist die INTR-Leitung zur CPU-Baugruppe.

Da der INTR-Eingang keine Flankensteuerung mit Signalspeicherung besitzt, benötigen wir ein Flipflop als Interrupt-Signalspeicher – erinnern wir uns: Ein Interrupt kann gesperrt sein und muss solange anstehen,

bis er angenommen wird. Dieses wird durch das Flipflop erreicht, das bei der Bedienung des Interrupts mit dem INTA-Signal (Interrupt-Annahme, Vektor lesen) gelöscht wird.

Bild 10 Basisschaltung Vektor-Interrupt

Die notwendige Kennung wird über 3 DIL-Schalter eingestellt, hieraus ergeben sich 23 = 8 Adress-Vektoren. Über ein Tristate-Gatter werden die drei Leitungen auf den Datenbus geschaltet, die Freigabe der Kennung erfolgt mit dem INTA-Lesesignal ( siehe auch CPU-Baugruppe, Fachpraktische Übungen Band 1, Kap. 2.1).

Die restlichen Datenbus-Signale (D1, D2, D6 und D7) werden nicht von der Vektor-Interrupt-Baugruppe angesteuert; sie führen ohne Ansteuerung über die pull-up-Widerstände, die sich auf dem Busabschluss befinden, H-Pegel.

Ein Interrupt kann ..

- durch einen prellfreien Taster (TEST-/Handauslösung)

- oder durch ein externes Signal ausgelöst werden.

In der folgenden Tabelle sind in Abhängigkeit von den DIL-Schalterstellungen die Kennungen und die entsprechenden Zieladressen aufgelistet.

| SX3 D5 | SX2 D4 | SX1 D3 | Kennung Datenbus | Zieladresse (Adressvektor) |

|---|---|---|---|---|

| on | on | on | C7 | 0000 |

| on | on | off | CF | 0008 |

| on | off | on | D7 | 0010 |

| on | off | off | DF | 0018 |

| off | on | on | E7 | 0020 |

| off | on | off | EF | 0028 |

| off | off | on | F7 | 0030 |

| off | off | off | FF | 0038 |

Anmerkung:

Die Leitung D1 wird bei der „Erweiterung der Adressvektoren“ Kapitel 5.3.1 gebraucht, d.h., sie wird aktiv angesteuert

Prioritätskodierung: daisy chain

Bei der Prioritätskodierung „daisy chain“ (Gänseblümchen-Kette) handelt es sich, wie der Name grob beschreibt, um eine Kette, besser gesagt, um eine Prioritäten-Kette. Die einzelnen Vektor-Kodierungsschaltungen (kurz: V-K-Schaltung) sind wie die Glieder einer Kette miteinander verbunden, wobei die erste Schaltung die höchste, die letzte in der Kette die niedrigste Priorität hat (siehe Bild 11).

Bild 11 Prioritätskodierung „daisy-chain“

Beschreibung:

Liegt an der ersten Vektor-Kodierungsschaltung kein Interrupt vor, so ist das Interrupt-Flipflop nicht gesetzt und das INTA-Lesesignal gelangt an die in der Kette folgende V-K-Schaltung. Liegt ein Interrupt an (Bsp.: V-K-Schaltung 2), so ist das I-FF gesetzt und die Weitergabe des INTA-Lesesignals über das UND-Gatter gesperrt. Kommt nun bei der Interrupt-Annahme das INTA-Lesesignal von der CPU, so gelangt es bis zu dem ersten gesetzten I-FF in der Kette. Die CPU kann aufgrund des gesetzten I-FF die Kennung dieser Vektor-Kodierungsschaltung (V-K-Schaltung 2) lesen.

Das gezeigte daisy-chain-Verfahren eignet sich besonders gut für MC-Systeme in Einschubtechnik, wo die Interrupte von den verschiedenen Baugruppen kommen, ausgelöst von den angeschlossenen Peripheriegeräten. Auf dem Systembus werden bei diesem Verfahren nur 2 Busleitungen benötigt,

- eine Leitung für den Sammelinterrupt und

- eine Leitung für die Prioritätenkette.

Die Schnittstellen-Bausteine der Firma Zilog beinhalten das daisychain-Verfahren, so dass es sehr einfach ist, ein Vektor-Interrupt-System aufzubauen; sei es auf einer Baugruppe oder in einem Einschubsystem.

Realisierte Schaltung

Die vollständige Schaltung in Bild 12 hat gegenüber der Schaltung in Bild 10 folgende Ergänzungen:

- Prioritätskodierung: „daisy-chain“,

- Monoflop für ein zeitlich begrenztes Setzsignal, so dass bei sofortiger Annahme das Interrupt-Flipflop gelöscht werden kann, auch wenn das Anforderungssignal länger ansteht. Die Monoflopeingänge erlauben eine positive/negative Flankenansteuerung.

- Eine Erweiterung des Adressvektors durch die Leitung Datenleitung D1.

Bild 12 Schaltbild für eine Vektor-Interrupt-Kodierung und Prioritätskodierung

Die Ergänzungen in der realisierten Schaltung “Vektor-Interrupt-Baugruppe“ erweitern die Einsatzmöglichkeiten der Baugruppe.

Durch die Erweiterung des Adressvektors mittels der Datenleitung D1 (Punkt c) ergibt sich die Möglichkeit einer anschaulichen Einführung in den komplexeren Interrupt-Controller 8259, der in den Personal-Computern und in der Industrie häufig eingesetzt wird.

Erweiterung der Adressvektoren

Die CPU 8085 kann, außer den 8 schon beschriebenen Interrupt-Kennungen, eine weitere Kennung lesen und dekodieren.

Diese zusätzliche Kennung in Verbindung mit dem externen Interrupt Controller 8259 ermöglicht eine Erweiterung der bisher kennengelernten Interrupt-Vektoren. Vom CPU-Hersteller wurde dazu eine flexible

Interrupt-Kennung genommen:

CD/16 = 1 1 0 0 1 1 0 1 /2

Diese Kennung ist der Maschinen-Befehl: CALL ADR ( ein Unterprogramm-Aufruf mit der Adresse: ADR ).

Hierdurch ist es möglich, den gesamten von der CPU adressierbaren Speicherbereich über einen von einem externen Interrupt-Controller gelieferten Adressvektor als Interrupt-Adresse zu benutzen.

Um nun die Kennung CD/16 kodieren zu können, benötigen wir auf der Vektor-Interrupt-Baugruppe einen weiteren Schalter zur Einstellung dieser Kennung. Betrachten wir die Kennung CD/16 als Dualcode, so ist zu sehen, dass die Datenleitung „D1“ auf Low-Potential gelegt werden muss.

| Datenleitungen | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| Pegel | H | H | L | L | H | H | L | H |

Ablauf einer Interrupt-Anforderung mit der Kennung CD/16

Stellen wir der CPU nach einer Interrupt-Anforderung über einen vierpoligen DIL-Schalter die Kennung CD/16 zur Verfügung, so erzeugt die CPU nach dem Einlesen dieser Kennung mittels INTA-Signal zwei weitere INTA-Lesezyklen. Mit dem ersten INTA-Lesezyklus liest die CPU das Low-Byte und mit dem zweiten INTA-Lesezyklus das High-Byte des zur Kennung benötigten Adressvektors. Danach schreibt die CPU wie bei einem CALL-Befehl die Rückkehradresse in den vom Stack-Pointer adressierten Stapelspeicher und verzweigt zu dem gelesenen Adress-Vektor. Im Gegensatz zu den bisher kennengelernten Kennungen, die einen bestimmten Adressvektor in der CPU erzeugten, ist dieser Adressvektor einstellbar.

Der Interrupt-Controller 8259 liefert den notwendigen Adressvektor automatisch – er lässt sich durch Steuerwörter programmieren. Bei der Vektor-Interrupt-Baugruppe lässt sich ebenfalls ein Adressvektor

über eine dazu geeignete Hardwarelösung einstellen. Dazu müssen drei Vektor-Interrupt-Schaltungen durch eine „daisy-chain“-Kette miteinander verbunden werden und über die drei parallel zu schaltenden

Eingänge angesteuert werden.

Das folgende Bild 13 zeigt die notwendige „daisy-chain“-Kette, bestehend aus drei Grundschaltungen. Aus diesen drei Grundschaltungen besteht die Vektor-Interrupt-Baugruppe – siehe Anhang. Die Interrupt-Eingänge INTRA bis INTRo sind miteinander verbunden, so dass ein Interruptsignal alle drei Interrupt-Anforderungs-Flipflops (INTR-FF) setzt. An der ersten Schaltung, auf die das INTA-Lesesignal von der CPU geht, muss die Kennung CD eingestellt werden. Die zweite und die dritte Schaltung liefern der CPU den Adressvektor.

Bild 13 Erweiterung der Interrupt-Vektoren über die Kennung CD

Ablauf-Beschreibung beim Eintreffen einer Interrupt-Anforderung:

- Das Eintreffen einer Interrupt-Anforderung setzt alle drei INTR-FF.

- Nach der Annahme des Interrupt sendet die CPU das INTA-Lese-Signal und liest in der Prioritätenkette die erste Kennung CD (CALL). Hierdurch wird das INTR-FFa der Schaltung A gelöscht.

- Mit dem zweiten INTA-Signal liest die CPU die an der zweiten Schaltung eingestellte Kennung – in diesem Fall das Low-Byte des benötigten Adressvektors (INTR-FFb wird gelöscht).

- Durch das dritte INTA-Signal wird von der CPU die an der dritten Schaltung eingestellte Kennung gelesen – das High-Byte des benötigten Adressvektors (INTR-FFc wird gelöscht).

- Die CPU speichert die Rückkehradresse auf dem Stack und setzt ihre Arbeit an der gelesenen Adresse fort. Die zur Interrupt-Anforderung gehörende Interrupt-Service Routine wird ausgeführt.

Aufgabe: Erstellen Sie sich eine Funktionstabelle mit den möglichen Adressvektoren, die sich mit den 4 DIL-Schaltern auf der Vektor-Interrupt-Baugruppe einstellen lassen – die Kombination CD (Kennung) ist kein Adressvektor.

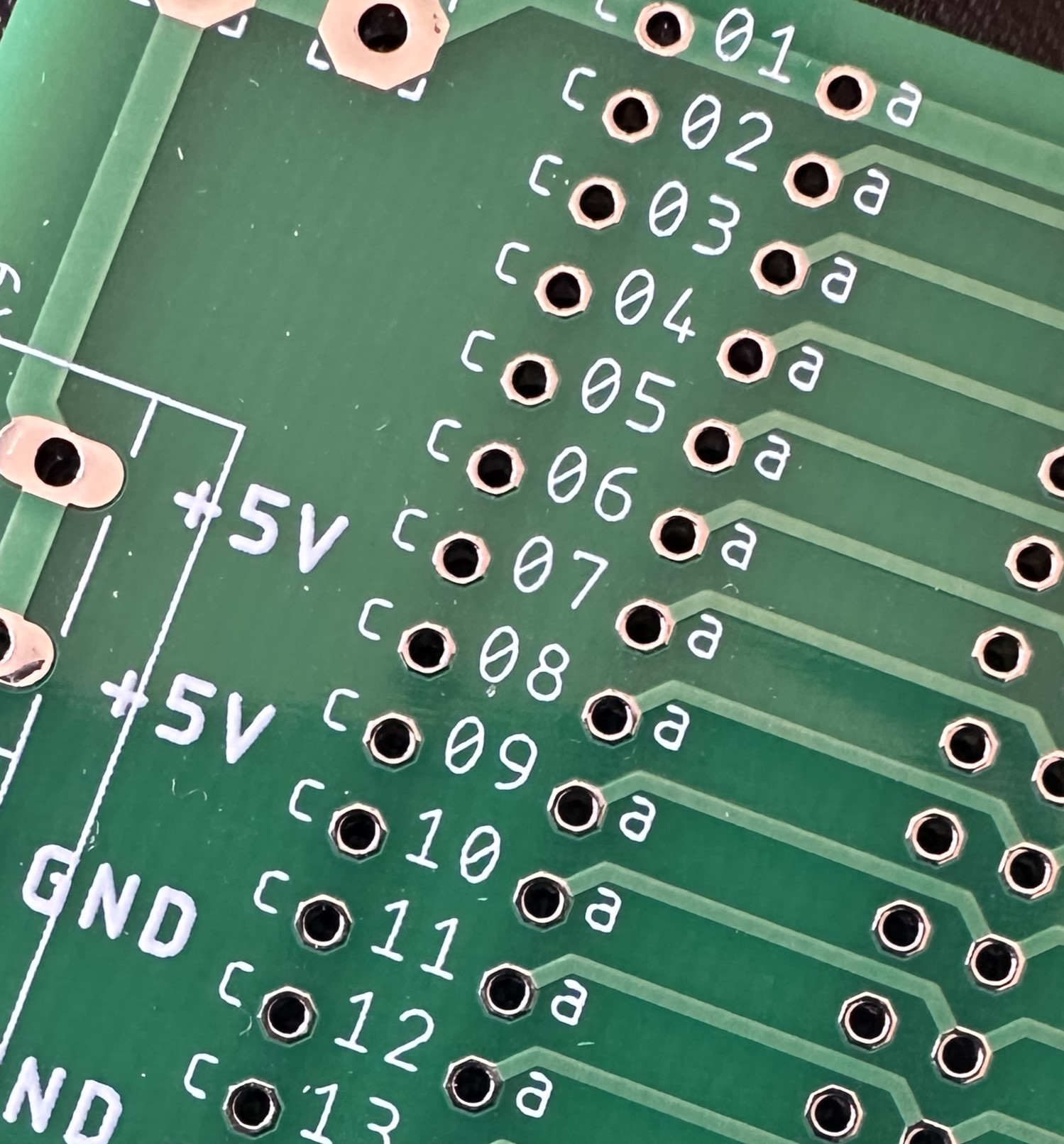

Bus-Aufsteckplatine (Schmitt-Trigger)

Diese Bus-Aufsteckplatine muß bei der Verwendung der Vektor-Interrupt-Baugruppe auf der Rückwand der Busplatine aufgesteckt sein; ebenso die Bus-Abschlußplatine.

Auf der Bus-Aufsteckplatine befinden sich ..

- der pull-up-Widerstand mit nachfolgendem Inverter für die INTR-Leitung (Vektor-Interrupt),

- eine Impulsformerstufe für die 100 Hz-Impulse vom Netzteil (liefert Impulse bei jedem Nulldurchgang der Netzspannung, siehe auch Fachtheoretische Übungen Kap. 7.2, S.146 – die beiden dort angegebenen CMOS-NAND-Gatter mit Schmitt-Triggereingang befinden sich auf dieser Aufsteckplatine und dürfen dann nicht mehr in der Baugruppe „Spannungsregelung“ nachgerüstet sein) und

- ein Steckbrückensockel, über den die geformten 100 Hz-Impulse den verschiedenen Interrupt-Eingängen zugeführt werden können. Hier ist ein freier Steckbrückenplatz, der die Impulse auf eine freie Busleitung (30a) führt, dort stehen sie über die Adapterkarte für andere Anwendungen zur Verfügung.

ACHTUNG:

Bei Änderung der Steckbrücke von dem freien Platz auf einen Interrupt-Eingang ist immer darauf zu

achten, dass dieser Interrupt-Eingang noch nicht anderweitig genutzt wird !

Bild 14 Schaltbild Bus-Aufsteckplatine

Anwendungsbeispiel 1: START-/STOP-UHR

Die beiden folgenden Anwendungsbeispiele sind einfach aufgebaut, so dass der Lernende sich mit dem Thema „Interrupt-Technik“ Vertraut machen kann. Erweiterungen sollten erfolgen, viel Spaß !

Hinweis: Vor der Durchführung dieses Anwendungsbeispiels sollte die Inbetriebnahme durchgeführt worden sein. Benutzen Sie bitte bei auftretenden Problemen den Inbetriebnahme-Teil.

;Assembler-Programm-Beispiel:

;******************************************

;* Interruptgesteuerte UHR (0 bis 59 sec)*

;******************************************

;mit START-/STOP-Funktion über eine Paralleleingabe (Bit 0)

;Ansteuerung des INTR-Eingangs mit Hilfe der Vektor-Interrupt-Baugruppe:

;Kennung: D7 (RST 2), Schalterstellungen:

;S14 S13 S12 S11

; on off on off

;Diese Kennung wird von MAT 85 bzw. vom Software-Paket SP1

;nicht genutzt

;Autor: E. Matl, 4/90, Berufsfoerderungszentrum Essen

IS2ADR EQU 0FC8C ;Sprungtabelle im RAM

PEING EQU 06 ;ADR Paralleleingabe, START/STOP

PAUSG EQU 07 ;ADR Parallelausgabe, Sekundenanzeige

IMASKE EQU 1F ;0001 1111, Maske für die

;nicht benoetigten Interrupteingänge

;

; Initialisierung

;

MVI A,0C3 ;Sprung zur ISR2-Routine:

STA IS2ADR

LXI H,SECISR ;*SEKUNDEN-UHR*

SHLD IS2ADR+1 ;vorbelegen

MVI A,IMASKE ;alle Interrupte bis auf

SIM ;INTR sperren

;

; Hauptprogramm

;

NEU: LXI H,UHR ;UHR: loeschen

XRA A ;1/100 Sekunden

MOV M,A ;auf Null

INX H ;Sekunden

MOV M,A ;auf Null

START: IN PEING ;START/STOP - Bit:

RAR ;Bit 0 = 1 ?

JNC START ;nein, warten auf START

EI ;ja, START

ANZEIG: LXI H,UHR+1 ;ADR Sekunden laden

MOV A,M ;Sekunden holen

OUT PAUSG ;und anzeigen

STOP: IN PE ING ;warten auf

RAR ;STOP

JC ANZEIG ;nein--> ANZEIG: Uhr läuft

DI ;ja, Interrupt sperren

JMP NEU ;neuer Start: Uhr steht

;

; Interrupt-Service-Routine:

; SEKUNDEN-UHR

;

SECISR: PUSH H ;die im Hauptprogramm verwendeten

PUSH PSW ;Registerinhalte retten

HSEC: LXI H,UHR ;ADR 1/100 Sekunden laden

MOV A,M ;1/100 Sekunden holen

CPI 63 ;HSEC = 63/16 = 59/10 ?

JZ HSEC0 ;ja--> HSEC0

INR M ;<HSEC> := <HSEC> + 1

JMP REGRET ;Ende

HSEC0: MVI M,0 ;1/100 Sekunden auf Null

INX H ;ADR Sekunden laden

SEC: MOV A,M ;Sekunden holen

CPI 59 ;SEC= 59/10 ?

JZ SEC0 ;ja--> SEC0

ADI 1 ;Sekunden dezimal

DAA ;zählen

MOV M,A ;und speichern

JMP REGRET ;Ende

SEC0: MVI M,0 ;Sekunden auf Null

REGRET: POP PSW ;Registerinhalte return

POP H

EI ;Interrupt wieder freigeben EI

RET ;zurueck zum unterbrochenen Programm

;

;

UHR: DB 0,0 ;Speicher: HSEC, SEC

Vor der Programmeingabe müssen die Hardware-Voraussetzungen, eine ordnungsgemäße Funktion des Programms notwendig sind, sein. Gehen Sie anhand der folgenden Stichpunkte vor:

- Haben die Ein-/Ausgabe-Baugruppen die richtigen Adressen?

- Werden die Interrupte 5.5, 6.5 und 7.5 anderweitig genutzt?

Sie haben eine höhere Priorität. Die Maske in diesem Programm kann z.B. vom Betriebsprogramm wieder umdefiniert werden. - Ist die richtige Kennung auf der Interrupt-Vektor-Baugruppe eingestellt? Sind die Kennungen nicht doppelt?

- Falls ein externer Generator für die 100 Hz-Impulse verwendet wird: “Hat er die richtige Frequenz und den richtigen Pegel (TTL)?“

- Bei Verwendung des 100Hz-Impulses vom Netzteil: Ist die Brücke an der Bus-Aufsteckplatine an der richtigen Stelle? Der 100Hz-Impuls muss auf der Busleitung 30a zu messen sein.

- Ist die 100Hz-Impulsquelle an dem richtigen Interrupteingang:

A,B,C und stimmt dieser mit der Kennung überein?

Anwendungsbeispiel 2: Drehzahlmessung

Hinweis: Vor der Durchführung dieses Anwendungsbeispiels sollte die Inbetriebnahme durchgeführt worden sein. Benutzen Sie bitte bei auftretenden Problemen den Inbetriebnahme-Teil.

;Assembler-Programm-Beispiel:

;********************************************

;* Drehzahlmessung (0 bis 99 Umdr./sec) *

;* Anzeige: BCD-Code an der Parallelausgabe*

;********************************************

;Ansteuerung des INTR-Eingangs mit Hilfe der

;Vektor-Interrupt-Baugruppe:

;Tor-Zeit: Eingang A, 100Hz --> 1 Sekunde Messzeit

;Kennung : D7 (RST 2)

;Schalterstellungen:

; S14 S13 S12 S11

; on off on off

;Umdrehungen:

;Eingang B --> Umdrehungsimpulse (1 Impuls/Umdr)

;Kennung : DF (RST 3)

;Schalterstellungen:

;S24 S23 S22 S21

; on off off off

;Beide Kennungen (Aressvektoren) werden von MAT 85 bzw. SP1

;nicht genutzt !

;Autor: E. Matl, 4/90, Berufsfoerderungszentrum Essen

IS2ADR EQU 0FC8C ;Sprungtabelle im RAM: RST 2

IS3ADR EQU 0FC8F ;Sprungtabelle im RAM: RST 2

PAUSG EQU 07 ;ADR Parallelausgabe, Cmdrehungsanzeige

IMASKE EQU 1F ;0001 1111, Maske für die

;nicht benoetigten Interrupteingänge

;

; Initialisierung

;

MVI A,0C3 ;Sprung zur

STA IS2ADR ;ISR2-Routine und zur

STA IS3ADR ;ISR3-Routine

LXI H,SECISR ;* TOR-ZEIT (1 SEKUNDE) *

SHLD IS2ADR+1 ;vorbelegen (ISR 2)

LXI H,UMDISR ;*UMDREHUNGEN*

SHLD IS3ADR+1 ;vorbelegen (ISR 3)

XRA A ;Null setzen:

STA UHR ;1/100 Sekunden

STA UMDR ;Umdrehungen pro Sekunde

OUT PAUSG ;Umdrehungsanzeige

MVI A,IMASKE ;alle Interrupte bis auf

SIM ;INTR sperren

EI ;allgemeine Interrupt-Freigabe

;

; Hauptprogramm

;

HLT ;anhalten, bis INTR eintrifft !

JMP WAIT ;nach ISR 2/3-->WAIT (Endlos-Schleife)

;hier wird nur auf einen Uhren- bzw.

;Umdrehungsimpuls gewartet

;

;Interrupt-Service-Routine: SEKUNDEN-UHR

; 1 Sekunde Torzeit für die Umdrehungsimpulse

;

SECISR: PUSH PSW ;Registerinhalte retten

HSEC: LDA UHR ;1/100 Sekunden holen

CPI 63 ;HSEC = 63/16 = 59/10 ?

JZ HSEC0 ;ja--> HSEC0

INR A ;<HSEC> := <HSEC> + 1

STA UHR ;speichern

JMP REGRET ;Ende

HSEC0: LDA UMDR ;1 sec um, Umdrehungen pro sec holen

OUT PAUSG ;und anzeigen

XRA A ;1/100 Sekunden

STA UHR ;und

STA UMDR ;Umdrehungen auf Null

REGRET: POP PSW ;Registerinhalte return

EI ;Interrupt wieder freigeben

RET ;zurueck zum unterbrochenen Programm

;

; Interrupt-Service-Routine: UMDREHUNGEN

;

UMDISR: PUSH PSW ;Registerinhalt retten

LDA UMDR ;Umdrehungen holen

ADI 01 ;und Impuls

DAA ;dezimal zählen

STA UMDR ;und speichern

POP PSW ;Registerinhalt zurück

EI ;Interrupt wieder freigeben

RET ;zurueck zum unterbrochenen Programm

UHR: DB 0 ;Speicher: HSEC

DB 0 ;UMDR: Umdrehungen pro Sekunde

Anmerkung:

Sollte kein Motor mit Impulsgeber zur Verfügung stehen, so kann als Ersatz ein Frequenzgenerator mit TTL-Ausgang genommen werden.

Vor der Programmeingabe müssen die Hardware-Voraussetzungen, eine ordnungsgemäße Funktion des Programms notwendig sind, sein. Gehen Sie anhand der folgenden Stichpunkte vor:

- Haben die Ein-/Ausgabe-Baugruppen die richtigen Adressen?

- Werden die Interrupte 5.5, 6.5 und 7.5 anderweitig genutzt?

Sie haben eine höhere Priorität. Die Maske in diesem Programm kann z.B. vom Betriebsprogramm wieder umdefiniert werden. - Ist die richtige Kennung auf der Interrupt-Vektor-Baugruppe eingestellt? Sind die Kennungen nicht doppelt?

- Falls ein externer Generator für die 100 Hz-Impulse verwendet wird: „Hat er die richtige Frequenz, den richtigen Pegel (TTL)“

- Bei Verwendung des 100Hz-Impulses vorn Netzteil: Ist die Brücke an der Bus-Aufsteckplatine an der richtigen Stelle? Der 100HzImpuls muss auf der Busleitung 30a zu messen sein.

- Ist die 100Hz-Impulsquelle an dem richtigen Interrupteingang:

A,B,C und stimmt dieser mit der Kennung überein?

Inbetriebnahme

Die Inbetriebnahme dieser Baugruppe wird hier auf zwei Ebenen durchgeführt. In der ersten Ebene wird mit einer Minimalkonfiguration des MC-Systems gearbeitet. Es ist eine überschaubare Ebene, eventuelle Nebeneffekte durch das Betriebsprogramm oder weitere Baugruppen entfallen hier. Der Lernende kann sich hier ganz auf das Problem „Interrupt-Technik“ und der dazu notwendigen Hardware konzentrieren. In der zweiten Ebene wird mit dem Betriebsprogramm gearbeitet, dieses setzt einige Kenntnisse über das Betriebsprogramm und dessen Unterstützung weiterer IQ-Baugruppen voraus. Die Nutzung von Interrupt-Eingängen (siehe Tabelle Seite 18) muss hier beachtet werden.

Inbetriebnahme Minimalkonfiguration

Für diese Inbetriebnahme benötigen wir außer der Vektor-Interrupt-Baugruppe folgende Baugruppen:

- CPU

- RAM (ab der Adresse 0000)

- Eingabe (Port-Adresse 06)

- Ausgabe (Port-Adresse 07)

- Bus-Signalgeber (zur Programm-Eingabe)

- Bus-Signalanzeige (zur Programm-Eingabe und für den Einzelschritt-Betrieb-Single-Step)

- Adapterkarte

(auf diese Karte die Vektor-Interrupt-Baugruppe aufstecken; für Handbetrieb bzw. Messungen) - Bus-Aufsteckplatine mit dem Widerstand für den offenen Kollektor-Ausgang: INTR und dem notwendigen Inverter.

Voreinstellungen an der Vektor-Interrupt-Baugruppe:

- Stecken Sie die Steckbrücke auf CON5 in die Stellung: 1. Baugruppe.

- Die Steckbrücken der Schaltung A (CON2), der Schaltung B (CON3) und der Schaltung C (CON4) sind in die Stellung „Hand-Betrieb“ zu stecken.

- Die drei Steckbrücken an der Frontplatte CON6, CON7 und CON8 für die Eingänge mit negativer Flankenansteuerung sind anstatt auf die Eingänge auf Masse zu stecken.

Stellen Sie die drei folgenden Kennungen ein:

| Schaltung | A | Schaltung A hat die höchste Priorität |

| Kennung | C7 | |

| Datenleitung | D5 on D4 on D3 on D1 off | |

| Schaltung | B | Schaltung A hat die nächsthöchere Priorität |

| Kennung | CF | |

| Datenleitung | D5 on D4 on D3 off D1 off | |

| Schaltung | C | Schaltung A hat die niedrigste Priorität |

| Kennung | D7 | |

| Datenleitung | D5 on D4 off D3 on D1 off |

Sind alle oben angegebenen Vorarbeiten/ Einstellungen durchgeführt, so können Sie den Baugruppenträger mit den Baugruppen bestücken.

Nachdem Sie alles nochmals überprüft haben, schalten Sie die Versorgungsspannung ein und geben Sie mit dem Bus-Signalgeber das folgende Testprogramm ein.

Testprogramm 1: Minimalkonfiguration:

| INTR-Nr | Adresse | Daten | Mnemonic | Kommentar |

|---|---|---|---|---|

| RST 0 | 0 0 0 0 0 0 0 1 0 0 0 3 | AF D3 07 C3 40 00 | XRA A OUT 07 JMP 0040 | Akkuinhalt := 0 INTR-Nr 0 anzeigen Sprung zur Initialisierung |

| RST 1 | 0 0 0 8 0 0 0 A 0 0 0 C | 3E 01 D3 07 C9 | MVI A,01 OUT 07 RET | INTR-Nr 1 laden und anzeigen zurück |

| RST 2 | 0 0 1 0 0 0 1 2 0 0 1 4 : : 0 0 4 0 0 0 4 3 0 0 4 5 0 0 4 6 0 0 4 8 0 0 4 A 0 0 4 D 0 0 4 E | 3E 02 D3 07 C9 : : 31 00 20 3E 1F 30 DB 06 E6 01 CA 46 00 FB C3 46 00 | MVI A,02 OUT 07 RET : : LXI SP,2000 MVI A,1F SIM IN 06 ANI 01 JZ 0046 EI JMP0046 | INTR-Nr 2 laden und anzeigen zurück Stackpointer setzen INTR RST 5.5/6.5/7.5 sperren START bei B0 = 1 B0 = 0, Karten B0 = 1, Interrupt frei START abfragen |

Stellen Sie, bevor Sie das Testprogramm starten, die Bus-Signalanzeige auf „Einzelschritt-Betrieb“ (Schalter: RUN/HLT auf HLT und Schalter: ON/OFF auf OFF; Hardware-Breakpoint aus). Danach können Sie das Programm starten, indem Sie den Bus-Signalgeber abschalten (Schalter: EIN/AUS auf AUS). Protokollieren Sie das Testprogramm im Einzelschritt-Betrieb nach dem folgenden Schema:

| STEP | ADR | DATA | MEMR | MEMW | IOW | IOR | INSTR | Kommentar |

|---|---|---|---|---|---|---|---|---|

| 0: RESET | 0000 | AF | * | * | INTR-Nr 0 | |||

| 1 | 0001 | D3 | * | * | anzeigen | |||

| 2 | 0002 | 07 | * | |||||

| 3 | 0003 | C3 | * | * | Sprung … |

Mit dem Schalter B0 an der Paralleleingabe können Sie die Interrupt-Freigabe starten. Bevor der Befehl EI (Interrupt freigeben) nicht ausgeführt Kurde, müssen auf der Vektor-Interrupt-Baugruppe von Hand

ausgelöste Interrupt-Signale ignoriert werden. Sobald der Schalter B0 an der Eingabe eingeschaltet wird, reagiert die CPU auf anstehende Interrupt-Anforderungen. Erzeugen Sie mit den Hand-Tastern (TA1, TA2 und TA3) auf der Vektor-Interrupt-Baugruppe Interrupt-Anforderungen und protokollieren Sie den Ablauf.

In einem weiteren Schritt können Sie vom Einzelschritt-Betrieb in den „RUN-Betrieb“ umschalten und die Baugruppe dynamisch testen. Je nach gedrückter Interrupt-Anforderung wird die entsprechende Interrupt-Nummer an der Ausgabe-Baugruppe angezeigt.

Nach dem vorgegebenen Testprogramm für die ersten drei Interrupt-Vektoren sollten Sie auch die noch fünf verbleibenden Interrupt-Vektoren testen. Dazu müssen auf der Vektor-Interrupt-Baugruppe die Interrupt-Kennungen entsprechend eingestellt werden und die dazu notwendigen ISR-Testroutinen unter den Zieladressen eingegeben werden.

Beispiel:

INTR-Nr 5 –> Kennung: EF –>DIL-Schalter:

| Datenleitung | D5 | D4 | D3 | D1 |

| DIL-Schalter | off | on | off | off |

ISR-Testroutine:

Zieladresse: 0028 MVI A,05 ; Interrupt 5

002A OUT 07 ; anzeigen

002C RETInterrupt-Anforderungen über die Interrupt-Eingänge

Die Steckbrücken der Schaltung A (CON2), der Schaltung B (CON3) und der Schaltung C (CON4) sind in die Stellung „AUTO“ zu stecken.

Zur Ansteuerung der Baugruppe 1, wird ein Signalgeber mit TTL-Ausgang benötigt. Wenn Sie das zuvor angegebene Testprogramm hier nutzen wollen, müssen Sie einen Signalgeber mit niedriger Ausgangsfrequenz benutzen, um die Signale an der Ausgabe-Baugruppe beobachten zu können.

Für die negativ-Flankeneingänge müssen die Steckbrücken an der Frontplatte CON6, CON7 und CON8 von „Masse“ auf die Eingangsbuchsen (linke Reihe Buchsen A bis C) gesteckt werden. In dieser Stellung

der Steckbrücken funktionieren die positiv-Flankeneingänge nur, wenn die negativ-Flankeneingänge den Pegel „Low“ einnehmen, d.h., sie müssen auf „Low-Pegel“ gelegt oder zur Ansteuerung genutzt werden .

Inbetriebnahme mit dem Betriebsprogramm MAT85

Außer den benötigten Baugruppen unter dem Inbetriebnahme-Teil „Minimalkonfiguration“ wird die ROM-Baugruppe mit dem Betriebsprogramm MAT85 ( ab Adresse 0000) für diese Inbetriebnahme benötigt, RAM-Speicher muss mindestens ab der Adresse E000 vorhanden sein, Durch die Nutzung des Betriebsprogramms MAT85 liegen nun alle Interrupt-Adressvektoren der CPU 8085 am Anfang des ROM-Bereichs von MAT85. Damit der Anwender später mit den vom Betriebsprogramm nicht genutzten Interrupten flexibel arbeiten kann, steht im ROM an den entsprechenden Adressen ein Sprung in den RAM-Bereich (siehe Tabelle Seite 18), Im RAM stehen jeweils 3 Byte für einen Sprung in die notwendige Anwender-Interrupt-Service-Routine.

Sprungliste im ROM:

| ROM-Adr | Mnemonic | Bemerkung | RST |

|---|---|---|---|

| 0000 | JMP 0149 | RESET, Sprung in den ROM-Bereich | RST 0 |

| 0008 | JMP 023F | USER-Einsprung, ROM-Bereich | RST 1 |

| 0010 | JMP FC8C | frei, Sprung in den RAM-Bereich | RST 2 |

| 0018 | JMP FC8F | frei, Sprung in den RAM-Bereich | RST 3 |

| 0020 | JMP 02DF | BREAKPOINT-Einsprung, ROM-Bereich | RST 4 |

| 0024 | JMP 0286 | Warmstart-Einsprung, ROM-Bereich | TRAP |

| 0028 | JMP FC92 | frei, Sprung in den RAM-Bereich | RST 5 |

| 002C | JMP FC95 | MINI-DOS: Floppy-Disk-Controller | RST 5.5 |

| 0030 | JMP FC98 | frei, Sprung in den RAM-Bereich | RST 6 |

| 0034 | JMP FC9B | SPS/BASIC: Abbruch über Tastatur | RST 6.5 |

| 0038 | JMP 024D | PROGRAM-ABBORT-Einsprung, ROM-Bereich | RST 7 |

| 003C | JMP FC9E | SPS-Interpreter (timer) | RST 7.5 |

Anmerkung:

Eine Beschreibung des Betriebssystems finden Sie in dem Band Fachtheoretische Übungen, Kapitel 7.1 MAT 85 und Kapitel 7.2 Software-Paket SP1.

Voreinstellungen an der Vektor-Interrupt-Baugruppe:

- Stecken Sie die Steckbrücke auf CON5 in die Stellung: 1. Baugruppe.

- Die Steckbrücken der Schaltung A (CON2), der Schaltung B (CON3) und der Schaltung C (CON4} sind in die Stellung „Hand-Betrieb“ zu stecken.

- Die drei Steckbrücken an der Frontplatte CON6, CON7 und CON8 für die Eingänge mit negativer Flankenansteuerung sind anstatt auf die Eingänge auf Masse zu stecken,

Stellen Sie die drei folgenden Kennungen ein:

| Schaltung | A | Schaltung A hat die höchste Priorität |

| Kennung | C7 | |

| Datenleitung | D5 on D4 on D3 on D1 off | |

| Schaltung | B | Schaltung A hat die nächsthöchere Priorität |

| Kennung | CF | |

| Datenleitung | D5 on D4 on D3 off D1 off | |

| Schaltung | C | Schaltung A hat die niedrigste Priorität |

| Kennung | D7 | |

| Datenleitung | D5 on D4 off D3 on D1 off |

Bevor Sie die Versorgungsspannung einschalten, überprüfen Sie bitte alle Einstellungen. Geben Sie anschließend mit Hilfe des Assemblers das folgende Testprogramm ein.

Testprogramm 2 unter MAT 85:

| INTR-Nr | Adresse | Daten | Mnemonic | Kommentar |

|---|---|---|---|---|

| RST 0 | 0 0 0 0 | C3 49 01 | JMP 0149 | Sprung nach 149, RESET |

| RST 1 | 0 0 0 8 | C3 3F 02 | JMP 023F | Sprung nach 23F, USER |

| RST 2 | 0 0 1 0 | C3 8C FC | JMP FC8C | Sprung nach FC8C, RAM |

| START: | E000 E002 E003 E004 E006 E007 E008 : | 3E 1F 30 AF D3 07 FB 76 C3 07 E0 : | MVI A,1F SIM XRA A OUT 07 EI HLT JMP E007 : | INTR RST 5.5/6.5/7.5 individuell sperren Akku := 0 anzeigen Interrupt allgemein freigeben und HALT-Zustand Endlos-Schleife (verlassen nur durch RESET- oder Interrupt-Signal möglich |

| ISR2: | E010 E011 E013 E014 : : FC8C | 3C D3 07 FB C9 : : C3 10 E0 | INR A OUT 07 EI RET : : JMP E010 | lnterrupte zählen anzeigen Interrupt freigeben zurück Sprungleiste zur Anwender- ISR2 |

Wenn Sie das Testprogramm2 gestartet haben, werden die lnterrupt-Signale der Schaltung C ( niedrigste Priorität) gezählt und an der Ausgabe-Baugruppe angezeigt. Bei Auslösung der anderen beiden Vektor-Interrupt-Signale kann die Endlos-Schleife mit einer Rückkehr in das Betriebsprogramm verlassen werden.

Schaltung B: Rückkehr in das Betriebsprogramm mit Meldung: USER

Schaltung A: Rückkehr in das Betriebsprogramm mit MeJdung: *RESET*

(höchste Priorität)

Dieses kleine Testprogramm für die Vektor-Interrupt-Baugruppe zeigt einmal die Nutzung eines freien Interrupt-Adressvektors ( RST ) und als zweites Beispiel die Nutzung von Betriebssystem-Adressvektoren.

Aufgabe: Testen Sie in gleicher Weise die restlichen 5 Interrupt-Adressvektoren.

Hinweis:

Unter dem RST 4 -Adressvektor erfolgt die Meldung: BREAKPOINT-ERROR mit einer Ausgabe der aktuellen CPU-Registerinhalte. Dieses kann zu Programmtests genutzt werden, wobei durch ein externes Ereignis eine Triggerung bzw. Programm-Terminierung mit einer aktuellen Protokollierung erreicht werden kann.

Inbetriebnahme mit den erweiterten Adressvektoren

Wie in dem Kapitel Erweiterung der Adressvektoren beschrieben, müssen die Interrupteingänge A bis C untereinander verbunden und von einer Interrupt-Quelle angesteuert werden. Dadurch wird in allen drei Schaltungen das Interrupt-Flipflop gesetzt. Die CPU liest bei eingestellter Kennung „CD“ an der Schaltung A diese Kennung sowie die nächsten beiden Adressvektoren und löscht die entsprechenden Interrupt-Anforderungen.

Durch diese Maßnahme steht nur noch ein Interrupteingang zur Verfügung (Nachteil); es ergeben sich weitere Adressvektoren (Vorteil, siehe Anhang A8).

Stellen Sie die folgenden Kennungen ein:

Schaltung A: Kennung : CD –> Schalterstellungen

| S14 | S13 | S12 | S11 |

| on | on | off | on |

Schaltung B: Kennung : CF –> Schalterstellungen

| S24 | S23 | S22 | S21 |

| on | on | off | off |

Schaltung C: Kennung : D7 –> Schalterstellungen

| S34 | S33 | S32 | S31 |

| on | off | on | off |

Testprogramm 2 unter MAT 85:

| INTR-Nr | Adresse | Daten | Mnemonic | Kommentar |

|---|---|---|---|---|

| START: | E000 E002 E003 E004 E006 E007 E008 : | 3E 1F 30 AF D3 07 FB 76 C3 07 E0 : | MVI A,1F SIM XRA A OUT 07 EI HLT JMP E007 : | INTR RST 5.5/6.5/7.5 individuell sperren Akku := 0 anzeigen Interrupt allgemein freigeben und HALT-Zustand Endlos-Schleife (verlassen nur durch RESET- oder Interrupt-Signal möglich |

| ISRCALL: | D7CF D7D0 D7D1 D7D2 | 3C D3 07 FB C9 | INR A OUT 07 EI RET | lnterrupte zählen anzeigen Interrupt freigeben zurück |

Wenn Sie das Testprogramm 3 gestartet haben, werden die Interrupt-Signale an den untereinander verbundenen Eingängen gezählt und an der Ausgabe-Baugruppe angezeigt. Auf diese Weise lässt sich die richtige Funktion der gesamten Interrupt-Logik des MC-Systems testen. Die Frequenz des eintreffenden Interrupt-Signals sollte nicht zu hoch sein, so dass die richtige Zählung an der Ausgabe verfolgt werden kann. Ist ein Zweikanal-Oszilloskop vorhanden, kann die Eingangs- und Ausgangsfrequenz verglichen werden.

Hinweis: Die Frequenz an B0 der Ausgabe hat die halbe Frequenz des Interruptsignals – positive Flanke löst den Interrupt aus.

Interrupt-Adresstabelle

| Anschluss Signal | Priorität | Zieladresse | Auslösung durch | |

|---|---|---|---|---|

| RST 0 (C7) | freigegeben durch EI-Befehl | 5 | 0000 | H-Pegel bis zur Annahme |

| RST 1 (CF) | freigegeben durch EI-Befehl | 5 | 0008 | H-Pegel bis zur Annahme |

| RST 2 (D7) | freigegeben durch EI-Befehl | 5 | 0010 | H-Pegel bis zur Annahme |

| RST 3 (DF) | freigegeben durch EI-Befehl | 5 | 0018 | H-Pegel bis zur Annahme |

| RST 4 (E7) | freigegeben durch EI-Befehl | 5 | 0020 | H-Pegel bis zur Annahme |

| RST 5 (EF) | freigegeben durch EI-Befehl | 5 | 0028 | H-Pegel bis zur Annahme |

| RST 6 (F7) | freigegeben durch EI-Befehl | 5 | 0030 | H-Pegel bis zur Annahme |

| RST 7 (FF) | freigegeben durch EI-Befehl | 5 | 0038 | H-Pegel bis zur Annahme |

| RST 5.5 | maskierbar durch SIM-Befehl | 4 | 002C | H-Pegel bis zur Annahme |

| RST 6.5 | maskierbar durch SIM-Befehl | 3 | 0034 | H-Pegel bis zur Annahme |

| RST 7.5 | maskierbar durch SIM-Befehl | 2 | 003C | L-H-Flanke Anforderung wird bis zur Annahme gespeichert |

| TRAP (RST 4.5 | nicht maskierbar | 1 | 0024 | L-H-Flanke und H-Pegel bis zur Annahme |

Interrupt-Masken-Register

I-Register – Schreiben

| BIT | Register | Bedeutung |

|---|---|---|

| 7 | SOD | SOD-Ausgang der CPU |

| 6 | SOD EN | Freigabe: H |

| 5 | X | nicht verwendet |

| 4 | RES 7.5 | Rücksetzen des RST 7.5-Flip-Flops durch H-Pegel |

| 3 | MSE | Maske L: wird ignoriert H: wird gesetzt |

| 2 | M 7.5 | Unterbrechungsmaske: L: Interrupt erlaubt H: Interrupt gesperrt |

| 1 | M 6.5 | Unterbrechungsmaske: L: Interrupt erlaubt H: Interrupt gesperrt |

| 0 | M 5.5 | Unterbrechungsmaske: L: Interrupt erlaubt H: Interrupt gesperrt |

I-Register – Lesen

| BIT | Register | Bedeutung |

|---|---|---|

| 7 | SID | Pegel am Eingang SID der CPU |

| 6 | I 7.5 | Flags für anstehende Unterbrechungen |

| 5 | I 6.5 | Flags für anstehende Unterbrechungen |

| 4 | I 5.5 | Flags für anstehende Unterbrechungen |

| 3 | IE | Unterbrechungs-Freigabe-Bit H: Maske ist freigegeben |

| 2 | M 7.5 | Aktuelle Unterbrechungsmaske: L: Interrupt erlaubt H: Interrupt gesperrt |

| 1 | M 6.5 | Aktuelle Unterbrechungsmaske: L: Interrupt erlaubt H: Interrupt gesperrt |

| 0 | M 5.5 | Aktuelle Unterbrechungsmaske: L: Interrupt erlaubt H: Interrupt gesperrt |

Adressvektoren incl, Erweiterung für den Interrupt INTR

| SX D5 | SX D4 | SX D3 | SX D1 | Kennung Datenbus | Zieladresse Adressvektor |

|---|---|---|---|---|---|

| on | on | on | on | C5 | ( C5 ) |

| on | on | on | off | C7 | 0000 |

| on | on | off | on | CD | CALL |

| on | on | off | off | CF | 0008 |

| on | off | on | on | D5 | D5 |

| on | off | on | off | D7 | 0010 |

| on | off | off | on | DD | DD |

| on | off | off | off | DF | 0018 |

| off | on | on | on | E5 | E5 |

| off | on | on | off | E7 | 0020 |

| off | on | off | on | ED | ED |

| off | on | off | off | EF | 0028 |

| off | off | on | on | F5 | F5 |

| off | off | on | off | F7 | 0030 |

| off | off | off | on | FD | FD |

| off | off | off | off | FF | 0038 |

SX: DIL-Schalter S1 bis S3 (Schaltung Abis C)

Anmerkung:

Diese Tabelle ist eine Erweiterung der Adressvektor-Tabelle von Seite 20 der Funktionsbeschreibung. Für die Erweiterung werden alle drei Vektor-Interrupt-Schaltungen (A, B und C) auf der Baugruppe benötigt.

An der Schaltung A muss dann die Kennung „CD“ (CALL) eingestellt werden. Die Schaltungen B und C liefern dann das Low- bzw. High Byte des notwendigen Adressvektors ( Zieladresse in Klammern ) für die Kennung „CD“.

Beispiel:

| Schaltung A | Schaltung B | Schaltung C |

|---|---|---|

| CD | CF | D7 |

ergibt: CALL D7CF

Hinweise zur Inbetriebnahme

Nützliche Hinweise zum Betrieb und zur Erweiterung (2. Baugruppe)

Hier soll nun eine kurze Zusammenfassung von Hinweisen erfolgen – sozusagen eine Checkliste.

Denken Sie daran, dass das Interruptsystem Ihres Mikrocomputers unter Umständen noch nie genutzt wurde – verdeckte Fehler sind möglich. Eine einfache und überschaubare Inbetriebnahme ist auf jeden Fall für den Einstieg und für eine m6gliche Fehlersuche von Vorteil. Anderweitige Nutzung des Interruptsystems wird dabei ausgeschlossen.

Zum Betrieb der Vektor-Interrupt-Baugruppe ist die Bus-Aufsteckplatine erforderlich, sie liefert für den “offenen Kollektorausgang“ der Interruptleitung den notwendigen „pull-up-Widerstand“ und stellt die Verbindung zur Bus-INTR-Leitung über einen Inverter her.

Der netzsynchrone 100 Hz-Impuls kann nur eine TTL-Last treiben. Bei einer Nutzung in Zusammenhang mit der Erweiterung der Adressvektoren (Ansteuerung der drei untereinander verbundenen Interrupteingänge) muss ein Treiber-IC zwischengeschaltet werden.

Werden zwei Vektor-Interrupt-Baugruppen zusammengeschaltet -Erweiterung der „daisy-chain-Ketten auf 6 Interruptquellen-, so muss eine Baugruppe über die Steckbrücke CON5 auf Baugruppe 1 und die zweite Baugruppe muss über die Steckbrücke CON5 auf Baugruppe 2 eingestellt sein. Die auf Baugruppe 1 eingestellte Vektor-Interrupt-Baugruppe liegt dann in der Prioritätenkette vor der Baugruppe 2.

Die beiden Baugruppen sollten nebeneinander gesteckt sein, da das INTA-Lesesignal extern verbunden werden muss:

Baugruppe 1: INTA-Übertrag AUS verbunden mit

Baugruppe 2: INTA-Übertrag EIN

Bevor Sie ein Beispiel aus dieser Beschreibung ausprobieren, überprüfen Sie bitte folgende Punkte:

- Sind die Kennungen richtig eingestellt?

- Kommen keine Kennungen doppelt vor?

- Haben die Steckbrücken CON2, CON3 und CON4 (HAND/AUTO) die richtige Position?

- Falls Sie lnterrupte über die Interrupteingänge A, Bund C auslösen, so müssen die Steckbrücken CON2, CON3 und CON4 auf “AUTO“ gesteckt sein.

- Haben die Interruptsignale die richtigen Pegel und eine entsprechende Flankensteilheit?

- Pegel lassen sich gut im „Hand-Betrieb“ der Vektor-Interrupt-Baugruppe im Zusammenspiel mit dem „single-step-Betrieb“ des MC-Systems überprüfen.

- Ist die Bus-Aufsteckplatine auf den Bus gesteckt?

- Erstellen Sie sich zusätzlich zu einem Programmablaufplan (Flussdiagramm)

Ihres Programms einen Interruptplan mit den verwendeten Interrupten, Kennungen, Adressvektoren.

Prioritäten und die zeitliche Abfolge der Ansteuerung müssen stimmen und in den Plan aufgenommen werden.

Wichtige Hinweise für die Benutzer der MAT 32 K TerminalVersion

Durch die Anpassung des MAT85 Betriebsprogramm an die Terminalversion hat sich die Sprungliste im ROM verändert. Entgegen der Beschreibung auf S. 33 ergibt sich für den Anwender der Terminalversion

folgende Sprungliste:

Sprungliste im ROM:

| ROM-Adr | Mnemonic | Bemerkung | RST |

|---|---|---|---|

| 0000 | JMP 0149 | RESET, Sprung in den ROM-Bereich | RST 0 |

| 0008 | JMP 023F | USER-Einsprung, ROM-Bereich | RST 1 |

| 0010 | CALL 082D | Serielle Eingabe, ROM-Bereich | RST 2 |

| 0018 | JMP 0877 | Sprung im ROM-Bereich | RST 3 |

| 0020 | JMP 02DF | BREAKPOINT-Einsprung, ROM-Bereich | RST 4 |

| 0024 | JMP FC8C | Sprung in den RAM-Bereich | TRAP |

| 0028 | JMP FC92 | frei, Sprung in den RAM-Bereich | RST 5 |

| 002C | JMP FC95 | MINI-DOS: Floppy-Disk-Controller | RST 5.5 |

| 0030 | JMP FC98 | frei, Sprung in den RAM-Bereich | RST 6 |

| 0034 | JMP FC9B | SPS/BASIC: Abbruch über Tastatur | RST 6.5 |

| 0038 | JMP 024D | PROGRAM-ABBORT-Einsprung, ROM-Bereich | RST 7 |

| 003C | JMP FC9E | SPS-Interpreter (Timer) | RST 7.5 |

Ein Vergleich der Sprunglisten zeigt, dass sowohl RST 2 als auch RST 3 für den Anwender der Terminalversion nicht nutzbar ist. Bei der Durchführung der Anwendungsbeispiele 1 und 2 sowie vom Testprogramm 2 müssen daher andere Vektoren als vorgegeben eingestellt werden (RST 5 und/oder RST 6).

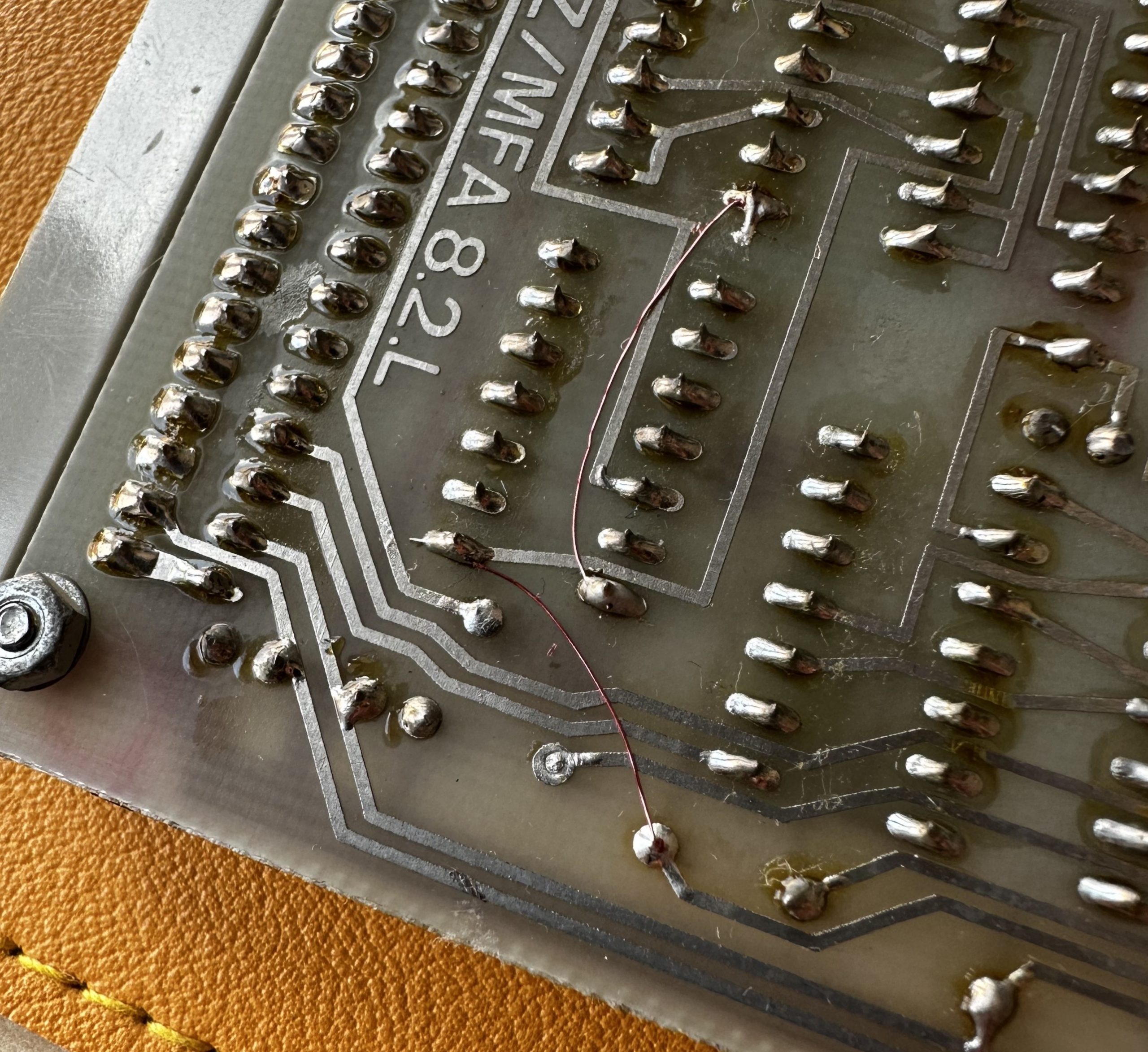

Stromlaufplan – Interrupt-Vektor-Karte

Bestückungsplan

Leiterplatte

Stromlaufplan CPU-Baugruppe

BUS Aufsteckplatine