Von den 256 möglichen lnstruktionscodes· im Mikroprozessor 8080 sind zwölf unbesetzt und funktionieren als NOPs (NOP =no operation). Beim Typ 8085 werden zwei davon für die Behandlung der Interruptmaske verwendet (RIM und SIM). Die verbleibenden zehn Codes sind „neue Instruktionen“, die der Hersteller bislang nicht bekanntgegeben hat. Außerdem sind zwei neue Zustandsbits vorhanden: überlauf mit und ohne Vorzeichen. Tests liefen auf den Versionen 8085 sowie 8085A und zeigten keine Abweichungen gegenüber der vorliegenden Beschreibung. Sieben der zehn neuen Befehle führen 16-bit-Operationen aus, die restlichen drei werten die neuen Zustandsbits aus. Die mnemotechnischen Codes der neuen Instruktionen sind im Einklang mit den bestehenden Codes gewählt (siehe Tabelle).

Einige Merkmale der neuen Instruktionen

DSUB

DSUB ist eine 16-bit-Subtraktion komplementär zu DAD B; das BC-Doppelregister wird vom HL-Doppelregister subtrahiert.

RDEL

RDEL ähnelt RAL erweitert auf 16 bit, hier in Form des DE-Doppelregisters, welches um ein Bit nach links rotiert wird.

ARHL

Ohne Vorgänger im 8080 ist ARHL: HL-Doppelregister arithmetisch nach rechts schieben, d . h. rechts schieben unter Beibehaltung des höchstwertigen Bits.

SHLX/LHLX

Bekannt sind STAX D und LDAX D, die den 8-bitWert im A-Register indirekt durch die Adresse im DE-Doppelregister speichern oder laden; die neuen Befehle SHLX und LHLX speichern und laden den 16-bit-Wert im HL-Doppelregister indirekt durch DE.

LDHI

LDHI -> LDHI macht Index-Adressierung über 256-Byte (,,Page“ -)Grenzen hinweg möglich, während LDSI -> LDSI sich für Stack-Manipulationen in Systemroutinen eignet.

Die verbleibenden drei neuen Instruktionen sind:

- RSTV

- JX5

- JNX5.

RSTV

RSTV wirkt wie ein Restart-Befehl zur Adresse 40h, wenn V gesetzt ist, sonst wie ein NOP.

JX5/JNX5

JX5 und JNX5 reagieren auf das X5-Bit genau wie JC und JNC auf das Carry-Bit, sie sind also bedingte Sprungbefehle.

Ähnlich ist RSTV als ein bedingter Restart-Befehl zu bezeichnen. Von den zwei neuen Zustandsbits V und X5 ist V das normale Zweierkomplement-Überlaufbit wie auch bei anderen Prozessoren. X5 entspricht keinem Standard-Zustandsbit bei sonstigen Prozessoren und ist deshalb nach seiner Position im Zustandsregister benannt, nicht nach seiner Funktion. Bei INX und DCX kann X5 als Überlaufindikator für Zahlen ohne Vorzeichen Verwendung finden, und zwar beim Übergang von FFFF auf 0000 (INX) bzw. von 0000 auf FFFF (DCX). Der Einsatz der neuen Instruktionen bei Maschinensprache-Programmen erfolgt genau wie bei den alten Befehlen. In Assembler-Programmen hingegen setzt man am besten Makros ein, die den Instruktionscode und eventuelle Argumente als „Datenbytes“ absetzen. Dann können die neuen Befehle wie die alten geschrieben werden.

Codebeispiel

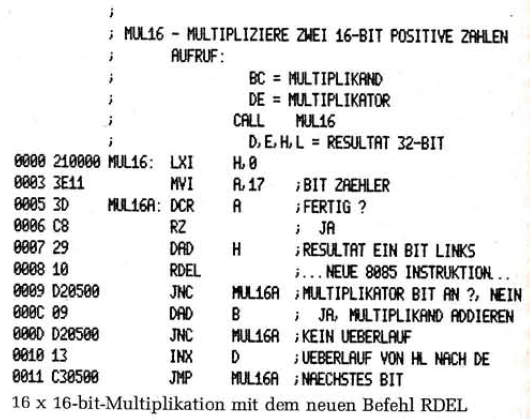

16×16-Bit Multiplikation mit dem neuen 8085-Befehl RDEL:

; MUL16 - Multipliziere zwei 16-Bit Positive Zahlen

; Aufruf:

; BC = Multiplikand

; DE = Multiplikator

;

; CALL MUL16

; D,E,H,L = Resultat 32-Bit

;

0000 21 00 00 MUL16: LXI H,0 ;

0003 3E 11 MVI A,17 ; Bit-Zaehler

0005 3D MUL16A: DCR A ; Fertig ?

0006 C8 RZ ; Ja

0007 29 DAD H ; Resultat ein Bit links

0008 10 RDEL ; neue 8085-Instruktion

0008 ; Rotiere DE links durch Carry

0009 D2 05 00 JNC MUL16A ; Multiplikator Bit an ? (nein)

000C 09 DAD B ; Ja, Multiplikant addieren

000D D2 85 00 JNC MUL16A ; kein Ueberlauf

0010 13 INX D ; Ueberlauf von HL nach DE

0011 C3 05 00 JMP MUL16A ; Naechstes Bit

Die neuen Instruktionen sind besonders für arithmetische Routinen vorteilhaft. 16-durch-16-bit-Division wird doppelt so schnell unter Ausnützung von RDEL und DSUB (368 μs im Mittel); ebenso Multiplikation (278 μs im Mittel, Bild). Der 8085-Prozessor ist somit bei dieser Anwendung konkurrenzfähig mit 16-bit-Minirechnern ohne festverdrahtete Arithmetik.

In der Tabelle sind die Befehle zusammengestellt:

| Mnemonic | Op-Code | Takt- Zyklen | Verwendete Zustandsbits | Beschreibung |

|---|---|---|---|---|

| DSUB | 08 | 10 | CY, S, X5 AC, Z, V, P | Doppelsubtraktion HL = HL – BC |

| ARHL | 10 | 7 | CY | Schiebe HL arithmetisch ein Bit rechts ins Carry (oberes Bit in H wird dupliziert) |

| RDEL | 18 | 10 | CY, V | Rotiere DE links durch Carry |

| LDHI D8 | 28 | 10 | keine | Lade DE mit HL plus 8-Bit Byte DE = HL + Datenbyte |

| LDSI D8 | 38 | 10 | keine | Lade DE mit SP plus 8-bit Byte DE = SP + Datenbyte |

| RSTV | CB | 6 / 12 | keine | Restart bei Überlauf RST zu 40 wenn V = 1 |

| SHLX | D9 | 10 | keine | Speichere HL indirekt über DE |

| JNX5 ADR | DD | 7 / 10 | keine | Springe, wenn X5-Bit nicht gesetzt |

| LHLX | ED | 10 | keine | Lade HL indirekt über DE |

| JX5 ADR | FD | 7 / 10 | keine | Springe, wenn X5-Bit gesetzt |

Zustandsregister mit den neuen Bits X5 und V (Überlauf):

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| S | Z | X5 | AC | 0 | P | V | C |

Quelle: ELEKTRONIK, Heft 15, 1978, W. Dehnhordt, V . M. Sorensen