Einleitung

Für viele Anwendungen in der Steuerungstechnik ist die Einhaltung von Verzögerungen zwischen zwei Ereignissen notwendig. Das 4fach-Zeitwerk dient dazu, vier Ausgangssignale zu erzeugen, die nach Ansteuerung durch entsprechende Eingangssignale zeitverzögert auftreten. Die Verzögerungszeiten zwischen Eingangs- und Ausgangs-Signalen können mit Trimm-Potentiometern in weiten Bereichen eingestellt werden. Außerdem wird durch LEDs angezeigt, in welchem Zustand sich die Ein- und Ausgänge der Zeitstufen befinden.

Das Zeitwerk besteht aus der programmierbaren Parallelschnittstelle und zusätzlichen Zeitstufen mit Anzeigen. Hierdurch wird es möglich, die Wirkungsweise des Schnittstellenbausteins anhand eines weiteren konkreten Anwendungsbeispiels kennenzulernen.

Ein Einsatzgebiet der Baugruppe besteht z.B. darin, sie als Zeitgeber- und AnzeigeFunktionsgruppe

innerhalb einer sogen. Speicherprogrammierbaren Steuerung (SPS) einzusetzen; vgl. Kapitel 3.

Blockschaltbild und Arbeitsweise des Zeitwerks

Bild 30 zeigt das Blockschaltbild der Baugruppe. Sie besteht aus den Schaltungsteilen Adressvergleicher, programmierbare Parallelschnittstelle und Zeitwerke mit Anzeigen. Zunächst wird die Wirkungsweise der Baugruppe anhand dieses Blockschaltbildes erklärt.

Die programmierbare Parallelschnittstelle enthält – wie eingangs dieses Kapitels 6.1 erklärt – drei Datenkanäle, die durch Laden eines Steuerwortes in die interne Steuerlogik als Eingabe- oder als Ausgabe-Ports programmiert werden können. Für den hier vorgesehenen Anwendungsfall wird Kanal A als Ausgabeport und Kanal B als Eingabeport programmiert.

Die Adresse der Steuerlogik und die Portadressen sind durch den schaltungstechnischen Aufbau (Hardware) bestimmt. Der Adressvergleicher gibt den Schnittstellenbaustein nur dann für den Datenaustausch mit dem Mikroprozessor frei, wenn auf dem Adress-Bus eine gültige Adresse für eines der drei Ports oder die Steuerlogik ausgegeben wird.

Bild 30: Das Blockschaltbild des 4fach-Zeitwerks

Über die Ausgabeleitungen PA3 bis PA3 des Ports A wird der Block »Zeitwerke mit Anzeigen« angesteuert. Er enthält vier voneinander unabhängige einstellbare Verzögerungsglieder (Zeitwerke), jeweils mit dazugehöriger Anzeige für das Start-Signal (UE = H) und der Anzeige, dass die Verzögerungszeit abgelaufen ist (UA = L).

Die Ausgangssignale der Verzögerungsglieder werden dem Eingabeport B über die Leitungen PB0 bis PB3 zugeführt und können durch Abfrage dieses Ports vom Prozessor gelesen werden.

Bild 31 : Der Stromlaufplan des 4fach-Zeitwerks.

Die programmierbare Parallelschnittstelle und der Adressvergleicher

Es wird der Schnittstellenbaustein 8255 verwendet. Bild 32 zeigt ein vereinfachtes Innenschaltbild dieses Bausteins, die zu seinem Betrieb notwendigen Verbindungen zum System-Bus und den Anschluss des Adressvergleichers.

Bild 32: Der Anschluss des Schnittstellenbausteins 8255 und des Adressvergleichers

Grundsätzlich können die Datenkanäle A, B und C als Eingabe- oder als Ausgabe-Ports programmiert werden. Je nach gewünschter Betriebsart ist zur Programmierung ein vom Bausteinhersteller vorgeschriebenes Steuerwort in das Steuerwort-Register zu laden, das sich in der Lese/Schreib- und Steuer-Logik des Bausteins befindet. Dieses Laden des Steuerwortes nennt man Initialisieren des Bausteins (initial = am Anfang stehend). Um die in Bild 32 dargestellte Funktion des Bausteins zu erhalten, muß das Steuerwort 82H verwendet werden; zur Bildung der Steuerworte siehe Seite 360ff.

Das Einschreiben des Steuerwortes in das Steuerwort-Register erfolgt grundsätzlich genauso wie die Übergabe eines Datenwortes an ein Ausgabeport: Man gibt zuerst die Port-Adresse auf dem Adreß-Bus aus und stellt dann das Steuerwort auf dem Daten-Bus bereit. Mit dem Steuersignal IOW wird anschließend die Übernahme des Steuerwortes in das adressierte Register ausgelöst.

Die Tabelle in Bild 33 zeigt, welche Signalpegel an den Leitungen A0, A1 und CS zur Erzielung der gewünschten Funktionen für unseren Anwendungsfall benötigt werden.

Das Einschreiben des Steuerwortes in das Steuerwort-Register erfolgt grundsätzlich genauso wie die Übergabe eines Datenwortes an ein Ausgabeport: Man gibt zuerst die Port-Adresse auf dem Adress-Bus aus und stellt dann das Steuerwort auf dem Daten-Bus bereit. Mit dem Steuersignal IOW wird anschließend die Übernahme des Steuerwortes in das adressierte Register ausgelöst.

Die Tabelle in Bild 33 zeigt, welche Signalpegel an den Leitungen A0, A1 und CS zur Erzielung der gewünschten Funktionen für unseren Anwendungsfall benötigt werden.

Bild 33: Die Signalpegel an den Adress- und Steuer-Leitungen des Bausteins 8255, abhängig von den

Bausteinfunktionen. X bedeutet, daß die Pegel der damit bezeichneten Leitungen für die Funktion bedeutungslos sind.

Ein Datentransport zwischen Daten-Bus und Baustein ist nur möglich, wenn der CS-Eingang (Chip-Select = Bausteinauswahl) L-Pegel führt. Das Signal an diesem Eingang, das Bausteinfreigabe-Signal, kommt vom Adressvergleicher und wird durch IC2.1 invertiert, weil der Adressvergleicher an seinem Ausgang »OUT« H-Pegel abgibt.

Dieser H-Pegel tritt jedoch nur auf, wenn die Signalkombination auf den Adressleitungen A4 bis A7 gleich derjenigen Signalkombination ist, die mit den Schaltern S1 bis S4 eingestellt ist. Mit der in Bild 32 dargestellten Schaltereinstellung und den aus Bild 33 entnommenen Pegeln für die Adressleitungen A0 und A1 ergeben sich nun die Adressen für die drei Ports A, B und C und für das Steuerwort-Register wie in Bild 34 dargestellt.

| A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | Adressen | Angesprochene Register |

|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 1 | X | X | 0 | 0 | 10 14 18 1C | Port A |

| 0 | 0 | 0 | 1 | X | X | 0 | 1 | 11 15 19 1D | Port B |

| 0 | 0 | 0 | 1 | X | X | 1 | 0 | 12 16 1A 1E | Port C |

| 0 | 0 | 0 | 1 | X | X | 1 | 1 | 13 17 1B 1F | Steuerwort-Register |

Bild 34: Die Bildung der Adressen aus den Pegeln der Adressleitungen A0 bis A7. Die Adreßleitungen A2 und A3 werden hier nicht benutzt. Da ihr Pegel 0 oder 1 sein kann, ergeben sich mehrere gültige Adressen für die Ports bzw. das Steuerwort-Register.

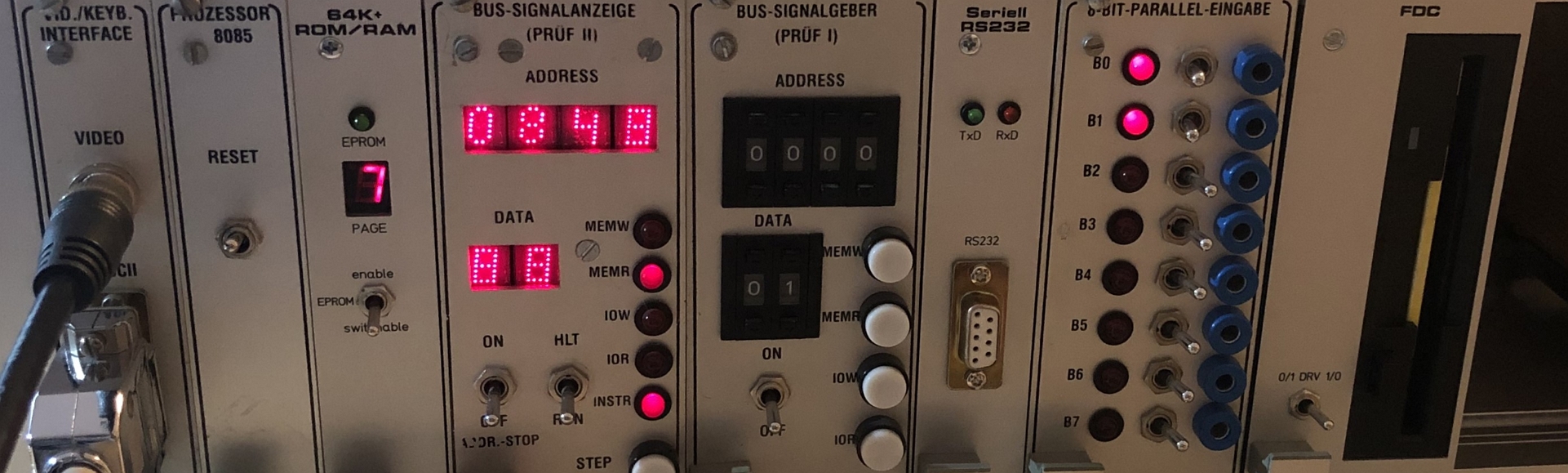

Die Initialisierung des Schnittstellenbausteins kann nun z.B. mit dem Bus-Signalgeber (siehe Kapitel 5.1) in folgenden Schritten vorgenommen werden:

- Adresse 13H (Steuerwort-Register) auf den Adreß-Bus geben

- Steuerwort 82H auf den Daten-Bus geben

- Steuersignal IOW auslösen

Nach dieser Initialisierung haben die Datenkanäle folgende Funktion:

- Kanal A wird Ausgabeport (Adr. 10)

- Kanal B wird Eingabeport ( Adr. 11)

- Kanal C wird Ausgabeport (Adr. 12)

- Wird die Baugruppe innerhalb eines Mikrocomputer-Systems als Ein/Ausgabe-Baugruppe

verwendet, so kann ihre Initialisierung z.B. durch folgendes Programm erfolgen:

| Befehl | Kommentar |

|---|---|

| MVI A, 082 | Akku mit dem Wert des Steuerwortes laden |

| OUT 013 | Akkuwert in das Steuerwort-Register schreiben |

Die Zeitwerke mit Anzeigen

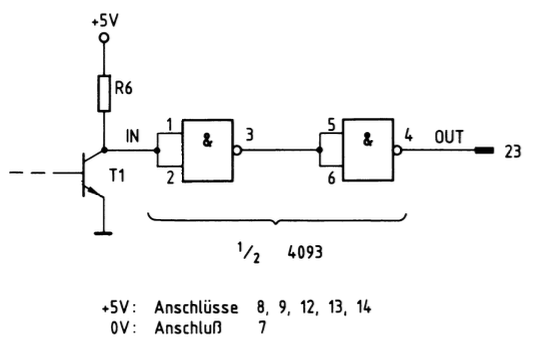

Bild 35 zeigt die Schaltung eines der vier Zeitwerke mit seiner Anzeige. An den Eingang dieser Stufe wird der Ausgang PAO des Ausgabeports A angeschlossen. Der Ausgang der Stufe wird mit dem Eingang PBO des Eingabeports B verbunden.

Bild 35: Das Zeitwerk T0 mit seiner Anzeige

Wenn das Zeitwerk T0 über die Portleitung PA0 einen L-Pegel erhält oder wenn PA0 hochohmig ist (Tristate-Ausgänge!), so befindet sich die Schaltung in ihrer Ruhelage. An ihrem Ausgang PBO stellt sich dann H-Pegel ein, und die beiden LEDs D10 und D26 leuchten nicht.

Schaltet der Mikrocomputer durch Aussenden eines geeigneten Datenwortes über Port A den Eingang auf H-Pegel, so wird das Zeitwerk gestartet.

Der Ausgang des ersten Inverters IC10.1 führt dann L-Pegel, so daß die grüne LED D1O leuchtet. Hiermit wird der Start des Zeitwerks angezeigt. Der Ausgang des folgenden Inverters IC12.1 führt den gleichen Signalpegel wie der Eingang des Zeitwerks. Dieser H-Pegel wird durch das RC-Glied verzögert dem Eingang des Schmitt-Triggers IC13.1 zugeführt. Erst wenn sich die Kondensatoren C10 und C14 soweit aufgeladen haben, daß die Schaltschwelle (Us1) des Schmitt-Triggers erreicht ist, dann erfolgt ein Signalwechsel von H- nach L-Pegel am Ausgang des Schmitt-Triggers. Gleichzeitig leuchtet LED D26 auf und zeigt den Ablauf der Zeitverzögerung an. Die Verzögerungszeit tv ist mit dem Trimmpotentiometer R38 einstellbar und hängt von der Wahl der Widerstände R34 und R38 und der Kapazität der Kondensatoren C10 und C14 ab: Bild 36 zeigt die zeitlichen Verläufe der Spannungen UE, UA und Uc.

Bild 36: Der zeitliche Verlauf von UE, UA und Uc

Ein Rücksetzen des Zeitwerks kann durch Ausgabe eines geeigneten Datenwortes über Port A erfolgen, indem der Eingang des Zeitwerks wieder L-Pegel erhält. Hierdurch wird der Stromfluß durch die LED D10 unterbrochen. Der Ausgang des Inverters IC12.1 nimmt dann ebenfalls L-Pegel an, und die Kondensatoren entladen sich sehr schnell über die Diode D22 nach Masse. Unterschreitet die Kondensatorspannung Uc die Ausschaltschwellenspannung Us2 des Schmitt-Triggers, so nimmt dessen Ausgang H-Pegel an. Das folgende Bild 37 zeigt den zeitlichen Zusammenhang zwischen dem Leuchten der beiden LEDs und dem Eingangspegel

Bild 37: Der Zusammenhang zwischen UE und dem Leuchten der LEDs zur Anzeige des gestarteten

Zeitwerks und der abgelaufenen Verzögerungszeit

Bild 38: Der zeitliche Verlauf von UE, Uc und UA für den Fall, daß UE kürzer als tvo ansteht

Da die Kondensatorspannung in der zur Verfügung stehenden Zeit die Eingangsschwellenspannung

Us1 des Schmitt-Triggers nicht erreicht, faßt dieser den Pegel der Spannung als L-Pegel auf und liefert an seinem Ausgang H-Pegel, so daß die grüne LED nicht leuchten kann.

Die rote LED leuchtet nur so lange, wie die Eingangsspannung ansteht.

Die Einstellung der Verzögerungszeit

Die Verzögerungszeit tvo wird durch zwei Einstellmöglichkeiten bestimmt. Durch die Brücken 1 – 2 und 1 – 3 ist eine Grobeinstellung in drei Stufen möglich. Eine Feineinstellung kann mit dem Trimmwiderstand R38 vorgenommen werden (Bild 35).

Den kürzesten Zeitbereich (2 … 12 s) erzielt man, wenn nur die Brücke zum Kondensator mit der kleinsten Kapazität (10 μF) geschlossen wird (1 – 2). Der längste Zeitbereich (6 … 65 s) ergibt sich durch die Parallelschaltung beider Kondensatoren (57 μF), indem die Brücken 1 – 2 und 1 – 3 geschlossen werden. Wird nur die Brücke 1 – 3 geschlossen ( 47 μF), so ergeben sich 5 … 54 s.

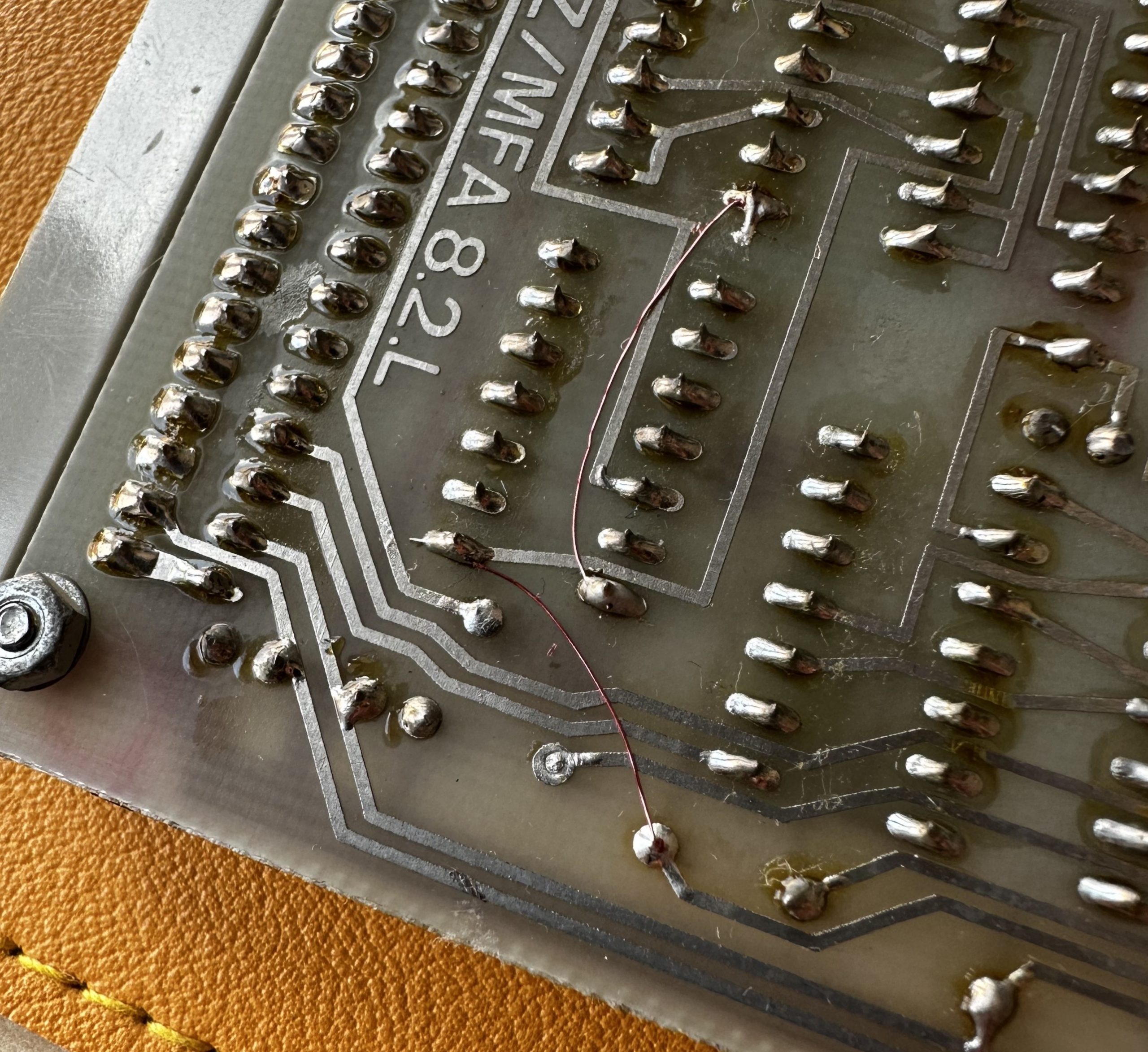

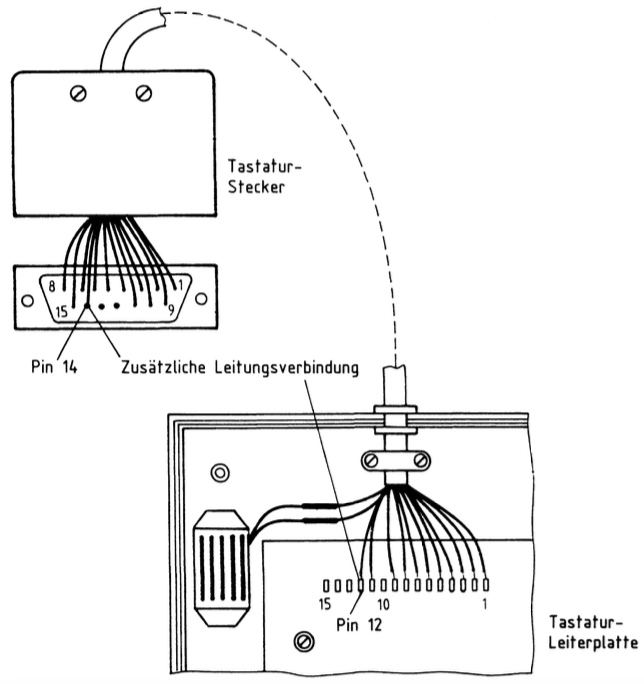

Platine

Bestückungsplan

Verdrahtungsplan