Einleitung

Mit dem NSC800-Mikroprozessor liegt ein Prozessor vor, der zur Vereinigung der jeweiligen Vorteile der Prozessoren Z80 und 8085 entwickelt worden ist. Er ist hardware-mäßig dem 8085- und softwaremäßig dem Z80-Prozessor weitgehend kompatibel. Damit bietet er die Möglichkeit, den 8085-Prozesssor im MFA-Mikrocomputersystem mit geringem Aufwand durch einen Z80-kompatiblen Prozessor zu ersetzen. Da der Befehlssatz des 8085-Prozessors bis auf die Befehle RIM und SIM eine Teilmenge des Z80-Befehlssatzes darstellt, können 8085-Programme in Z80-Systemen ablaufen. Umgekehrt ist das nicht möglich, d.h., Z80-Programme laufen nicht in 8085-Systemen.

Diese Ausbaustufe für den MFA-Mikrocomputer ist für das CP/M-System vorgesehen, weil sich damit die Möglichkeit eröffnet, das gesamte, für CP/M-Systeme verfügbare Software-Angebot nutzen zu können.

Beispielsweise wird es mit diesem Prozessor möglich, Hochsprachen wie Turbo-PASCAL auf dem MFA-Mikrocomputer einzusetzen. Speziell diese Programmiersprache ist im Personal-Computer-Bereich weit verbreitet und bietet auch im MFA-System weitere didaktische Möglichkeiten.

Darüber hinaus kann der Makroassembler M80, der Teil des Microsoft-Entwicklungspaketes (BASIC-Interpreter/-Compiler) ist, durch Ausnutzung der Z80-Mnemonik für die Einführung in die Z80-Assemblersprache verwendet werden.

Funktionsbeschreibung

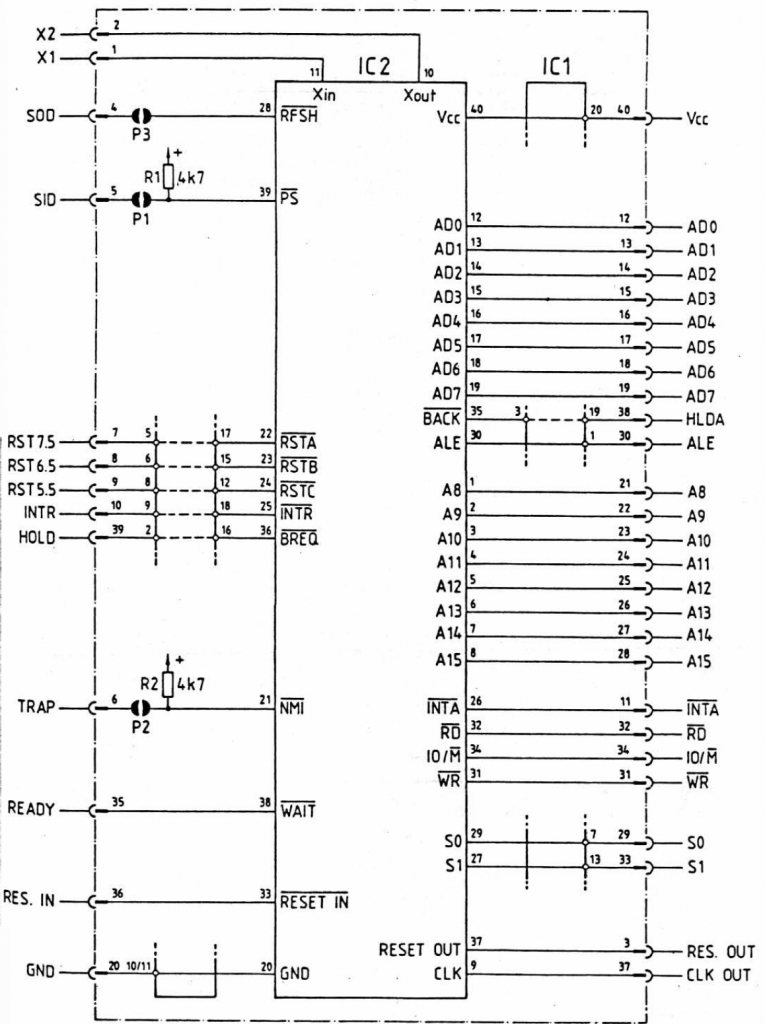

Dem Stromlaufplan der Adapter-Platine kann entnommen werden, dass die Signale des NSC800-Prozessors denen des 8085-Prozessors weitgehend entsprechen und sich teilweise lediglich in

der Bezeichnung unterscheiden. Allerdings ist die Pin-Belegung zum 8085 verschieden und einige Signale müssen invertiert werden.

In der folgenden Beschreibung wird daher im wesentlichen auf die Besonderheiten dieses Prozessors und auf die Unterschiede zum Z80 oder 8085 eingegangen.

Die Analogie der Anschlüsse zwischen dem 8085- und dem NSC800- Prozessor kann dem Schaltbild direkt entnommen werden. Der 8085-Prozessor unterscheidet sich insbesondere durch die Anschlüsse SID (Serial Input DATA, Pin 5) und SOD (Serial OUTPUT DATA, Pin 4) vom NSC800. Dafür besitzt der NSC800 die Anschlüsse PS (Power Save, Pin 39) und RFSH (Refresh, Pin 28). Auf der Adapterplatine sind diese Signale durch offene Lötbrücken vom Platinenstecker getrennt und der Eingang PS (Pin 39) liegt über einen Pull-Up- Widerstand fest auf H-Pegel. Diese Signale werden hier nicht weiter verwendet.

Darüber hinaus ist der Interrupt-Eingang NMI (Non-Maskable Interrupt, Pin 21) des NSC800 vom Platinenstecker getrennt und ebenfalls fest auf H-Pegel gelegt. Dieser Anschluss entspricht dem Interrupt-Signal TRAP des 8085. Gegenüber dem 8085 ist das NMI-Signal ein aktiv Low-Signal und die zugehörige (Restart-) Adresse ist vom 8085 verschieden.

| 8085-Anschluss | Restart-Adresse | NSC800-Anschluss | Restart-Adresse |

| TRAP (Pin 6) | 0024h | /NMI (Pin 21) | 0066h |

Die Anpassung des NSC800-Prozessors an die 8085-Prozessor-Platine erfolgt über einen PAL-Baustein (GAL16V8). Sie wurde so vorgenommen, dass die sich im aktiven Pegel unterscheidenden Signale über Inverter geführt werden. Darüber hinaus wurde auch eine weitgehende Kompatibilität zwischen dem RST7.5-Anschluß des 8085-Prozessors und dem RSTA-Anschluss des NSC800 hergestellt. Beide Anschlüsse unterscheiden sich dadurch, dass der RST7.5-Eingang des 8085 flankengesteuert arbeitet, während der RSTA-Eingang des NSC800 statisch wirkt. Da der flankengesteuerte RST7.5-Eingang Vorteile bei der Anwendung bietet, wurde mittels des PAL-Bausteins diese Anpassung ebenfalls vorgenommen. So lassen sich leichter interrupt-gesteuerte Programme realisieren, die in Verbindung mit der Zähler- und Zeitgeber-Baugruppe (BFZ/MFA 4.6) ausgetestet werden können, indem ein Interrupt über den Handtaster in der Frontplatte der Baugruppe ausgelöst wird. Dabei ist es dann unbedeutend, wie lange der Taster bestätigt wird und es brauchen keine programmiertechnischen Abfragen in das Programm eingefügt werden.

Im Anhang ist ein einfaches Beispiel für ein solches interruptgesteuertes Programm angegeben, welches manuell getestet werden kann.

Die Eingangssignale des NSC800

Im folgenden sind alle NSC800-Bausteinanschlüsse kurz beschrieben. Für eine genaue Funktionsbeschreibung sei auf das zugehörige Datenblatt der Firma National Semiconductor Corporation verwiesen.

RESET INPUT (Pin 33):

Aktiv Low-Signal; schaltet die Leitungen A8 – A15 sowie AD0 – AD7 in den Tri-State und löscht die Register PC, 1 und R; sperrt Interrupts und erzeugt das Signal RESET OUT.

BUS REQUEST (Pin 36):

Aktiv Low-Signal; wird verwendet, wenn ein anderes Gerät den BUS anfordert; die CPU erkennt das Signal am Ende des aktuellen Maschinenzyklusses; bewirkt, dass die Leitungen A8 – A15, AD0 – AD7, sowie IO/M, RD, and WR in den Tri-State geschaltet werden; die CPU bestätigt die Anforderung durch das Signal BUS ACKNOWLEDGE.

NON-MASKABLE INTERRUPT (Pin 21):

Aktiv Low-Signal; flankengesteuert; nicht-sperrbares Interrupt-Signal mit der höchsten Priorität, d.h. unabhängig vom Interrupt-Enable-Flipflop; wenn aktiv, so sichert die CPU den PC auf dem STACK und verzweigt zur Adresse 0066H.

RESTART INTERRUPTS A,B,C (Pin 22,23,24):

Aktiv Low-Signale; sperrbare Interrupt-Signale; Ausführung wie beim NMI-Interrupt; Priorität in der Folge A, B, C; zugehörige Adressen RSTA -> 003Ch, RSTB -> 0034h, RSTC -> 002Ch.

| 8085-Anschluss | Restart-Adresse | NSC800-Anschluss | Restart-Adresse |

|---|---|---|---|

| RST 7.5 (Pin 7) | 003Ch | RSTA (Pin 22) | 003Ch |

| RST 6.5 (Pin 8) | 0034h | RSTB (Pin 23) | 0034h |

| RST 5.5 (Pin 9) | 002Ch | RSTC (Pin 24) | 002Ch |

INTERRUPT REQUEST (Pin 25):

Aktiv Low-Signal; Interrupt mit der niedrigsten Priorität; die CPU unterscheidet drei Betriebsarten; in der Betriebsart 0 kann wie beim 8085 über Restart-Vektoren (RST 0 – RST 7) bzw. über einen drei-Byte Call-Befehl zur Interrupt-Service-Routine verzweigt werden; in der Betriebsart 1 verzweigt die CPU fest zur Restart-Adresse 0038H; die Betriebsart 2 erfordert spezielle Ein-/Ausgabe-Bausteine, die nach Anforderung eines lnterruptes das Low-Byte einer Adresse liefern können, dieser Teil ergänzt den

Inhalt des Interrupt-Vektor-Registers der CPU und bildet eine Speicheradresse, von der die CPU die Adresse der Interrupt-Service-Routine liest (indirekter Sprung zur 1SR).

WAIT (Pin 38):

Aktiv Low-Signal; die CPU verlängert die Maschinenzyklen durch Warte-Zyklen, wenn dieses Signal während eines RD-, WR- oder INTA-Maschinenzyklusses aktiviert wird.

POWER SAVE (Pin 39):

Aktiv Low-Signal; wenn aktiv, dann stoppt die CPU am Ende des Befehlszyklusses und geht in einen Low-Power-Mode mit geringem Stromverbrauch.

Xin,Xout (Pin 10,11):

Quarzanschlüsse für den integrierten Taktgenerator.

Ausgangssignale des NSC800

BUS AKCKNOWLEDGE (Pin 35):

Aktiv Low-Signal; zeigt an, dass die CPU den BUS und die Steuer-Signale in den Tri-State geschaltet hat (siehe BUS REQUEST).

A8 – A15 (Pin 1 – 8):

Aktiv High-Signale; acht höchstwertige Adress-Leitungen.

AD0 – AD7 (Pin 12 – 19):

Adress- und Daten-Leitungen, die im Betrieb umgeschaltet (gemultiplext) werden; die Leitungen werden beim Datentransport auch als Eingänge verwendet.

RESET OUT (Pin 37):

Aktiv High-Signal; wenn aktiv, so führt die CPU einen RESET aus.

INPUT/OUTPUT/MEMORY (Pin 34):

Das High-Signal zeigt einen Schreib- oder Lese-Zugriff der CPU auf Ein-/Ausgabe-Baugruppen an; das Low-Signal entsprechend den Zugriff auf den Speicher.

REFRESH (Pin 28):

Aktiv Low-Signal; zeigt einen Refresh-Zyklus für dynamische RAM-Speicher an.

ADDRESS LATCH ENABLE (Pin 30):

Aktiv High-Signal; ein High-Low-Signalwechsel signalisiert eine gültige Adresse, das untere Adreß-Byte muss mit diesem Signal gespeichert werden.

READ STROBE (Pin32):

Aktiv Low-Signal; die CPU liest Daten mit dem Signalwechsel am Ende des Signals.

WRITE STROBE (Pin 31):

Aktiv Low-Signal; die CPU sendet Daten während des aktiven Signals.

CLOCK (Pin 9):

Systemtakt mit einer Frequenz, die halb so groß ist wie die Frequenz des Taktgenerators.

INTERRUPT AKNOWLEDGE (Pin 26):

Aktiv Low-Signal; CPU liest mit diesem Signal den Interrupt-Vektor der Interface-Baugruppe, die den Interrupt ausgelöst hat.

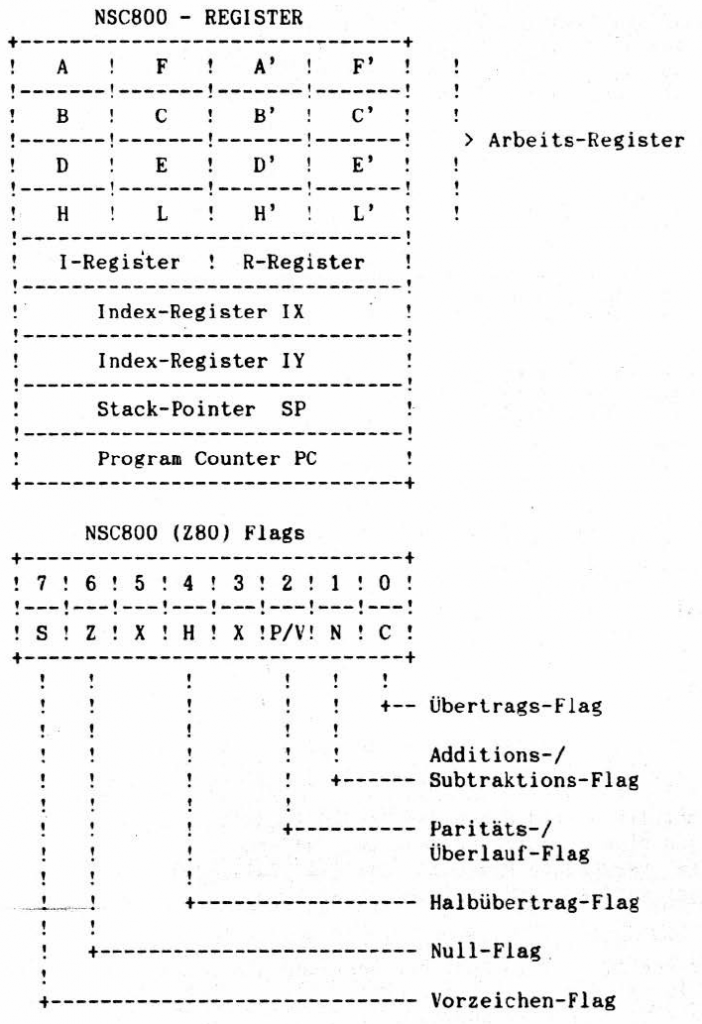

Der Register- und Befehlssatz des NSC800

Der Registersatz des NSC800 entspricht dem des Z80, d.h. er besitzt gegenüber dem 8085 den doppelten Arbeitsregistersatz sowie zwei Indexregister (IX und IY). Daneben gibt es zwei weitere Register, das Interrupt-Vektor- (I) und das Refresh-Register (R).

Der NSC800 unterscheidet in der Interrupt-Verarbeitung des Interrupt-Request-Signals (INTR, Pin 25) zwischen drei Betriebsarten. Die Betriebsart 2, auch Mode 2 genannt, verlangt spezielle Ein-/Ausgabe-Bausteine als Interrupt-Steuerbausteine. In dieser Betriebsart wird der Inhalt des I-Registers als oberer Adressteil einer Zeigeradresse für das Auffinden der Interrupt-Service- Routine verwendet. Werden dynamische RAM-Bausteine als Speicher verwendet, so müssen die RAM-Zellen in bestimmten Zeitabständen aufgefrischt werden. Der Z80 sowie der NSC800 verwenden dafür ein spezielles Register, welches als Refresh-Zähler verwendet werden kann. Im Gegensatz zum Z80 ist dieses Refresh-Register auf 8-Bit erweitert worden.

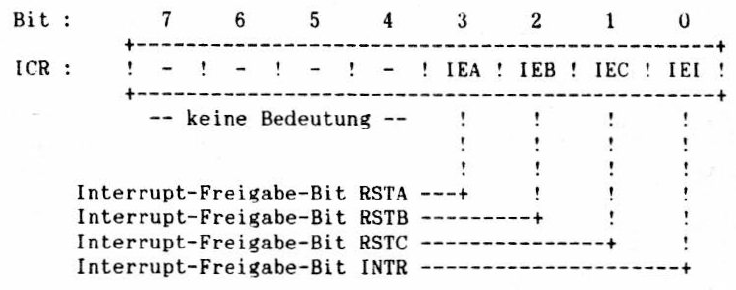

Das Interrupt-Control-Register (ICR)

Wesentlicher Unterschied zum Z80 ist ein weiteres Register, das Interrupt-Control-Register (ICR), welches in der vorstehenden Darstellung nicht aufgeführt ist. Dieses Register wurde notwendig, um die zum 8085 kompatiblen Interruptsignale RSTA, RSTB und RSTC maskieren, d.h. sperren oder freigeben zu können. Diese drei Interruptsignale, die der Z80 nicht besitzt, entsprechen den 8085-Interruptsignalen RST7.5, RST6.5 und RST5.5. Der 8085 besitzt zum Lesen und Schreiben seines lnterrupt-Masken-Registers die Befehle RIM und SIM, die beim NSC800-Prozessor nicht vorhanden sind. Sein Befehlssatz ist voll kompatibel zum Z80. Daher wird beim NSC800 das Interrupt-Control-Register wie eine Ausgabe-

Einheit mit einer festen Baugruppen-Nummer (BBH) behandelt und kann mit einem OUT-Befehl verändert werden. Im folgenden Bild ist die Zuordnung der einzelnen Masken-Bits zu den Interrupt-Signalen wiedergegeben.

Damit eine Interrupt-Anforderung von der CPU angenommen werden kann, muss das zugehörige Freigabe-Bit gesetzt ( = 1 ) sein. Darüber hinaus müssen Interrupts über den Befehl Enable Interrupt

(EI) freigegeben sein.

Der Befehlssatz

Im Anhang ist die Befehlsliste des NSC800-/Z80 dargestellt. Um die Liste möglichst kurz und übersichtlich zu gestalten, wird eine Symbolik verwendet, die in solchen Kurzdarstellungen üblich ist. In der Befehlsliste wird neben der Mnemonik und der Wirkung eines Befehls auch eine Erläuterung gegeben, sofern dies erforderlich ist. Die verwendete Sysmbolik soll im folgenden noch einmal kurz erklärt werden, um die Liste lesbar zu machen.

Ein Datum (oder ein Operand), das von einem Befehl beeinflusst wird, ist durch seine Adresse im Speicher oder durch das Register gekennzeichnet, in welchem es sich befindet. Dieser Sachverhalt wird durch folgende Schreibweise ausgedrückt:

< Adresse > = Datum im Speicher unter Adresse

< Register> = Datum im Prozessor-Register

Die spitzen Klammern symbolisieren den Inhalt der Speicherstelle oder des Registers und können wie folgt gelesen werden:

< … > = „Inhalt von … >

In der Ausführung der Befehle kommt es vor, dass ein Datun im Speicher beeinflusst wird, dessen Adresse in einem Registerpaar, z.B. dem HL-Registerpaar, steht. Dieser Sachverhalt wird wie folgt dargestellt:

<< Registerpaar >> = Datum im Speicher unter der Adresse, die im Registerpaar steht

Wird nun durch einen Befehl ein Datentransport ausgeführt, so wird dies durch die in der Programmiersprache PASCAL übliche Wertzuweisung zum Ausdruck gebracht:

< Adresse > := Ergebnis

< Register> := Ergebnis

Dies Bedeutet, daß das Ergebnis unter der Adresse im Speicher oder in dem angegebenen Register abgelegt wird.

Mit dieser Schreibweise (Notation) ist es möglich, die Befehlsliste kurz und übersichtlich zu gestalten. Nach einer Eingewöhnungsphase wird es dem Benutzer keine Probleme mehr machen, mit einer solchen Befehlsliste umgehen zu können.

Im Einzel fall kann es notwendig werden, die exakte Beschreibung eines Befehls nachlesen zu können. Dazu sei auf die Darstellungen in den Datenbüchern verwiesen oder auf die umfangreiche Fachliteratur, die es zum Z80-Prozessor gibt.

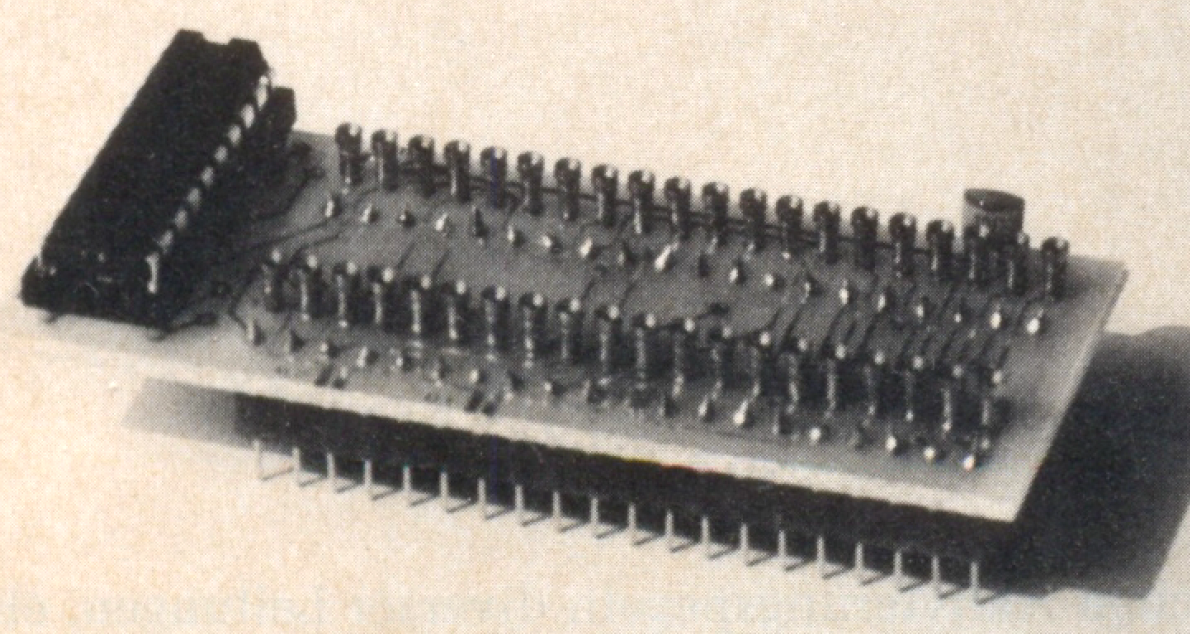

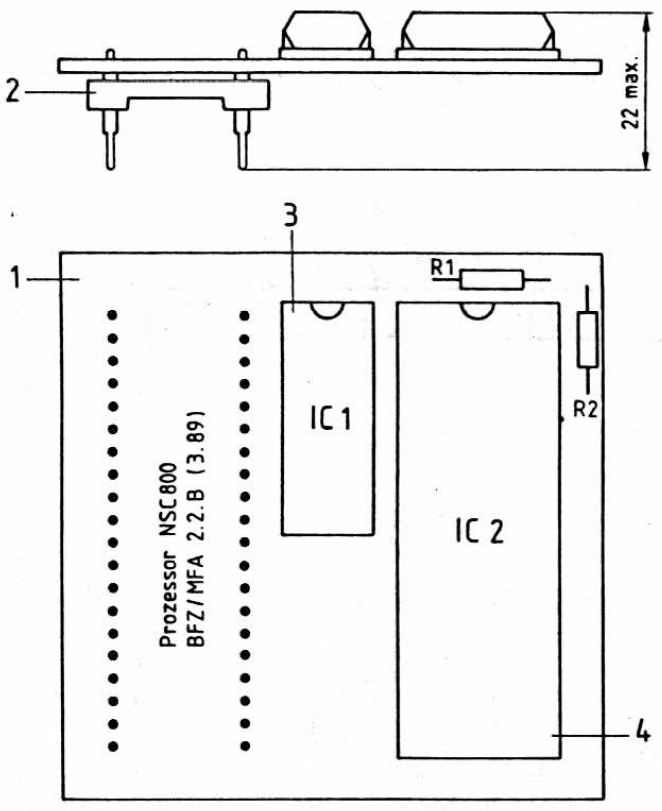

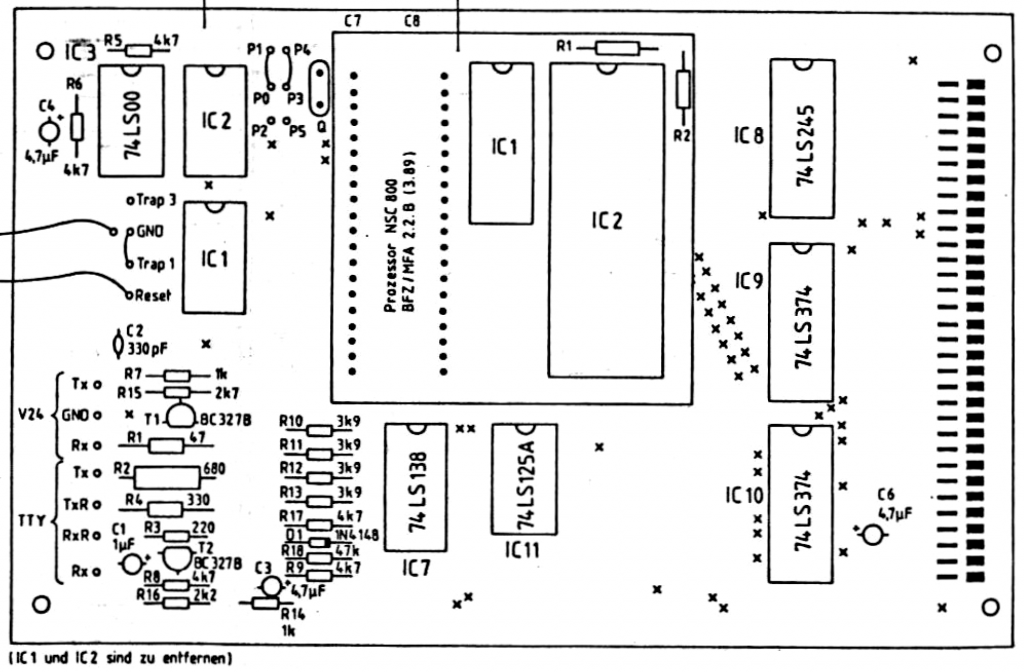

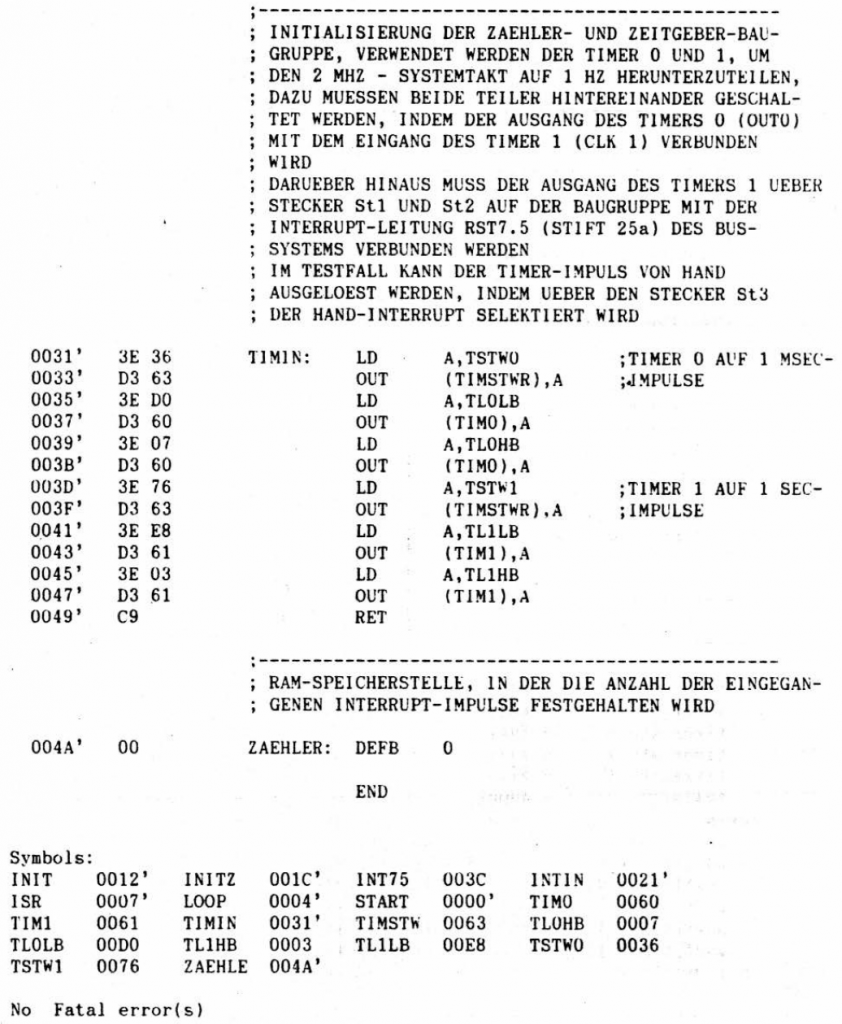

Inbetriebnahmehinweise

Für die Inbetriebnahme der Baugruppe ist lediglich die 8085-CPU auf der Prozessor-Baugruppe BFZ/MFA 2.1 gegen die Adapter-Platine auszutauschen. Dabei ist darauf zu achten, dass alle Steckerstifte korrekt in den 40-poligen IC-Stecker auf der Basisplatine eingeführt werden. Im Anhang ist die mit der Adapter-Platine bestückte CPU-Baugruppe abgebildet.

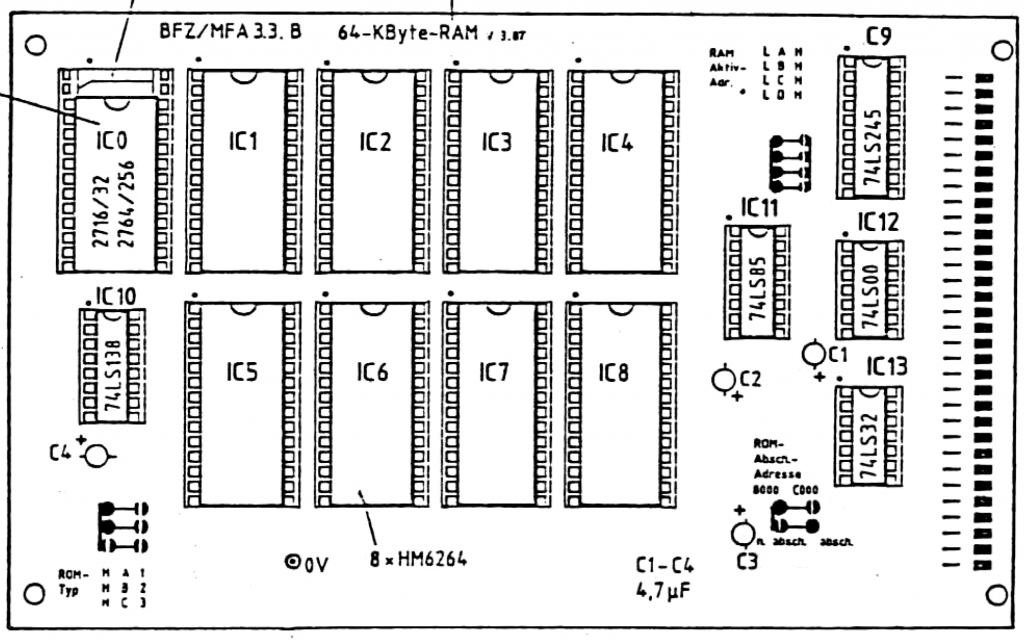

Neben dem Austausch der CPU ist das BOOT-EPROM 2716 mit dem BIOS-Programm für das CP/M-Betriebssystem auf der 64-K-RAM-Baugruppe BFZ/MFA 3.3 bzw. auf der ersten 16-K-RAM/EPROM-Baugruppe BFZ/MFA 3.2 auszutauschen. Auf den Speicher-Baugruppen bleiben alle Brücken unverändert.

Nach dem Einschalten der Betriebsspannung muss sich das System wie in der ursprünglichen 8085-Konfiguration verhalten und das Betriebsprogramm von der Diskette lesen. Dies ist der Fall, wenn am Laufwerk A der Zugriff durch Aufleuchten der roten LED angezeigt wird. Nach dem Laden des Betriebsprogramms muss das MC-System die Bereitschaft durch Ausgabe der Kommandoanforderung „A > “ anzeigen.

Sollten hier Probleme auftreten, so führen Sie die gleichen Funktionskontrollen und Inbetriebnahmeschritte durch, wie sie in den Fachpraktischen Übungen zur Prozessor-Baugruppe, der Speicher-Baugruppe und zum CP/M-System beschrieben sind. Sowohl die BUS-Signalanzeige wie auch der BUS-Signalgeber können für den Funktionstest wie in gewohnter Weise verwendet werden.

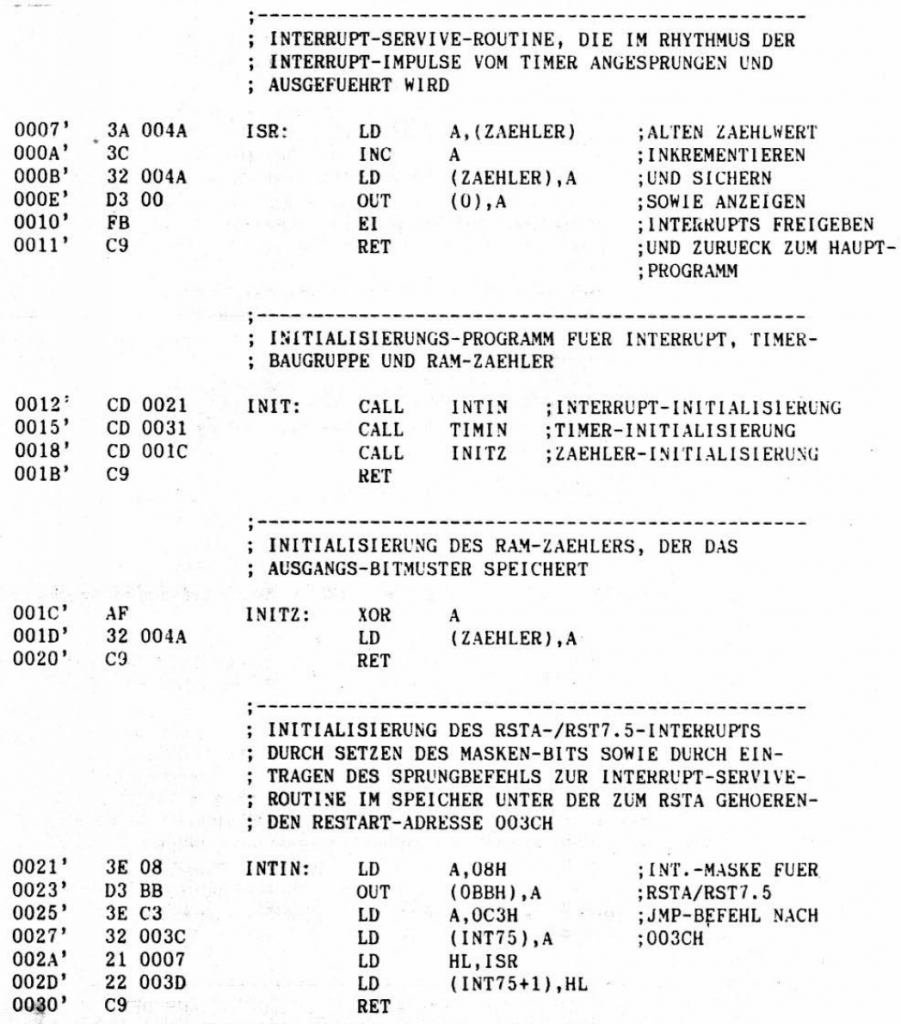

Z80-Programmbeispiel

Im Anhang A7 ist ein Programmbeispiel abgebildet, welches in der Mnemonik des Z80 geschrieben ist und mit dem Makro-Assembler M80 übersetzt wurde. Der Makro-Assembler M80 ist ein universeller Assembler, der von der Firma Microsoft zusammen mit den Hochsprachen vertrieben wird. Er ist beispielsweise in dem Mikrosoft-Entwicklungspaket BASIC-Interpreter/-Compiler enthalten und für die Einbindung von Assembler-Programmteilen in Hochsprachenprogrammen vorgesehen. Der M80 ermöglicht zusammen mit dem Linker (Binder) L80 die modulare Entwicklung von Programmen. Darüber hinaus bietet er die Möglichkeit, neben der 8080/85-Mnemonik auch Programmteile in der Z80-Mnemonik zu übersetzen, so dass mit dem gleichen Assembler in die Z80-Programmierung eingeführt werden kann.

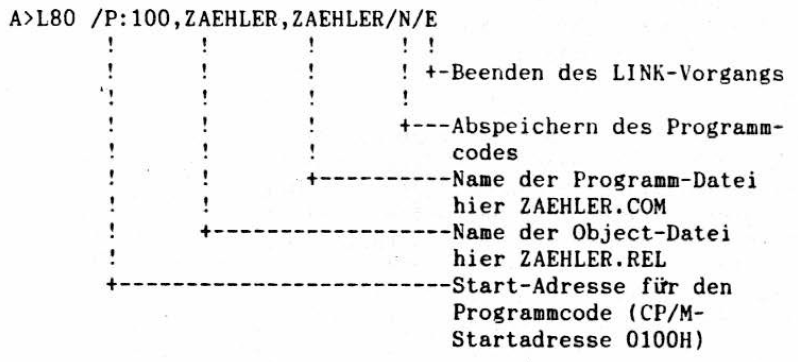

Das vorliegende Beispiel realisiert einen Zähler an der Ausgabe-Baugruppe (BG-Nr. 00) der über einen Zeit-Interrupt von der Zähler- und Zeitgeber-Baugruppe gesteuert wird. Es wurde deshalb gewählt, um die mit dem 8085-Prozessor vergleichbaren Interrupt-Möglichkeiten durch die Hardware-Anpassung über den PAL-Baustein auf der NSC800-Adapter-Platine zu demonstrieren. Für den Lerner ist es günstig, die Interrupts zunächst manuell über den Handtaster in der Frontplatte der Zähler- und Zeitgeber-Baugruppe auszulösen, um die Funktion und Wirkungsweise des Programms zu testen. Dafür ist es günstig, wenn der Interrupt-Eingang der CPU auf eine Signalflanke reagiert. Das ist beim RSTA-Eingang des NSC800 nicht der Fall, wird aber mit Hilfe eines Schaltwerkes im PAL-Baustein realisiert. Das Programm ist so dokumentiert, dass es hier nicht weiter beschrieben werden muss. Es wurde wie folgt mit Hilfe des Assemblers M80 und des Linkers L80 übersetzt:

A>M80 ZAEHLER,ZAEHLER=ZAEHLER

Aufbau: M80 List-Datei (.PRN), Objekt-Datei (.REL), Quell-Datei (.MAC)

Der Assembler erzeugt zunächst einen Maschinencode für die Start-Adresse 0000H. Diesen Code nennt man den relativen Maschinencode. Er wird vom M80 in der Object-Datei mit dem Datei-Namen ZAEHLER.REL abgelegt. Erst mit Hilfe des Linkers L80, dem man die wirkliche (absolute) Programmstart-Adresse mitteilen muss, wird der ablauffähige Programmcode erzeugt.

Das abgebildete Listing stellt den Inhalt der vom Assembler erzeugten List-Datei ZAEHLER.PRN dar.

Turbo-PASCAL-Programmbeispiel

Auf Personal- und Hobby-Computern ist zwar die Programmiersprache BASIC am weitesten verbreitet, weil sie zweifellos leicht erlernbar ist und seit je her als Interpreter ein interaktives Arbeiten erlaubt. Jedoch bieten die heute gebräuchlichen Compiler-Sprachen ebenfalls diese Möglichkeit. Dies verhalf insbesondere der Programmiersprache Turbo-PASCAL zu einem Durchbruch im Personal-Computerbereich. Leistungsfähigkeit, Einfachheit in der Bedienung sowie der günstige Preis führten dazu, daß Turbo-PASCAL heute ein Standard darstellt. Turbo-PASCAL wurde ursprünglich für CP/M-Systeme

entwickelt. Die heute auf den IBM- und kompatiblen Personal-Computer eingesetzten Versionen sind bezüglich der Bedienoberfläche weiter verbessert und im Sprachumfang, angepasst an die PC-Möglichkeiten, erweitert worden. Welche didaktischen Möglichkeiten bietet diese Programmiersprache?

Ein wesentliches Merkmal dieser wie vergleichbarer höherer Programmiersprachen ist das Prozedur-/Unterprogramm-Konzept. Programme werden vergleichbar mit der Assembler-Programmierung in übersichtliche und funktionsbezogene Einheiten, d.h. in Unterprogramme

unterteilt, die später durch Angabe des Namens aufgerufen werden.

Ein PASCAL-Programm könnte beispielsweise folgende Form haben:

program MOTOR_STEUERUNG;

(*$I UP.PAS *)

begin

WARTE_AU F_START_TASTE ;

MOTOR_EINSCHALTEN;

STARTE_LAUFZEIT;

WARTE_AUF_LAUFZEIT_ENDE;

MOTOR.AUSSCHALTEN;

end.Durch die Definition von Unterprogrammen, die in einer Datei (UP.PAS) abgelegt sind, wird die Funktion des Programms direkt lesbar. Hiermit bietet sich die Möglichkeit, dem Lernenden eine Reihe von vordefinierten Programmteilen „unsichtbar” zur Verfügung zu stellen, die er aber nutzen kann. Damit lassen sich Aufgabenbeispiele in die Vermittlung einbinden, die programmiertechnisch zu kompliziert, aber für den Auszubildenden von Interesse sind. Verfolgt man dieses Konzept konsequent, so lassen sich auch Lernanfänger über einen anwendungsbezogenen Befehlssatz in Form dieser vordefinierten Unterprogramme in den Einsatz und die Handhabung von Computern einführen.

Turbo-PASCAL hat einen bildschirm-orientierten Editor integriert, der in seinen Funktionen dem Textverarbeitungsprogramme Wordstar entspricht. Das setzt allerdings ein Computer-System voraus, welches mit einem Daten-Terminal ausgestattet ist, das Steuerfunktionen für die Positionierung des Cursors auf dem Bildschirm ermöglicht. Diese Funktionen eines Terminals nennt man „direkte Cursor-Steuerung“. Für das MFA-Mikrocomputer-System stehen mit dem Video-Interface BFZ/MFA 8.4 diese Funktionen zur Verfügung. Für den Einsatz von Turbo-PASCAL ist dieses Interface in der CP/M-Ausbaustufe erforderlich.

Bei dem nachfolgend abgebildeten Programmbeispiel, welches in der Programmiersprache Turbo-PASCAL realisiert wurde, handelt es sich wieder um den Zähler. Allerdings wurde hier die Interrupt-Verarbeitung so realisiert, dass die Interrupt-Service-Routine unter der Restart-Adresse 003CH lediglich aus dem RET-Befehl besteht und in dem Unterprogramm „warte_auf_interrupt“ der Prozessor bis

zu einem eintreffenden Interrupt-Impuls über einen HALT-Befehl

gestoppt wird.

NSC800 – Schaltplan

Pinbelegung Stromversorgung

| IC1 GAL 16V8 | IC2 NSC800 | |

|---|---|---|

| +5 V | Pin 20 | Pin 40 |

| 0 V | Pin 10,11 | Pin 20 |

- Der RST7.5-Eingang wirkt flankengesteuert; die Eingangsschaltung zum RSTA-Eingang ist

vereinfacht dargestellt! - Der NMI-Eingang NSC8D0 ist aktiv Low, so dass gegenüber der 8085-CPU hier die Bezeichnung /TRAP angegeben ist!

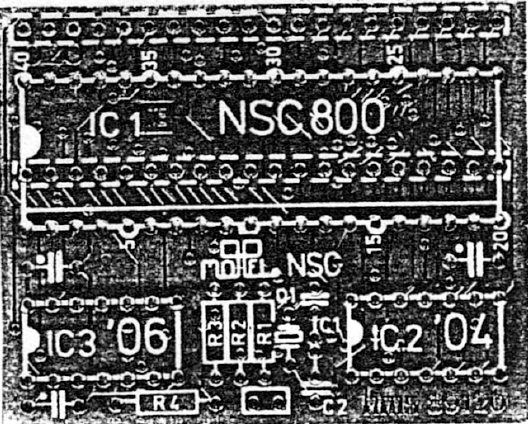

NSC800 – Adapterplatine

Aufbau / Bestückungsplan CPU

Aufbau / Bestückungsplan RAM

NSC800 Pinbelegung

Befehlsliste NSC800 / Z80

Z80-Assembler-Listing

Zaehler-Programm mit Interrupt-Steuerung

—

Anpassung des Programmes BFZFORM.COM

CP/M-Anpassung für den NSC800

Das Formatierungs-Programm BFZFORM.COM zum MFA-CP/M-System muss an den Prozessor NSC80Ü angepasst werden. Diese Anpassung kann mit Hilfe des CP/M-Debuggers DDT durchgeführt werden. Die auszuführenden Schritte sind im folgenden protokolliert, wobei zur Änderung des Programms das S-Kommando verwendet wurde.

A>DDT BFZFORM.COM < Aufruf des DDT und Laden des Programmes

DDT VERS 2.2 BFZFORM.COM in den TPA-Bereich

NEXT PC

0D80 0100

-S066A < Änderungen bei der Adresse 066A beginnen

066A 3E CD < der jeweilige Inhalt der Speicherstelle

066B OE 5D wird vom DDT angezeigt, die Eingabe

066C 30 OC Daten überschreiben diesen

066D E1 . < Abbruch der Änderungen

-S0C4C < erneute Änderung ab Adresse 0C4C

0C4C 46 4E

0C4D 4F 49

0C4E 52 43

0C4F 4D 48

0C50 41 54

0C51 54 20

0052 49 46

0C53 45 4F

0C54 52 52

0C55 45 4D

0C56 4E 41

0C57 20 54

0C58 4E 49

0C59 49 45

0C5A 43 52

0C5B 48 54

0C5C 54 24

0C5D 20 3E

0C5E 4D 02

0C5F 4F D3

0C60 45 BB

0C61 47 C9

0C62 4C 00

0C63 49 00

0C64 43 00

0C65 48 00

0C66 24 00

0C67 5A . < Abbruch der Änderungen

-^C < Rückkehr zum Betriebssystem

A> SAVE 13 NSCFORM.COM < Speichern des geänderten Programmes

unter dem Namen NSCFORM.COMAbhilfe bei Startproblemen der Takterzeugung

In Einzelfällen hat es sich gezeigt, dass der Oszillator des NSC800-Prozessors nach dem Einschalten der Betriebsspannung Anschwingproblerae hat, so dass zum Start nochmals die Reset-Taste betätigt werden muss. In hartnäckigen Fällen ist Abhilfe auf folgende Art möglich: Die beiden mitgelieferten Teile (ein Kondensator mit 27pF und ein Widerstand mit 1 MOhm) werden direkt am 2-MHz-Quarz auf die Prozessor-Hauptplatine gelötet, wie in der Skizze dargestellt: