Einleitung

Unter einem Einplatinencomputer wird allgemein ein Computersystem verstanden, das auf einer einzigen Platine neben dem Mikroprozessor mit seinen erforderlichen Steuerbausteinen zusätzlich EPROM und RAM-Speicher mit bestimmter Kapazität besitzt.

Die Kapazität der Speicherbausteine ist dabei wesentlich geringer, als die durch den Mikroprozessor maximal adressierbare Kapazität. Diese Tatsache hängt mit dem Einsatzgebieten eines Einplatinencomputers zusammen. Er soll in diesen Bereichen, fest instalIiert, ein Programm abarbeiten, das eine bestimmte Aufgabe löst. Diese Programme sind wesentIich kIeiner aIs z.B. 64 KByte.

Das Programm wird auf einem Entwicklungssystem geschrieben und in allen Funktionen getestet. Danach wird es in einem EPROM mit entsprechendem Speicherbereich fest abgelegt. Der Einplatinencomputer wird dann mit diesem EPROM bestückt und kann das Programm abarbeiten.

Neben den genannten Blöcken findet man sehr oft noch Ein- und Ausgabebausteine auf Einplatinencomputern. Diese E/A-Einheiten sind allerdings meistens auf spezielle Aufgaben zugeschnitten. Um die Einsatzmöglichkeiten dieses Einplatinencomputer universeller zu gestalten, wurde eine zusätzliche Ein- Ausgabekarte entwickelt, die direkt adaptierbar ist. Dadurch lassen sich fast alle in der Praxis vorkommenden Problemstellungen mit geringem Aufwand Iösen, da nur das Programm im

EPROM geändert werden muss.

Blockaufbau des Einplatinencomputers

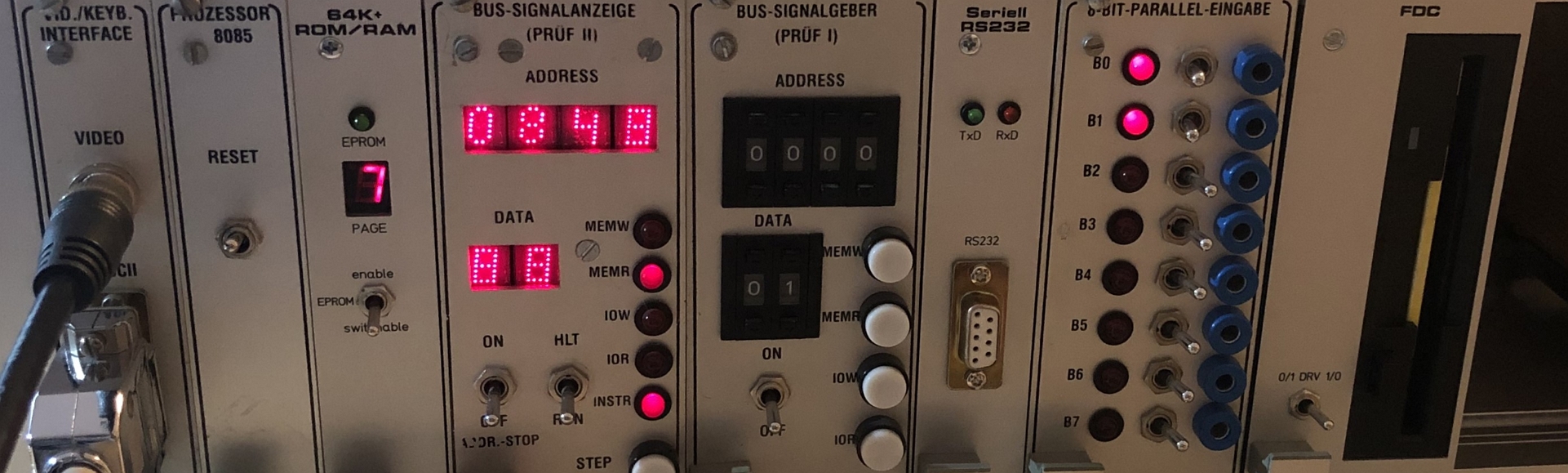

Der Einplatinencomputer ist in seinem Aufbau an das MFA-System angeIehnt. Er wurde deshalb mit dem Mikroprozessor 8085 aufgebaut und ist daneben mit der für diesen Prozessortyp erforderlichen

Adresszwischenspeicherung, einem Datenbustransceiver und einem Decoder für die Steuersignale RD, WR und IO/M bestückt.

Zusätzlich befinden sich auf der Platine ein EPROM- und ein RAM- Baustein. Die Kapazität des RAM-Bausteins beträgt 2 KByte, für den EPROM-Bereich können wahlweise Bausteine mit einer Kapazität

von 2 KByte oder 4 KByte benutzt werden. Die Unterscheidung wird durch eine Drahtbrücke auf der Platine vorgenommen. Die Pinbelegung der 64-poligen Steckerleiste ist vollkomnen kompatibel zum

Bussystem des MFA-Mikrocomputers.

Die Z-Diode ZPD 5,6 dient als Verpolungs- und Überspannungsschutz. Diese Übung setzt die Kenntnisse der Fachtheoretischen Übungen BFZ/MFA 10.1. – 10.4. voraus, da hier nicht auf die grundsätzliche Arbeitsweise eines Mikroprozessors eingegangen wird. Außerdem können weitergehende Informationen der Fachpraktischen Übung BFZ/MFA 2.1. entnommen werden.

Stromlaufplan des Einplatinencomputers

Bild 1 zeigt den Stromlaufplan des Einplatinencomputers. Dieser Stromlaufplan muss bei der Durcharbeitung der folgenden Seiten und bei der Inbetriebnahme immer benutzt werden.

Zentraleinheit (CPU)

Die Zentraleinheit des Einplatinencomputers wird durch den Mikroprozessor 8085 gebildet. Der Systemtakt dieser CPU wird durch einen 4-MHz-Quarz erzeugt und im Baustein auf 2 MHz heruntergeteilt. Am PIN 37 des Bausteins, sowie am PIN 2a der Steckerleiste, kann dieser Systemtakt gemessen werden. Dabei ist zwischen die beiden Anschlüsse der Pufferbaustein IC8 geschaltet.

Auf den folgenden Seiten sind alle auf dem Einplatinencomputer benutzten Anschlüsse der Zentraleinheit beschrieben.

Bild 2 – Systemtakterzeugung des Einplatinencomputers

RESET-Erzeugung

Jede CPU muss nach dem Anlegen der Betriebsspannung definiert zurückgesetzt werden. Das bedeutet, der Adresszähler wird auf die Adresse 0000H gesetzt.

Der Prozessor 8085 wird durch ein L-Signal am PIN 36 zurückgesetzt. Dies wird durch eine R-C- Kombination aus 47 kOhm und 4,7µF bewirkt. Der Kondensator wird über den Widerstand auf die

Betriebsspannung aufgeladen. Solange die Kondensatorspannung unterhalb eines bestimmten Wertes Iiegt , erkennt die CPU L-Signal. Für diesen Zeitraum gibt die CPU außerdem am PIN 3 H-Signal ab. Dieses Signal kann zum Rücksetzen externer Bausteine benutzt werden. Danach beginnt die CPU mit der Abarbeitung des Programms. Im BiId 3 ist dieser Zusammenhang dargestellt.

Bild 3 – RESET-Signalverlauf

Adresssignal-Erzeugung und -Decodierung

Die CPU 8085 erzeugt insgesamt 16 Adresssignale, die zum Adressbus des Einplatinencomputers gesandt werden. Die sechzehn Adresssignale Iiegen an den Anschlüssen 12-19 und 21-28 an.

Dabei entsprechen die Anschlüsse 21-28 den Adressleitungen A8-A15 . An den Anschlüssen 12-19 liegen im MuItiplexbetrieb die Adressleitungen A0-A7 und die Datenleitungen D0-D7 an. Sie werden deshalb mit AD0-AD7 bezeichnet. Die Steuerung erfolgt dabei durch ein spezielles Signal, das mit „ADRESS-LATCH-ENABLE“ (ALE) bezeichnet wird.

Ist ALE=H, so liegt das untere Adressbyte an den Anschlüssen 12-19 an , ist ALE = L , so werden diese Anschlüsse als Datenleitungen benutzt. Damit die komplette 16-Bit-Adresse stabil auf dem Adressbus des Einplatinencomputers anliegt, werden alle 16 Adresssignale zwischengespeichert. Dies erfolgt mit Hilfe des ALE-Signals und der beiden Bausteine IC3 und IC4. Die beiden Bausteine stellen jeweils acht D-Flip-Flops dar, die mit einer positiven Taktflanke gesteuert werden. Die Taktflanke wird aus dem invertierten ALE-Signal gewonnen.

Außerdem erfolgt durch diese beiden Bausteine eine Pufferung der o.g. CPU-Anschlüsse. Bild 4 verdeutlicht die beschriebenen Zusammenhänge.

Bild 4 – Adresszwischenspeicherung

Datensignale

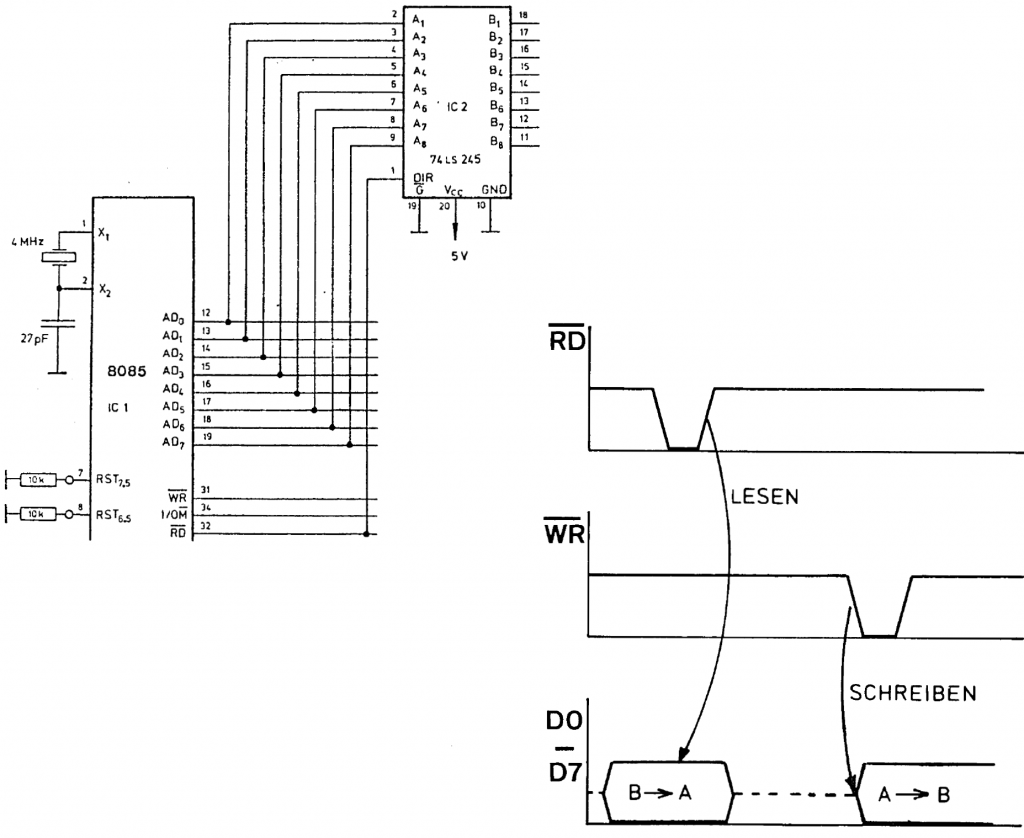

Die Datenleitungen der CPU werden durch den Baustein IC2 gepuffert. Da der Datenbus aber immer bidirektional ist, muss dieser Baustein in der Datenflussrichtung umschaltbar sein. Die Umschaltung erfolgt durch einen entsprechenden Pegel am Pin 1 dieses Bausteins. Liegt L-Signal an, so kann die CPU Daten zum Datenbus des Einplatinencomputers senden. Liegt H-Signal an, so kann die CPU Daten vom Datenbus empfangen. Die Steuerung erfolgt durch das Steuersignal RD der CPU.

Bild 5 zeigt den entsprechenden Schaltungsauszug.

Bild 5 – Datensignale des Einplatinencomputers

Steuersignaldecodierung

Die CPU 8085 liefert drei Steuersignale. Die Bezeichnung und Bedeutung dieser Steuersignale ist in der folgenden Tabelle 1 zusammengestellt.

| !RD | !WR | IO / !M | ||

| Speicher | Lesen | L | H | L |

| Speicher | Schreiben | H | L | L |

| Ein- Ausgabe | Lesen | L | H | H |

| Ein- Ausgabe | Schreiben | H | L | H |

Auf dem Steuerbus des Einplatinencomputers werden aber die vier Steuersignale MEMR, MEMW, IOR und IOW benötigt. Die o.g. Steuersignale der CPU müssen also decodiert werden. Diese Decodierung erfolgt durch den Baustein IC6. Es handelt sich dabei um einen 1 aus 4 – Decoder, dessen logische Funktion aus der folgenden Tabelle 2 hervorgeht. Die vier Steuersignale werden außerdem durch den Baustein IC8 gepuffert.

| !RD | !WR | IO / !M | !IOW | !IOR | !MEMW | !MEMR | ||

| Speicher | Lesen | L | H | L | H | H | H | L |

| Speicher | Schreiben | H | L | L | H | H | L | H |

| Ein- Ausgabe | Lesen | L | H | H | H | L | H | H |

| Ein- Ausgabe | Schreiben | H | L | H | L | H | H | H |

Tabelle 2: Decodierung der CPU-Steuersignale

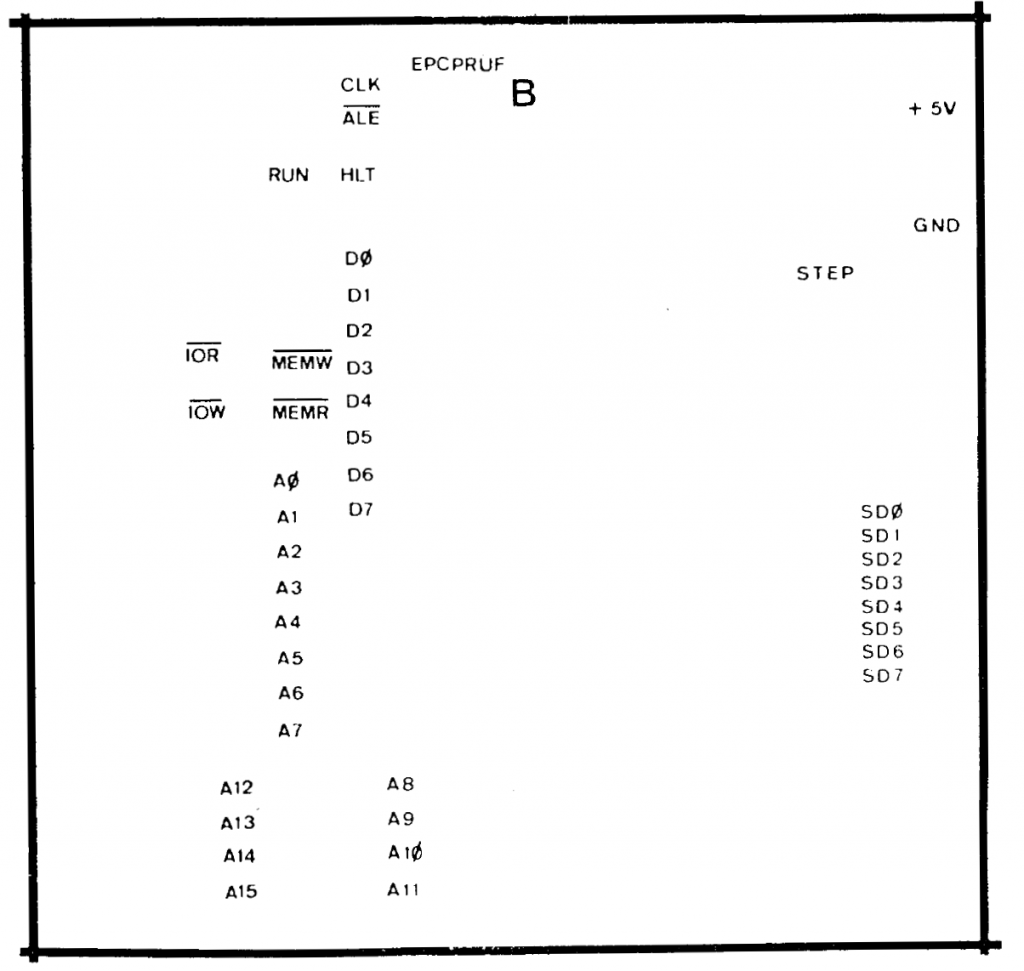

Prüfkarte

Bei der Inbetriebnahme des Einplatinencomputers ist es sinnvoll, die CPU nicht dynamisch zu betreiben, sondern ein vorgegebenes Prüfprogramm in einzelnen Schritten abzuarbeiten. Dabei wird die Schrittweite nicht durch den Takt der CPU bestimmt, sondern durch die Betätigung eines externen Tasters. Zu diesem Zweck wurde eine direkt adaptierbare Prüfkarte entwickelt , die neben der Einzelschrittsteuerung der CPU die Messung der Adresssignale, der acht Datensignale und der vier Steuersignale erlaubt.

Außerdem besteht die Möglichkeit, über einen 8-poligen DIL-Schalter ein festes Datenwort einzustellen, das von der CPU geIesen wird.

Bild 6: Stromlaufplan der Prüfkarte

Einzelschrittbetrieb der CPU

Hinweis: Benutzen Sie zu der folgenden Beschreibung den Stromlaufplan.

Die CPU 8085 besitzt einen sog. „READY“-Anschluss, der folgende Funktion hat:

Liegt dieser Anschluss auf konstantem H-Pegel, so arbeitet die CPU ein vorgegebenes Programm dynamisch ab, d.h. die Arbeitsgeschwindigkeit wird durch den Systemtakt bestimmt.

Liegt der READY-Anschluss dagegen auf L-Pegel , so stoppt die CPU die Programmabarbeitung und wartet so lange, bis READY wieder H-Pegel führt.

Ist der Schalter RUN/HLT auf der Prüfkarte geöffnet, so erhält der READY-Eingang über den Widerstand R4 auf dem Einplatinencomputer konstanten H-Pegel.

Wird der Schalter geschlossen, so wird der READY-Eingang mit dem Q-Ausgang von FF2 verbunden. Führt jetzt das ALE-Signal einen HL-Sprung durch, so wird FF2 zurückgesetzt und der READY-Eingang

liegt auf L-Pegel. Damit wird die CPU in den Wartezustand versetzt.

Der H-L-Sprung des ALE-Signals bedeutet aber, dass die CPU die nächst höhere Adresse ausgesandt, das unter dieser Adresse stehende Datenbyte gelesen und die entsprechende Steuerleitung aktiviert hat.

Mit einem Logiktester können jetzt die Daten-, Adress- und Steuersignale auf der Prüfkarte gemessen werden. Wird der STEP-Taster danach gedrückt , so wird FF1 gesetzt, Q1 führt einen L-H-Sprung aus, FF2 wird ebenfalls gesetzt, Q2 nimmt H-Pegel an und der READY-Eingang ebenso. Jetzt arbeitet die CPU das vorher gelesene Datenbyte ab. Nach der Abarbeitung führt ALE wieder einen H-L-Sprung durch (die nächst höhere Adresse wird ausgesandt) und setzt FF2 zurück, wodurch der READY-Eingang wieder L-Pegel führt.

Wird der STEP-Taster losgelassen, so wird FF1 ebenfalls zurückgesetzt, und bei nochmaligem Betätigen des Tasters läuft der beschriebene Vorgang erneut ab.

Im Bild 7 sind die auf der Seite 12 beschriebenen Zusammenhänge nochmals im Liniendiagramm dargestellt.

Bild 7: Einzelschrittbetrieb der CPU 8085

lnterrupteingänge der CPU 8085

Der Mikroprozessor 8085 besitzt insgesamt fünf lnterrupteingänge, von denen beim Einplatinencomputer vier benutzt werden können. Grundsätzlich ist bei einem Interrupt folgendes zu beachten:

Der Mikroprozessor unterbricht die laufende Programmabarbeitung und speichert die aktuelle Programmadresse ab. Danach wird die sog. Interruptroutine abgearbeitet. Ist die Abarbeitung erfolgt, fährt der Prozessor in dem vorher unterbrochenen Programm fort.

Restarteingänge RST5.5, 6.5 und 7.5

Diese drei Eingänge sind H-aktiv, wobei der Eingang RST 7.5 auf die positive Flanke eines Signals reagiert, während die Eingänge RST 6.5 und RST 5.5 zustandsgesteuert sind. Per Befehl lässt sich bestimmen, auf welchen der drei Eingänge der Mikroprozessor reagieren soll, d.h. einer oder mehrere Eingänge können ausgeblendet werden. Dieser Befehl lautet SIM (Set Interrupt Mask). Man spricht in diesem Zusammenhang auch von maskierbaren lnterrupteingängen. Nach Annahme eines „Restart-lnterrupts“ wird durch den Mikroprozessor eine vom Hersteller festgelegte Adresse ausgesandt, unter der dann ein Sprungbefehl zur lnterruptroutine stehen muss. In Tabelle 3 sind diese Adressen zusammengefasst.

Da diese drei Eingänge auf dem Einplatinencomputer offen Iiegen, wurden drei 10-kOhm-Widerstände als Pull-Down-Widerstände eingesetzt, damit ein ungewollter Interrupt nicht ausgelöst werden kann. Außerdem können die drei Eingänge durch den Befehl DI (Disable Interrupt) gesperrt und durch den Befehl EI (Enable Interrupt) freigegeben werden.

| Interrupt | Adresse |

|---|---|

| RST 5.5 | 002Ch |

| RST 6.5 | 0034h |

| RST 7.5 | 003Ch |

Interrupt-Eingang INTR und -Ausgang INTA

Dieser lnterrupteingang wird bei einem RESET der CPU automatisch gesperrt. Außerdem besteht die Möglichkeit, diesen Eingang durch den Befehl DI (Disable Interrupt) zu sperren, bzw. durch den Befehl EI (Enable Interrupt) freizugeben. Der Eingang ist, wie die Eingänge RST 5.5 und 6.5, H-aktiv.

Im Gegensatz zu den RESTART-Eingängen muss nach Annahme dieses Interrupts vom Anwender ein CALL-Befehl vorgegeben werden, dessen Adresse auf die Interrupt-Routine weist.

Der Prozessor gibt nach Annahme des Interrupts am Ausgang INTA ein L-Signal ab. Der INTR-Eingang wurde auf dem Einplatinencomputer ebenfalls mit einem Pull-Down-Widerstand beschaltet. Außerdem wurde der INTR-Eingang und der INTA-Ausgang auf die Steckerleiste des Einplatinencomputers geführt. Der Ausgang ist dabei durch IC8 gepuffert.

Steuersignale S0 und S1

Diese Steuersignale stehen in engem Zusammenhang mit dem Signal I0/M. Die nachfolgende Tabelle gibt Auskunft über den Zusammenhang der drei Signale.

| IO / !M | S1 | S0 | |

|---|---|---|---|

| L | L | H | Speicher schreiben |

| L | H | L | Speicher lesen |

| H | L | H | E/A schreiben |

| H | H | L | E/A lesen |

| L | H | H | Befehlsbyte lesen |

Ein- und Ausgänge zur seriellen Datenübertragung

Der Prozessor 8085 besitzt neben den acht Datenleitungsanschlüssen, die zur parallelen Datenübertragung dienen, einen Ein- und einen Ausgang zur seriellen Datenübertragung.

Die serielle Datenübertragung bietet gegenüber der parallelen den Vorteil, dass nur zwei Leitungen benötigt werden. Sie hat allerdings den Nachteil, dass sie langsamer als die parat feie Datenübertragung ist, da die acht Bit nur zeitlich hintereinander übertragen werden können. Außerdem ist ein höherer Softwareaufwand erfordert ich. Die serielle Datenübertragung wird auf Grund ihres Vorteils sehr häufig zur Datenfernübertragung benutzt. Der serielle Eingang der CPU wird mit SID bezeichnet, der serielle

Ausgang mit SOD.

Die beiden Anschlüsse sind über einen Pufferbaustein auf die Steckerleiste des Einplatinencomputers geführt (IC8).

Speicherbereich des Einplatinencomputers

EPROM-Speicherbereich

Für diesen Speicherbereich kann entweder der Baustein 2716 mit 2 KByte Speicherkapazität oder der Baustein 2732 mit 4 KByte Speicherkapazität benutzt werden. Die Unterscheidung erfolgt durch eine isolierte Drahtbrücke auf der Platine. Es gilt folgende Zuordnung:

Baustein

- 2716

Drahtbrücke P1 – P2 - 2732

Drahtbrücke P1 – P3

Die Adressdecodierung erfolgt durch die Bausteine 74LS00 (IC9) und 74LS04 (IC10). Allerdings muss auf dem Einplatinencomputer nicht die gesamte 16-Bit-Adresse decodiert werden, sondern nur die Adressleitung A13. Solange diese Adressleitung L-Signal führt, wird das EPROM angesprochen . Bei H-SignaI auf die Leitung wird der RAM-Baustein angesprochen. Dadurch bedingt kann sich z.B. der Adressbereich des EPROMs entweder von 0000-07FF (2716) oder von 0000-0FFF (2732).

RAM-Speicherbereich

Der RAM-Speicherbereich wird durch den Baustein 6116 mit einer Kapazität von 2 KByte realisiert. Dieser Baustein wird immer dann angesprochen, wenn die Adressleitung A13 H-Signal führt. Der Adressbereich kann sich also z.B. von 2000-27FF. Bild 8 zeigt nochmals einen entsprechenden Schaltungsauszug, und Tabelle 5 stellt die Adressdecodierung der beiden Speicherbausteine dar.

| Adresse | A13 | /CS EPROM | /CS RAM |

|---|---|---|---|

| 0000 | L | L | H |

| 1FFF | L | L | H |

| 2000 | H | H | L |

| 2FFF | H | H | L |

Bild 8: Speicherbereich des Einplatinencomputers

Flussdiagramm für den Arbeitsablauf

Hinweis: Auf den folgenden Seiten wird der Einplatinencomputer kurz als EPC bezeichnet!

Aufbau und Inbetriebnahme

In dieser Übung werden Sie den Einplatinencomputer aufbauen und in Betrieb nehmen. Falls Sie bereits eine fertig aufgebaute Baugruppe erhalten haben, besteht Ihre Aufgabe darin, sie zu prüfen und in Betrieb zu nehmen.

In dieser Übung werden Sie die Prüfplatine zum Einplatinencomputer bestücken und in Betrieb nehmen. Falls Sie bereits eine fertig aufgebaute Baugruppe erhalten haben, besteht Ihre Aufgabe darin, sie zu prüfen und in Betrieb zu nehmen.

Die Inbetriebnahme ist folgendermaßen aufgeteilt:

- statische Funktion des EPC

hier wird die CPU im Einzelschritt betrieben. Der Schalter RUN/HLT auf der Prüfplatine muss dabei auf HLT stehen. - dynamische Funktion der EPC

die CPU arbeitet jetzt mit der durch den Systemtakt vorgegebenen Geschwindigkeit. Der Schalter RUN/HLT der Prüfplatine muss dabei auf RUN stehen.

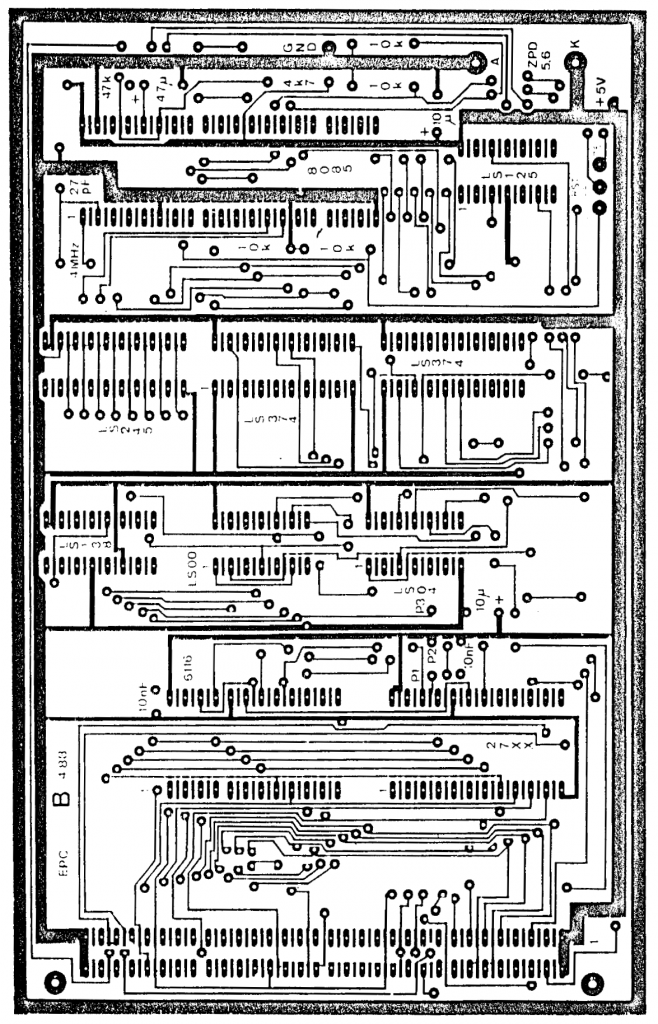

Für den Einplatinencomputer benötigen Sie eine zweiseitigkupferkaschierte und durchkontaktierte Leiterplatte.

EPC Lötseite

Leiterbahnseite der Platine

EPC Bestückungsseite

EPC Bestückungsplan

Bestücken Sie die Leiterplatte mit Hilfe des Bestückungsplans, der Stückliste und der Bauteilliste. Vorher sollten Sie die Leiterplatte mit einer Lupe nach Rissen und Kurzschlüssen untersuchen und Fehler beseitigen.

Prüfplatine

Für die Prüfkarte benötigen Sie eine einseitig-kupferkaschierte Leiterplatte.

Leiterbahnseite der Prüfplatine

Bestückungsseite der Prüfkarte

Bestücken Sie die Leiterplatte mit Hilfe des Bestückungsplans, der Stückliste und der Bauteilliste. Vorher sollten Sie die Leiterplatte mit einer Lupe nach Rissen und Kurzschlüssen untersuchen und Fehler beseitigen.

Bestückungsplan der Prüfkarte

Inbetriebnahme

Für die Sichtkontrolle sowie die Inbetriebnahme der Prüfkarte muß der Stromlauf- und Bestückungsplan bereit liegen.

Kontrollieren Sie alle Lötstellen auf der Leiterbahnseite und achten Sie auf Kurzschlüsse, die beim Löten eventuelI zwischen den Leiterbahnen entstanden sein könnten.

Achten Sie bei der Kontrolle der BauteiIe auf foIgende Punkte:

- Sind die beiden DIL-Schiebeschalter richtig eingebaut?

- Ist der Digitaster richtig eingebaut?

- Die IC’s dürfen noch nicht gesteckt sein

Auf den folgenden Seiten werden Sie die Prüfkarte in Betrieb nehmen. Sie benötigen dazu:

- 1 SV-Netzteil

- 1 Digital- oder Analog-Vielfachinstrument

- 1 Logiktester

Messen Sie an den entsprechenden Anschlüssen der nicht bestückten IC-Sockel die Versorgungsspannung.

Dazu schließen Sie ein 5V-NetzteiI an die Stecklötösen +5V und GND an. Suchen Sie sich aus dem Stromlaufplan die entsprechenden Anschlüsse heraus und tragen Sie Ihre Messergebnisse in die folgende

Tabelle ein.

| IC1 | IC2 | |

|---|---|---|

| Versorgungsspannung an PIN | ||

| Masse an PIN | ||

| Ub / V | ||

| GND |

Wenn die Messergebnisse korrekt sind, können Sie die Betriebsspannung ausschalten, die IC’s in die Fassungen stecken (Achten Sie auf den richtigen Einbau) und die Betriebsspannung wieder einschalten.

Bei dem Baustein 74LS641 (IC1) handelt es sich um einen bidirektionalen Treiberbaustein mit Open-Collector-Ausgängen. Durch die feste Beschaltung des DIR-Steuereingangs mit +5V ist der Baustein so voreingestellt, dass er nur Daten von den Anschlüssen A0-A7 zu den Anschlüssen B0-B7 senden kann. Die Signale werden dabei durch den 8-poligen DIL-Schiebeschalter vorgegeben.

Überprüfen Sie jetzt mit Hilfe eines Logiktesters die Funktion des Bausteins und tragen Sie Ihre Messergebnisse in die folgende Tabelle ein. Überlegen Sie dabei, welche Pegel bei der entsprechenden Schalterstellung des 8-poligen Schiebeschalters am IC zu messen sein müssen.

| 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SD7-SD0 01010101 | ||||||||||||||||

| SD7-SD0 10101010 |

Der Baustein 74LS74 (IC2) enthält zwei taktzustandsgesteuerte D-FLIP-FLOPS mit L-aktiven, statischen Setz- und Rücksetzeingängen. Das FLIP-FLOP1 soll den Step-Taster entprellen, dass FLIP-FLOP2 steuert den READY-Eingang der CPU 8085 an.

Bevor Sie diesen Übungsteil durchführen, machen Sie sich die Arbeitsweise des Stepbetriebs mit Hilfe von Seite 12 noch einmal klar.

Arbeitsweise von FF1:

Ist der Step-Taster nicht betätigt, so ist das FLIP-FLOP zurückgesetzt und Q1 muss L-Pegel führen. Bei Betätigung des Step-Tasters wird FF1 gesetzt und Q1 muss H-Pegel führen.

Arbeitsweise von FF2:

Nimmt der Clock-Eingang C2 H-Pegel an (gesteuert durch Q1), so kann der Ausgang Q2 nur dann H-Pegel annehmen, wenn S2 und R2 ebenfalls H-Pegel führen. Führt der Eingang R2 dagegen L-Pegel, so wird FF2 zurückgesetzt und Q2 nimmt L-Pegel an.

Überprüfen Sie die Funktion von FF1 und FF2 mit Hilfe eines Logiktesters und tragen Sie Ihre Messergebnisse in die folgende Tabelle ein. Der angegebene Pegel des ALE-Signals kann durch eine Leitung zwischen +5 Volt bzw. GND und dem ALE-Messpunkt auf der Prüfkarte hergestellt werden.

| ALE | STEP-Taster | /R1 | /S1 | Q1 | C2 | /R2 | Q2 |

|---|---|---|---|---|---|---|---|

| H | nicht betätigt | L | H | L | L | H | H |

| H | betätigt | H | L | H | H | H | H |

| L | nicht betätigt | L | H | L | L | L | L |

| L | betätigt | H | L | H | H | L | L |

Damit ist die Inbetriebnahme der Prüfkarte beendet!

Inbetriebnahme EPC

Für die Sichtkontrolle sowie die Inbetriebnahme des EPCs muss der Stromlauf- und Bestückungsplan bereitliegen.

Kontrollieren Sie alle Lötstellen auf der Leiterbahnseite und achten Sie auf Kurzschlüsse, die beim Löten eventuell zwischen den Leiterbahnen entstanden sein könnten.

Achten Sie bei der Kontrolle der Bauteile auf folgende Punkte:

- Sind alle Widerstände mit Ihrem richtigen Wert eingebaut?

- Sind alle Elkos richtig gepolt?

- Die IC’s dürfen nicht gesteckt sein

- Die Brücke P1-P2 oder P1-P3 muss vorhanden sein

- Die lsolierscheibe muss sich auf der Bestückungsseite unter dem Quarz befinden

Adaptieren Sie die fertige Prüfkarte an den Einplatinencomputer und schließen Sie die Versorgungsspannung von 5V über die Prüfkarte an. Messen Sie die Spannungsversorgung an allen IC-Sockeln. Suchen Sie sich aus dem Stromlaufplan die entsprechenden Anschlüsse heraus und tragen Sie Ihre Messergebnisse in die folgende Tabelle ein.

| TYP | IC1 | IC2 | IC3 | IC4 | IC4 | IC5 | IC6 | IC7 | IC8 | IC9 | IC10 |

|---|---|---|---|---|---|---|---|---|---|---|---|

| Pos. Versorgungs- Spannung | |||||||||||

| Masse an Pin | |||||||||||

| Ub | |||||||||||

| GND |

Nachdem Sie die Betriebsspannung an allen IC-Sockeln überprüft haben, werden die Daten- und Steuerleitungen auf Kurzschlüsse und Unterbrechungen untersucht. Da bei der Vielzahl der Leitungen und der sich daraus ergebenden Dichte auf der Platine, eine Sichtkontrolle nur schwer möglich ist, werden sie elektrisch überprüft.

Überprüfung der Datenleitungen

Stellen Sie mit Hilfe der Schalter SD7-SD0 auf der Prüfkarte das Datenwort 01010101 ein und überprüfen Sie, ob die gleichen Pegel an den entsprechenden Anschlüssen der bei den Speicherbausteine sowie an den B-Anschlüssen von IC2 des EPCs anliegen. Danach stellen Sie das Datenwort 10101010 ein und überprüfen wiederum die Pegel an den drei IC’s. Tragen Sie Ihre Messergebnisse in die Tabelle auf der folgenden Seite ein, überprüfen Sie die Richtigkeit und beseitigen Sie eventuell auftretende Fehler.

Eingestelltes Datenwort: 01010101

| EPROM | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 |

| RAM | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 |

| 72LS245 | B1 | B2 | B3 | B4 | B5 | B6 | B7 | B8 |

Eingestelltes Datenwort : 10101010

| PROM | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 |

| RAM | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 |

| 72LS245 | B1 | B2 | B3 | B4 | B5 | B6 | B7 | B8 |

ACHTUNG: BEI DEN NÄCHSTEN ARBEITSSCHRITTEN MUSS DIE BETRIEBSSPANNUNG ABGESCHALTET WERDEN!!!

Überprüfen Sie jetzt mit einem Ohmmeter , ob die Leitungen zwischen den A-Anschlüssen von IC2 und dem CPU-Sockel keine Unterbrechungen bzw. Kurzschlüsse aufweisen. Niederohmige Verbindungen kennzeichnen Sie in der folgenden Tabelle mit „I“, hochohmige mit „H“.

Kontrolle der Adressleitungen

Überprüfung auf Unterbrechungen

| IC2 (PIN) | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

| CPU (PIN) | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 |

| Messergebnis |

Überprüfung auf Kurzschluss

| IC2 (PIN) | 2-3 | 3-4 | 4-5 | 5-6 | 6-7 | 7-8 | 8-9 |

| Messergebnis | | | | | | | |

Die Steuerleitungen werden ebenfalls mit einem Ohmmeter auf Unterbrechungen

und Kurzschlüsse untersucht. Niederohmige Verbindungen werden mit „L“, hochohmige mit „H“ gekennzeichnet.

Überprüfung auf Unterbrechungen

Dazu wird das Ohmmeter auf der einen Seite an die Stecklötösen der Prüfkarte angeschlossen, auf der anderen Seite an die entsprechenden Anschlüsse von IC6.

| IC6 (EPC) | 9 | 12 | 11 | 14 |

| Prüfkarte | IOW | IOR | MEMW | MEMR |

| Messergebnis |

Überprüfung auf Kurzschluss

Es wird der Widerstand zwischen jeweils zwei Leitungen auf der adaptierten Prüfkarte gemessen

Untersuchung auf Unterbrechungen

| IC6 (PIN) | 1 | 2 | 3 |

| CPU (PIN) | 31 | 34 | 32 |

| Messergebnis |

Untersuchung auf Kurzschluss an den Anschlüssen von IC6

| IC6 (EPC) | 1-2 | 2-3 |

| Messergebnis |

Wenn die Meßergebnisse der letzten beiden Seiten keine Fehler aufwiesen, kann der Einplatinencomputer jetzt mit der CPU, dem Datenbustransceiver IC2, den Adreßzwischenspeichern IC3 und IC4, dem Steuersignaldecoder IC6 sowie dem Pufferbaustein IC8 bestückt werden. Die beiden Speicherbausteine werden noch nicht in die Sockel gesteckt.

Nach Einschalten der Betriebsspannung können jetzt die Adreßleitungen auf Kurzschlüsse und Unterbrechungen untersucht werden. Danach wird die Arbeitsweise der CPU in Verbindung mit den anderen Bausteinen überprüft.

Zuerst muss aber die Quarzfrequenz und die Taktfrequenz der CPU gemessen werden. Machen Sie sich mit HiIfe von Seite 6 den entsprechenden Sachverhalt noch einmal klar. Oszilloskopieren und zeichnen Sie dann folgende Signale:

- Upin1 = f(t) —> an der CPU

- Upin37 = f(t)

- UCLK = f(t) —> auf der Prüfplatine

Benutzen Sie für die Messungen an der CPU den 40poligen Adapter.

Die Messungen an der CPU müssen mit einem 10:1-Tastkopf durchgeführt werden!

RESET-Erzeugung

Der Programmzähler der CPU wird bei L-Pegel am Eingang RESIN auf 0000 zurückgesetzt. Außerdem werden die Adress-, Daten- und SteuerIeitungsanschIüsse in den hochohmigen Zustand geschaltet. Der Ausgang RESOUT gibt in dieser Phase H-Pegel ab.

Überprüfen Sie die beschriebene Funktion, indem Sie über den 40poligen Messadapter an den PIN 36 der CPU L-Pegel anlegen. Messen Sie mit einem Logiktester den Pegel an den in der folgenden CPU-Anschlüssen.

| RESIN | RESOUT | AD0 | AD1 | AD2 | AD3 | AD4 | AD5 | AD6 | AD7 |

| L |

| RESIN | RESOUT | A8 | A9 | A10 | A11 | A12 | A13 | A14 | A15 | /WR | /RD | IO/!M |

| L | | | | | | | | | |

HINWEIS: Bei richtiger Funktion der CPU muss der Ausgang RESOUT „H-Pegel“ führen, während alle anderen Ausgänge hochohmig sein müssen!

Überprüfung der Adresssignale

Der Mikroprozessor arbeitet ein vorgegebenes Programm immer sequentiell ab, d.h. es wird Befehl nach Befehl abgearbeitet. Bei der überprüfung der AdressIeitungen wird die CPU durch das fest eingestelIte Datenbyte auf der Prüfkarte (SD0-SD7) dazu gezwungen, immer den gleichen 1-Byte-Befehl abzuarbeiten. Das hat zur Folge, dass der gesamte Adressbereich von 0000-FFFF durchlaufen wird und alle Adressen hintereinander auf dem Adressbus erscheinen. Dieser Vorgang wiederholt sich so lange, bis die Betriebsspannung der CPU abgeschaltet wird. Der Programmzähler der CPU wird also ständig um 1 erhöht. Misst man die Adressignale, so müssen zwei benachbarte Leitungen ein Frequenzverhältnis von z.B. fA0 : fA1 = 2:1 aufweisen. Um diesen Sachverhalt zu verdeutlichen, wird die CPU zuerst im STEP-Betrieb betrieben. Stellen Sie den Schalter RUN/HLT der Prüfkarte auf HLT. Mit den Schaltern SD7-SD0 wird das Datenbyte 01111111 = 7F H auf der Prüfkarte eingestellt. Danach wird die CPU durch kurzzeitiges Ausschalten der Betriebsspannung zurückgesetzt.

Messen Sie jetzt die Pegel auf den Adressleitungen A0, A1 und A2 auf der Prüfkarte. Danach betätigen Sie einmal die STEP-Taste und messen wiederum den PegeI auf den genannten AdressIeitungen. Ihre Messergebnisse tragen Sie in die Tabelle auf der nächsten Seite ein.

Meßwerttabelle für den Stepbetrieb

| Step | A2 | A1 | A0 |

|---|---|---|---|

| 0 | L | L | L |

| 1 | L | L | H |

| 2 | L | H | L |

| 3 | L | H | H |

| 4 | H | L | L |

| 5 | H | L | H |

Schalten Sie jetzt den Schalter RUN/HLT der Prüfkarte auf RUN. Die CPU arbeitet den gesamten Adressbereich jetzt mit der Geschwindigkeit der Taktfrequenz ab (siehe Erklärung auf Seite 40). Messen Sie die Adresssignale an den Stecklötösen der Prüfkarte und tragen Sie die Messergebnisse in die folgende Tabelle ein. Achten Sie darauf, dass die Signale immer symmetrisch sein müssen.

Messwerttabel le für den dynamischen Betrieb

| T A0 | 4 µsec | T A1 | 8 µsec |

| T A2 | 16 µsec | T A3 | 32 µsec |

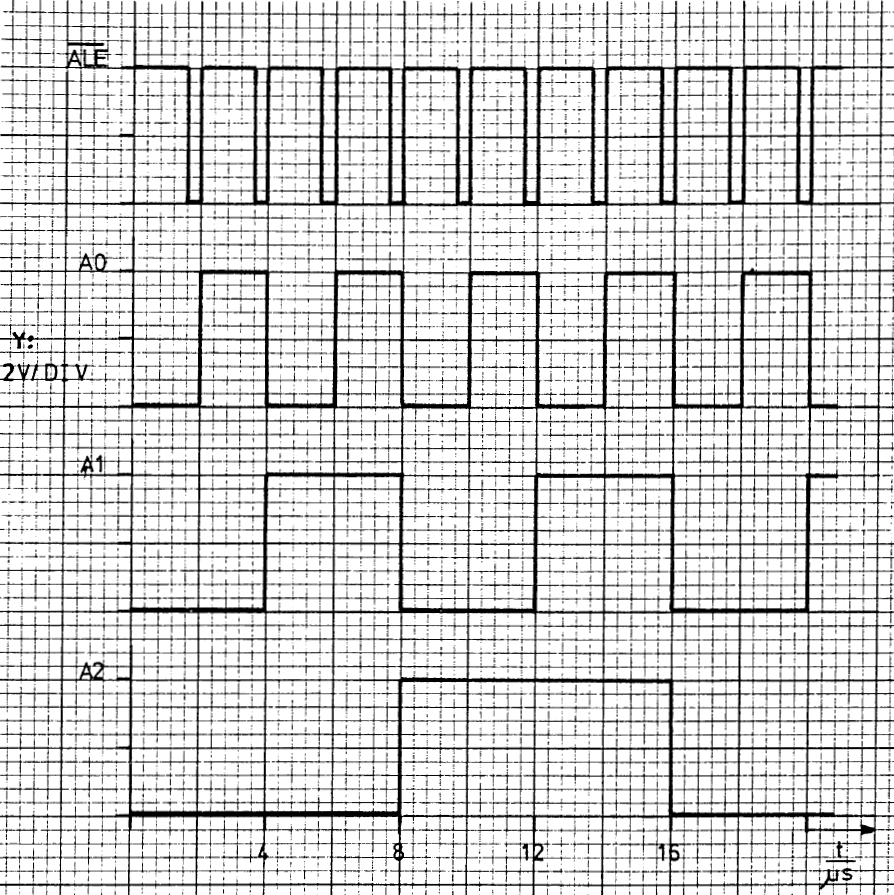

Adresszwischenspeicherung mit HiIfe des ALE-Signals

Wie auf Seite 8 schon beschrieben, besitzt die CPU 8085 nur 16 Anschlüsse für Adressen- und Datensignale. Darum werden die Anschlüsse AD0-AD7 (12-19) im Multiplexbetrieb betrieben. Die 16-Bit-Adresse wird deshalb durch die Bausteine IC3 und IC4 zwischengespeichert. Die Zwischenspeicherung erfolgt immer dann, wenn das ALE-Signale von H auf L wechselt.

Betreiben Sie die CPU wie auf der vorhergehenden Seite dynamisch und messen Sie mit HiIfe des Oszilloskops folgende Signale an den Stecklötösen der Prüfplatine:

ALE= f(t)

A0 = f ( t)

A1 = f(t)

A2 = f ( t)

Ergebnisse zu den Messungen

HINWEIS ZU DEN MEßERGEBNISSEN

Ein Signalwechsel das ALE-Signal auf dem Adressbus findet immer dann statt, wenn einen L-H-Sprung durchführt. Die Triggerung des Oszilloskops erfolgte bei Diagrammen auf der negativen Flanke des Signals A13.

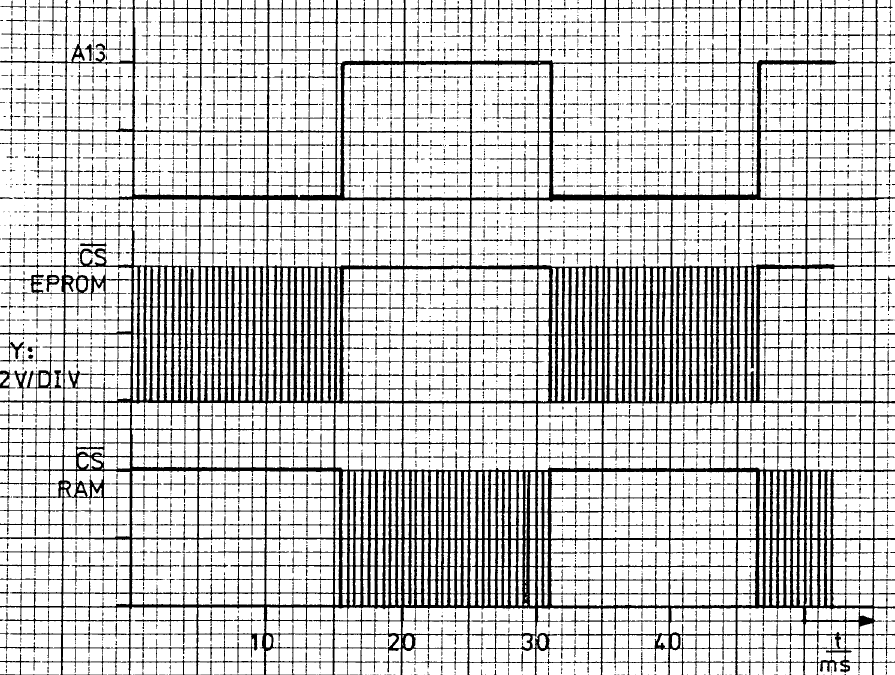

Adressdecodierung für die Speicherbausteine

Wie auf den Seiten 16 und 17 .schon beschrieben, wird der Speicherbereich des Einplatinencomputers in ein EPROM mit 2 oder 4 KByte und ein RAM mit 2 KByte Speicherkapazität unterteilt. Das EPROM wird immer dann angesprochen, wenn die Adressleitung A13 L-Pegel führt, das RAM wird angesprochen, wenn A13 H-Pegel führt. Überprüfen Sie diesen Sachverhalt, indem Sie die Signale der Adressleitung A13 und der beiden CS-Eingänge der Speicherbausteine oszilloskopieren. Die CPU wird genauso betrieben wie auf der vorhergehenden Seite. Die Messergebnisse tragen Sie in die Koordinatensysteme auf dieser Seite ein.

ERGEBNISSE ZU DEN MESSUNGEN VON SEITE 45

HINWEIS ZU DEN MESSUNGEN

Durch die Decodierung der Adressleitung A13 wird das EPROM bei L-Signal dieser Leitung angesprochen, das RAM bei H-Signal auf dieser Leitung. Innerhalb der aktiven Zeit wird der CS-Eingang des jeweiligen Bausteins insgesamt 8191mal angesprochen. Das entspricht z.B. dem Adressbereich 0000-1FFF oder 2000-1FFF. Die Triggerung des Oszilloskops erfolgte auf der negativen Flanke von A13.

Befehls-Abarbeitung durch die CPU

Die Befehlsabarbeitung kann grundsätzlich in zwei Schritte eingeteilt werden:

Befehlsholphase

In dieser Phase Iiest die CPU das Befehlsbyte aus dem Speicher. Das geIesene Byte wird anschIiessend in der CPU decodiert . Sind zur Abarbeitung noch weitere Daten erforderlich, so bewirkt die Ablaufsteuerung, dass diese Daten ebenfalls gelesen werden.

Ausführungsphase

Sind alle Daten zur Ausführung des Befehls bekannt, dann wird der Befehl ausgeführt und anschließend das nächste Befehlsbyte gelesen.

Mit Hilfe der Schalter SD7-SD0 auf der Prüfkarte werden jetzt verschiedene Befehlsbytes fest eingestellt, so daß die CPU imner den gleichen Befehl ausführen muß. Mit Hilfe des Oszilloskops können dann die Steuersignale gemessen und die Arbeitsweise der CPU überprüft werden.

Stellen Sie zuerst das Datenbyte 00101111 = 2F Hein. Dieses Datenbyte entspricht dem 1-Byte-Befehl CMA = Complement Accu.

Oszilloskopieren Sie die auf der nächsten Seite genannten Signale und übertragen Sie die Messergebnisse in die entsprechenden Koordinatensysteme.

HINWEIS: Die Triggerung sollte auf der negativen Flanke von MEMR erfolgen.

Osziloskopieren und zeichnen Sie folgende Signale:

- CLK = f (t)

- !ALE = f ( t)

- !MEMR = f (t)

Alle Signale können auf der Prüfplatine gemessen werden.

HINWEIS ZU DEN MESSUNGEN

Die Beschreibung der Signale bezieht sich auf den im Diagramm gekennzeichneten Zeitpunkt „X“

Zu diesem Zeitpunkt sendet die CPU eine neue Adresse aus, die mit der darauffolgenden positive n Flanke von ALE auf dem Adressbus ansteht . Eine halbe Taktperiode danach wird MEMR aktiviert und das unter der vorher ausgesandten Adresse stehende Befehlsbyte (2F) wird gelesen, entschlüsselt und ausgeführt. Danach beginnt der beschriebene Vorgang erneut.

Stellen Sie jetzt das Datenbyte 11011011 = DBh ein. Diese Datenbyte entspricht dem IN-Befehl

Oszilloskopieren und zeichnen Sie folgende Signale:

- CLK = f ( t)

- ALE = f(t)

- MEMR = f ( t)

Alle Signale können auf der Prüfplatine gemessen werden.

HINWEIS: Die Triggerung sollte auf der positiven Flanke von IOR erfolgen!

ERGEBNISSE ZU DEN MESSUNGEN VON SEITE 50

HINWEIS ZU DEN MESSUNGEN

Die Beschreibung der Signale bezieht sich auf den im Diagramm gekennzeichneten Zeitpunkt „X“

Zu diesem Zeitpunkt sendet die CPU eine neue Adresse aus, die mit der darauf folgenden positiven Flanke von ALE auf dem Adressbus ansteht. Da nach wird MEMR aktiviert und das BefehIsbyte „DB“ wird gelesen und entschlüsselt. Da es sich um den IN-Befehl handelt, muss die CPU noch die Adresse der Eingabeeinheit aus dem Speicher lesen. ALE wird aktiviert (die Portnummer steht immer auf der nächst höheren Adresse des Befehlsbyte) , danach wird MEMR aktiviert und damit sind alle Daten zur Ausführung des Befehls bekannt. Die CPU aktiviert jetzt nochmals das ALE-Signal, um die Adresse der Eingabeeinheit auszusenden. Danach wird die Steuerleitung IOR aktiviert und mit der positiven Flanke dieses Signals dann das Eingabebyte gelesen.

Jetzt muss noch überprüft werden, ob der Einplatinencomputer ein im EPROM abgelegtes Programm richtig abarbeitet und der RAM-Baustein richtig angesprochen wird. Sie benötigen dazu ein komplett aufgebautes MFA-System, das als Entwicklungssystem für das Prüfprogramm dient und das auch zum

Programmieren des EPROM’s dienen soll.

Das MFA-System muss folgende Einschübe enthalten:

- Prozessor 8085

- 8 KByte EPROM mit MAT 85 (Basisadresse 0000)

- 8 kByte RAM (Basisadresse E000)

- Ausgabekarte (Adresse 00)

- Video-Interface

- EPROM-Prograrrrnierkarte

- Spannungsregelung

- Netzteil

Zusätzlich benötigen Sie

- Tastatur

- Monitor

- Gleichspannungsquelle 15 V

- 1 gelöschtes EPROM 2716

Beschalten Sie die Gleichspannungsquelle, die Spannungsregelung und die Programmierkarte nach dem Stromlaufplan auf der nächsten Seite.

Stromlaufplan für die Zusammenschaltung von MFA-Spannungsregelung, Gleichspannungsquelle und EPROM-Programmierkarte

Wie am Anfang dieser Übung bereits beschrieben wurde, soll der Einplatinencomputer ein vorgegebenes Anwenderprogramm abarbeiten. Dieses Programm muss im EPROM des Einplatinencomputers stehen. Die foIgenden Punkte sollen Ihnen deutIich machen, weIche Schritte erforderlich sind, bis dieses Anwenderprogramm auf dem Einplatinencomputer lauffähig ist.

Formulierung der Problemstellung für das Anwenderprogramm

Der Einplatinencomputer solI mit HiIfe des Programms seinen eigenen RAM-Speicherbereich testen und über die Ausgabebaugruppe des MFA-Systems das Testergebnis anzeigen. Das Anwenderprogramm wird auf einem Entwicklungssystem geschrieben

Das MFA-System dient hier als Entwicklungssystem. Das Anwenderprogramm wird mit HiIfe des Assemblercodes in den RAM-Bereich des MFA-Systems eingegeben.

Testphase des Anwenderprogramms auf dem Entwicklungssystem

Über das GO-Kommando wird das Anwenderprogramm gestartet. Der überprüfte RAM-Bereich muss zum einen ausserhalb des Anwenderprogramms Iiegen (das Programm würde sonst durch den Testlauf zerstört), zum anderen muss der überprüfte RAM-Bereich dem des Einplatinencomputers entsprechen (2 KByte). Sollten bei dieser Testphase Fehler im Programmablauf auftreten, lassen sie sich problemlos korrigieren, da das Programm im RAM-Speicher steht.

Das Anwenderprogramm muß auf den EPROM-Adressbereich des Einplatinencomputers zugeschnitten werden

Das Anwenderprogramm wird im MFA-System ab der Adresse E000 abgelegt. Sämtliche Sprungbefehle und Unterprogramme beziehen sich auf diese Anfangsadresse. Auf dem Einplatinencomputer muß das Anwenderprogramm aber mit der Startadresse 0000 beginnen.

Das Anwenderprogramm wird mit Hife eines EPROM-Programmiergerätes in einem EPROM abgelegt. Das MFA-System wird hier zum Programmieren des EPROMs verwendet.

Der Einplatinencomputer wird mit dem programmierten EPROM bestückt. Mit Hilfe einer Anzeige wird überprüft, ob das Anwenderprogramm korrekt abgearbeitet wird. Als Anzeige dient hier die Ausgabebaugruppe des MFA-Systems.

Formulierung der Problemstellung für das Anwenderprograrrm

Das Anwenderprogramm soll einen RAM-Speicherbereich von 2 KByte überprüfen. Es soll außerdem über eine Ausgabebaugruppe anzeigen, ob der getestete Speicherbereich funktionsfähig ist oder nicht.

Der Aufbau des Programms sieht folgendermaßen aus:

- Zuerst wird das Datenwort 55H in die niedrigste Speicheradresse geschrieben und danach aus der gleichen Adresse gelesen. Dann werden geschriebenes und gelesenes Datenwort miteinander

verglichen. Fällt der Vergleich positiv aus, wird das Programm fortgesetzt, ansonsten erfolgt ein Programmabbruch mit entsprechender Anzeige. - Bei Fortsetzung des Programms wird dann das Datenwort AAH in die gleiche RAM-Adresse geschrieben, gelesen und verglichen. Die Reaktion des Programms auf positives oder negatives Ergebnis ist dabei die gleiche wie im ersten Schritt.

- Auf diese Weise werden sämtliche Speicheradressen getestet. Taucht bei einer Adresse ein Fehler auf, wird das Programm abgebrochen und eine Fehlermeldung ausgegeben. Sind alle Speicheradressen in Ordnung, dann erfolgt ebenfalls eine entsprechende Anzeige.

Das Anwenderprogramm wird auf einem Entwicklungssystem geschrieben

Überprüfen Sie vor dem Einschalten des MFA-Systems, ob die auf Seite 52 beschriebenen Einschübe vorhanden sind. Schalten Sie das System ein und rufen Sie nach dem Start des Betriebsprograrrrns den Assembler auf. Danach geben Sie, beginnend bei der Adresse E000 folgendes Programm ein.

LXI SP,27FF ;Stackpointer setzen

LXI H,0E100 ;Anfangsadr. RAM-Bereich

ANF: MVI A,55 ;Datenwort laden

MOV B,A ;Datenwort sichern

MOV M,A ;RAM-Adr. schreiben

MOV A,M ; RAM-Adr. lesen

CMP B ; RAM-Adr. OK?

JNZ STOP ;Nein !

MVI A,0AA ;Ja, inv. Datenwort laden

MOV B,A ; inv. Datenwort sichern

MOV M,A ;RAM-Adr. schreiben

MOV A,M ; RAM-Adr. lesen

CMP B ; RAM-Ad r. OK ?

JNZ STOP ;Nein !

INX H ;Ja, Adr.zaehler erhöhen

MOV A,H ;Zaehlerstand auf

CPI 0E8 ;hoechster RAM1-Adresse?

JNZ ANF ;Nein, naechste Adr. prüfen

ANF1: MVI A,0FF ;Alle

OUT 00 ;RAM-Adressen

CALL ZEIT ;sind in

MVI A,00 ;Ordnung

OUT 00

CALL ZEIT

JMP ANF1

STOP: MVI A,055 ;Eine RAM-Adr. ist

OUT 00 ;nicht in

JMP STOP ;Ordnung

ZEIT: MVI B,0F ;Zeitschleife

Z1: LXI D,1999 ; ca. 1 sec.

Z2: DCX D

MOV A,E

ORA

JNZ Z2

DCR B

JNZ Z1

RET

Testphase des Anwenderprograrrms auf dem Entwicklunssystem

Bei diesem Testlauf ist folgendes zu beachten:

Der erste Befehl LXI SP,27FF soll nachher den Stackpointer des EinpIatinencomputers definiert auf die höchste RAM-Adresse setzen. Dieser Befehl darf beim Testlauf im MFA-System nicht abgearbeitet werden!

DAS PROGRAMM IST DESHALB IM MFA-SYSTEM AB DER ADRESSE E003 ZU STARTEN!

Außerdem wurde das H-L-Register so geIaden, dass sich das Programm beim Testlauf nicht selber zerstört.

Starten Sie jetzt das Programm mit dem GO-Befehl ab der Adresse

E003

Ist das Programm in Ordnung (die LED’s der Ausgabebaugruppe müssen im Sekundentakt blinken), kann das EPROM für den Einplatinencomputer programmiert werden.

Das Anwenderprogramm muss auf den EPROM-Adressbereich des Einplatinencomputers zugeschnitten werden

Das Anwenderprogramm muss für den Einplatinencomputer ab der Adresse 0000h lauffähig sein. Deshalb sind die in folgender Liste aufgeführten Adressen zu ändern. Die Änderung Iässt sich am einfachsten mit dem „Memory“-Kommando des MFA-Betriebssytems durchführen.

Liste der zu ändernden Befehle

| Adresse | Alter Befehl | Geänderter Befehl |

|---|---|---|

| E003 | LXI H,E100 | LXI H,2000 |

| E00C | JNZ E030 | JNZ 0030 |

| E015 | JNZ E030 | JNZ 0030 |

| E01A | CPI E8 | CPI 28 |

| E01C | JNZ E006 | JNZ 0006 |

| E023 | CALL E037 | CALL 0037 |

| E02A | CALL E037 | CALL 0037 |

| E02D | JMP E01F | JMP 001F |

| E034 | JMP E030 | JMP 0030 |

| E03F | JNZ E03C | JNZ 003C |

| E043 | JMP E039 | JMP 0039 |

Das Anwenderprogramm wird mit Hilfe eines EPROM-Programmiergerätes in einem EPROM abgelegt

Überprüfen Sie, ob das EPROM-Programmiergerät im MFA-System und und die zusätzliche Spannungsquelle richtig miteinander verbunden sind.

Danach wird ein gelöschtes EPROM 2716 in die Fassung des Programmiergerätes gesteckt und das Programmierprogramm mit der Adresse 1E06 (GO) gestartet. Nach dem Aufruf erscheint auf dem Bildschirm folgender Ausdruck:

- TEST

- READ

- PROG

- COMP

- QUIT

Zuerst muss das eingesteckte EPROM auf richtige Funktion getestet werden. Dazu „T“ eingeben. Ist das EPROM in Ordnung, erscheint auf dem Bildschirm der Ausdruck „READY“.

Danach „P“ eingeben. Jetzt wird die Startadresse der zu programmierenden Daten abgefragt. Geben Sie „E000“ ein. Das EPROM wird jetzt programmiert. Dieser Vorgang dauert ca. 2 Min.

Der EinpIatinencomputer wird mit dem programmierte EPROM bestückt. Mit Hilfe einer Anzeige wird überprüft , ob das Anwenderprogramm korrekt abgearbeitet wird Schalten Sie jetzt die Betriebsspannung am Einplatinencomputer ab und entfernen Sie die Prüfplatine. Danach wird der Einplatinencomputer mit EPROM und RAM bestückt.

Um die richtige Funktion des Einplatinencomputers zu überprüfen, wird er mit der Ausgabe-Baugruppe zusammen im MFA-System betrieben. Schalten Sie das MFA-System und die zusätzliche Gleichspannungsquelle aus und entfernen Sie außer der Ausgabebaugruppe, der SpannungsregeIung und dem NetzteiI alle Einschübe. Danach schieben Sie den Einplatinencomputer in das MFA-System und schalten das System wieder ein.

Der Einplatinencomputer arbeitet jetzt das im EPROM befindliche Programm ab. Da die Abarbeitung sehr schnell erfolgt, werden Sie schon nach kurzer Zeit eine entsprechende Reaktion an der Ausgabebaugruppe feststellen.

Damit ist die Übung beendet!