Einleitung

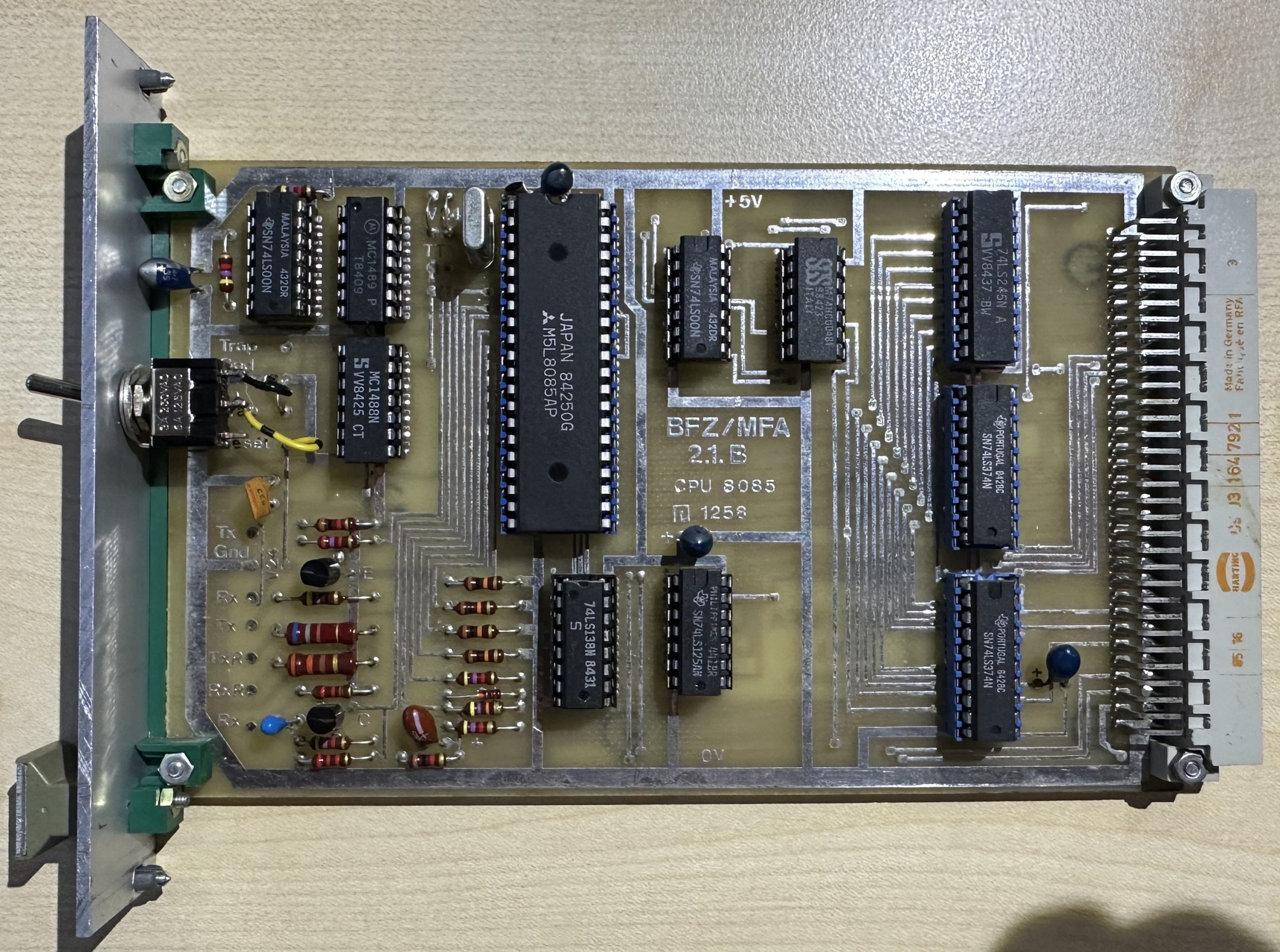

Die CPU hat die Aufgabe, im Speicher abgelegte Befehle auszuführen sowie Daten zu verarbeiten, z.B. Addieren von Zahlen, Ausgeben von Ergebnissen, Verknüpfen von Daten. Die zur Bewältigung dieser Aufgabe nötigen Funktionsgruppen befinden sich in der CPU; siehe Bild 46.

Zum Einholen von Befehlen (was ist zu tun?) und Daten (womit?) aus dem Speicher gibt die CPU eine 16-Bit-Signalkombination (Adresse) auf den Adreßbus.

Mit einem Steuersignal veranlaßt sie dann, daß der Inhalt der adressierten Speicherstelle über den Datenbus in die CPU gelangt. Die anschließende Verarbeitung der Daten erfolgt CPU-intern.

Die Ausgabe von Daten geschieht entsprechend: Adresse ausgeben – Steuersignal ausgeben – Daten ausgeben.

Zwischen der CPU und dem Systembus befinden sich die Treiber (teilweise mit Zwischenspeicher) für die Adreß-, Daten- und Steuersignale. Bei der CPU 8085 ist es nötig, die unteren acht Bit (low-Byte) einer von der CPU ausgesendeten Adressezwischenzuspeichern, da dieser Teil des Busses auch für den Datentransport benutzt wird. Die oberen acht Bit (high-Byte) des Adreßbusses (CPU-seitig) werden nur für den Adressverkehr benutzt. Sie werden zwischengespeichert, um die CPU-Ausgänge zu entlasten.

Die Übernahme der Adressen in die Speicher bzw. Treiber wird mit dem CPU-Signal ALE gesteuert (ALE= address latch enable).

Da die Daten nach der Ausgabe der Adresse auf dem für beide benutzten Busteil der Baugruppe verkehren, brauchen sie nicht zwischengespeichert zu werden. Der Datenbustreiber muss jedoch Datenverkehr in zwei Richtungen zulassen. Gesteuert wird die Datenflussrichtung durch die Steuersignale RD und INTA.

Bild 46: Das Blockschaltbild der CPU-Baugruppe

Die Schaltung der CPU-Baugruppe

Mit den Steuersignalen RD, IO/M und WR meldet die CPU, ob sie Lesen oder Schreiben will, und zwar in oder aus Speicherstellen oder Ein/Ausgabe-Geräte. Im Steuersignal-Decoder werden diese Signale decodiert und umgewandelt in die Sy- stem-Steuersignale MEMR Speicherstelle lesen MEMW in Speicherstelle einschreiben IOR Eingabebaugruppe lesen IOW in Ausgabebaugruppe einschreiben

Über das CPU-Signal HLDA lassen sich die Daten-, Adreß- und Steuer-Bustreiber in den hochohmigen Zustand schalten.

Alle übrigen Steuersignale sind nur gepuffert; sie sind also nicht vom Bus trennbar.

Über die Interrupt-Steuerleitungen kann die CPU veranlaßt werden, ihre momentane Programmbearbeitung zu unterbrechen, um ein vorrangiges Programm zu bearbeiten.

An die serielle Schnittstelle kann ein Datensichtgerät oder ein Fernschreiber (TTY) angeschlossen werden.

Mit der Reset-Taste wird die CPU veranlaßt, ihre Programmabarbeitung bei dem Speicherplatz mit der Adresse 0000H zu beginnen.

Der 4-MHz-Quarz erzeugt CPU-intern ein Rechtecksignal mit einer Taktperiodendauer von 500 ns (interne Teilung durch 2). Mit Hilfe dieses Taktes werden alle Arbeitsschritte der CPU gesteuert.

Die CPU-Baugruppe steuert mit Hilfe der beiden Speicherbaugruppen EPROM (Lesespeicher) und RAM (Schreib-Lese-Speicher) die Funktion des gesamten Mikrocomputers. Über eine Datensichtstation sowie Eingabe- und Ausgabe-Baugruppen kann der Mensch oder eine Maschine Verbindung mit dem Mikrocomputer aufnehmen.

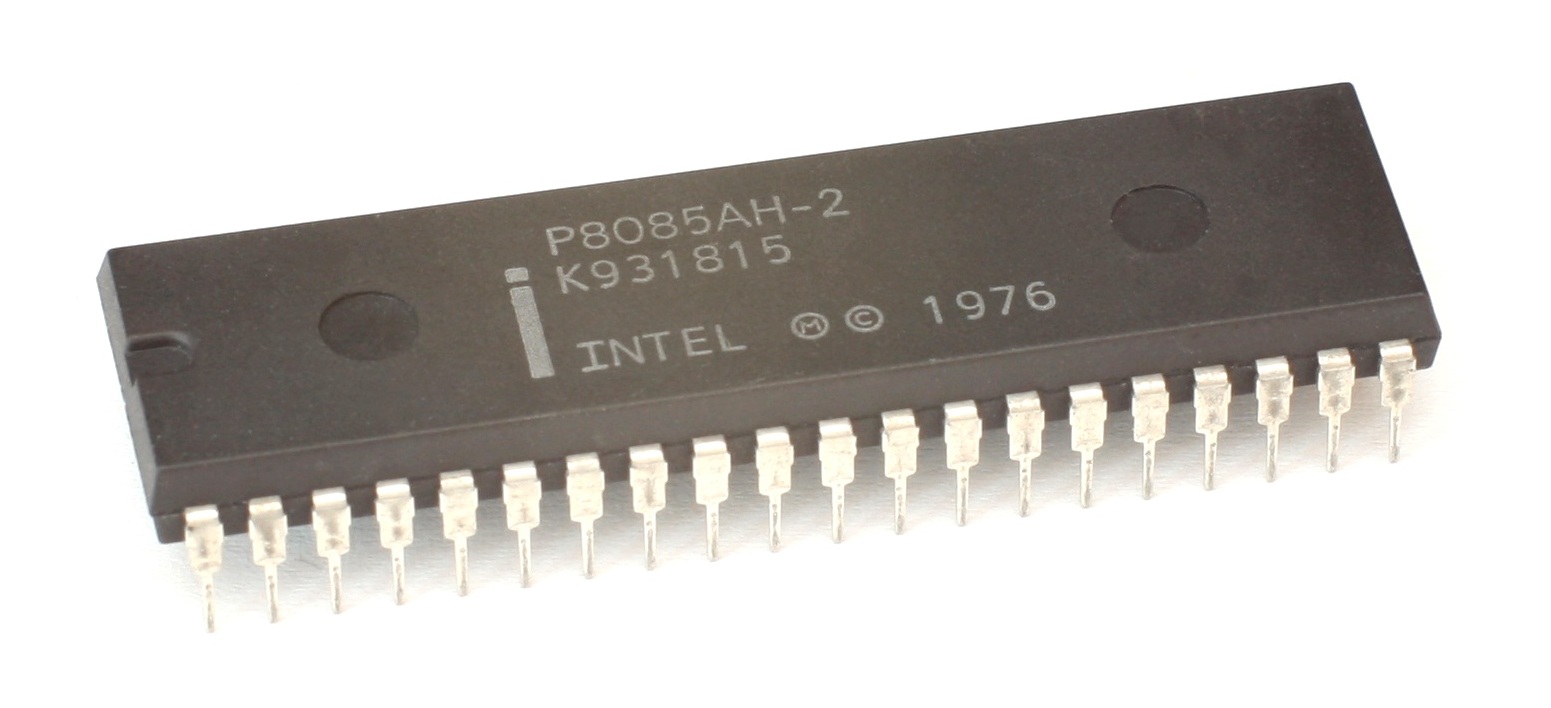

Den Kern der CPU-Baugruppe stellt die CPU 8085A dar (CPU= Central Processing Unit = zentrale Prozessor-Einheit); man nennt sie auch Mikroprozessor. Sie übernimmt die eigentlichen Steuer- und Rechenvorgänge; hierzu benötigt sie noch einige Hilfsbausteine, deren Funktionen im folgenden erklärt werden. Der innere Aufbau der CPU aus Registern, Akkumulator arithmetischer logischer Einheit usw. wurde in den Kapiteln 1 und 2 erklärt.

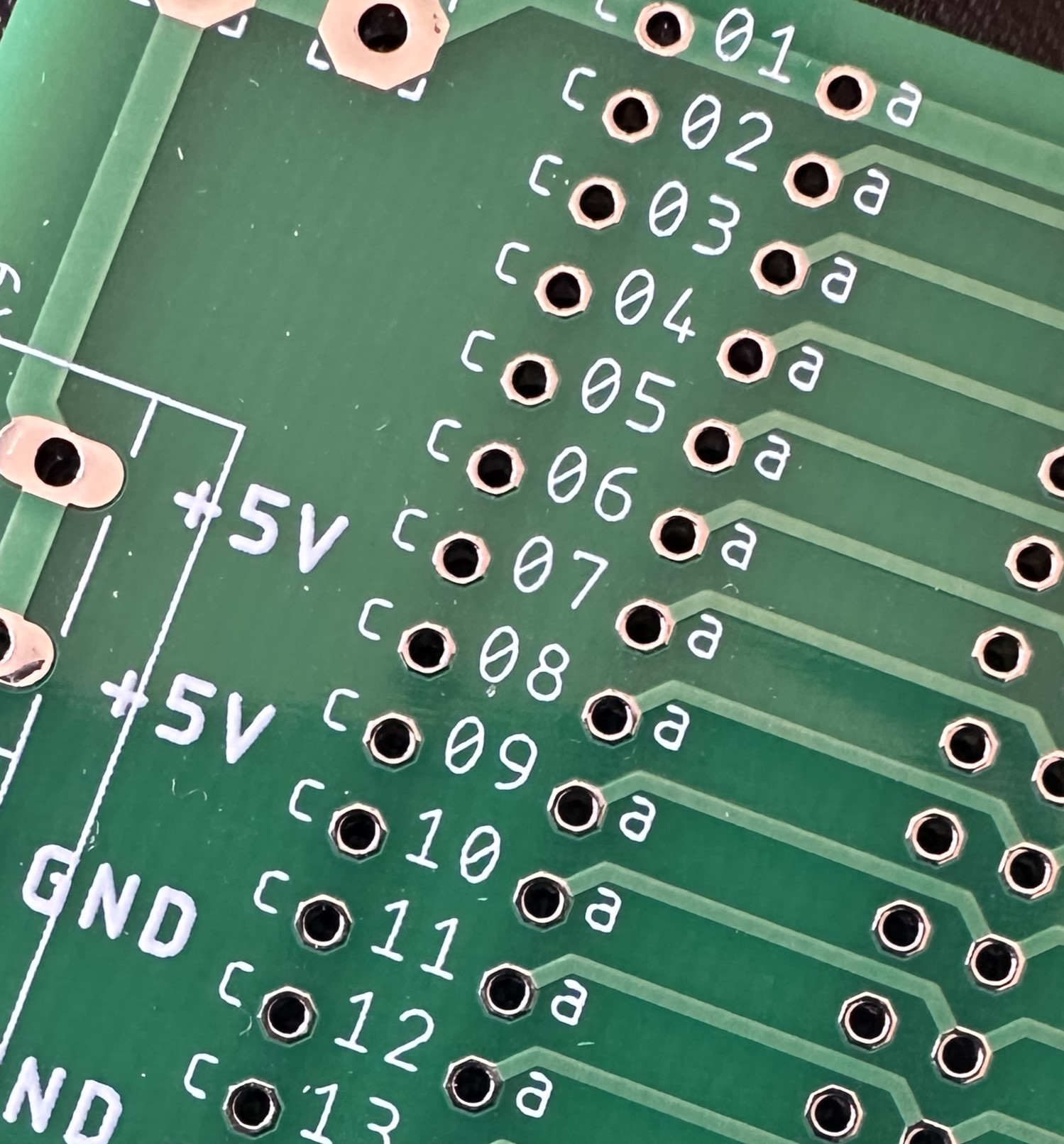

Durch die verwendete CPU ist die Anzahl der Leitungen von Adreß- und Daten-Bus festgelegt. Der 8085 verfügt über einen 16-Bit-Adreß-Bus und einen 8-Bit-Daten-Bus.

Mit den 16 Adressleitungen kann die CPU maximal 2^16 = 65.536 Speicherplätze mit einer Datenbreite von 8 Bit (1 Byte) adressieren.

Der Befehlssatz ist durch die CPU ebenfalls fest vorgegeben. Mit dem 8085 vergleichbare Mikroprozessoren sind zum Beispiel der 8080 von INTEL (der Vorgänger des 8085), der 6500 von Rockwell, der 6800 von Motorola und der Z80 von Zilog. Sie alle gehören zur Gruppe der 8-Bit-Mikroprozessoren, d. h. sie verfügen über einen 8-Bit-Daten-Bus. Im Handel erhältlich sind inzwischen auch Weiterentwicklungen der genannten Prozessortypen mit einem 16-Bit-Daten-Bus.

Bild 47 zeigt den Stromlaufplan der Baugruppe. Sie sollten ihn bei allen folgenden Schaltungserklärungen zur Orientierung heranziehen.

Die Arbeitsweise des Prozessors

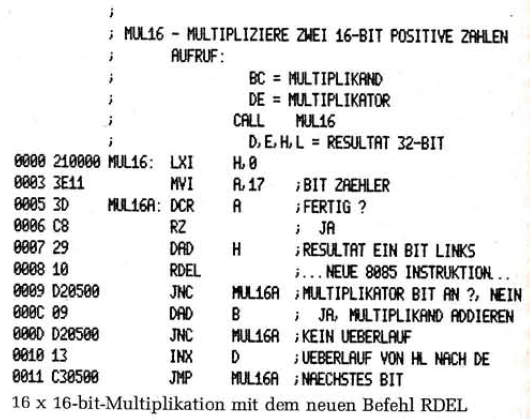

Der Prozessor bearbeitet Befehle nach einem fest vorgegebenen Arbeitstakt. Seine Arbeitsgeschwindigkeit wird durch diesen Takt bestimmt. Die zu bearbeitenden Befehle müssen dem Prozessor über ein Programm mitgeteilt werden, das in einem Speicher in binärer Form abgelegt ist. Die CPU 8085 »versteht« 93 verschiedene Befehle; sie bilden den Befehlssatz des Prozessors. Ein Befehl kann aus einem Byte (8 Bit), aber auch aus zwei oder aus drei Bytes bestehen. Das Flussdiagramm in Bild 48 zeigt, wie solche Befehle abgearbeitet werden.

Bild 48: Ein einfaches Flussdiagramm zur Befehls-Abarbeitung.

Zu 1:

Nach dem Starten eines Programms holt sich der Prozessor ein Befehlsbyte (Operationscode, kurz Op-Code genannt) aus dem Speicher in ein internes 8-Bit-Register, das Befehlsregister. Der Speicherplatz wird dabei durch ein 16-Bit-Register, den Befehlszähler (Program Counter, kurz PC) adressiert.

Zu 2:

Der Prozessor entschlüsselt (decodiert) dieses erste Byte und steuert entspre- chend den weiteren Ablauf.

Zu 3:

Handelt es sich um einen 1-Byte-Befehl, der also keine weiteren Daten oder Adressen benötigt, so erhöht der Prozessor den Befehlszähler und führt den Befehl aus.

Beispiel für einen 1-Byte-Befehl: Bilde das Komplement vom Inhalt des Registers A (Akkumulator, kurz Akku), d. h. jede 1 des im Akku stehenden Bytes wird durch eine Oersetzt und umgekehrt (mnemonisch = leichter merkbar).

| Mneomonischer Code | Hexadezimaler Code | Binär Code |

| CMA | 2F | 0010 1111 |

Aufgrund dieses einen Befehlsbytes kann der Prozessor .den Befehl ausführen.

Zu 4:

Benötigt der vom Prozessor geholte Befehl weitere Angaben, wie zum Bei- spiel einen zum Befehl gehörenden Operanden, so erhöht er zuerst den Befehlszähler, holt dann den Operanden und führt anschließend den Befehl aus.

Beispiel für einen 2-Byte-Befehl: Verknüpfe das im Akku stehende Byte mit dem zweiten Byte des Befehls UND. Das zweite Byte wird hier mit 80 (hexadezimal) gewählt.

| Mneomonischer Code | Hexadezimaler Code | Binär Code |

| ANO 80 1. Byte Operationscode 2. Byte Operand | E6 80 | 1110 0110 1000 0000 |

Außer dem Operationscode ANI (E6) benötigt der Prozessor noch eine Bit- kombination (Operand, hier 80H), mit der er den Akkumulator-Inhalt UND- verknüpfen soll.

Zu 5:

Folgt dem ersten Befehlsbyte eine Speicheradresse (2 Byte), so muß der Prozessor den Befehlszähler zweimal erhöhen und das jeweilige Adreß-Byte holen, um danach den Befehl ausführen zu können.

Beispiel für einen 3-Byte-Befehl: Springe (JUMP) zur angegebenen Adresse, nämlich F800H

| Mneomonischer Code | Hexadezimaler Code | Binär Code |

| JMP F8 00 1. Byte Operationscode 2. Byte 1. Operand (höherwertiges Adressbyte) 3. Byte 2. Operand (niederwertiges Adressbyte) | C3 00 F8 | 1100 0011 0000 0000 1111 1000 |

Wie das Beispiel zeigt, folgt in der hexadezimalen und in der binären Darstellung des Befehls dem Operationscode zuerst das niederwertige und dann das höherwertige Byte der Speicheradresse. In dieser Reihenfolge muß eine zum Befehl gehörende Adresse im Speicher stehen.

Zu 6:

Beispiel für die Ausführung des Befehls CMA:

Angenommener Akku-Inhalt vor der Befehlsausführung: 0110 1101

Akku-Inhalt nach der Befehlsausführung: 1001 0010

Jedes Bit des Akkumulators ist durch den Befehl CMA invertiert worden.

Die Taktsteuerung

Die CPU besitzt einen internen Taktoszillator, dessen Frequenz von einem außen angeschlossenen 4-MHz-Quarz abgeleitet wird. Er halbiert die vom Quarz gelieferte Taktfrequenz und formt sie in ein Rechtecksignal um.

Nach dem so gewonnenen 2-MHz-Takt, der als Systemtakt dient, laufen alle Vorgänge in der CPU ab. Gleichzeitig steht der Systemtakt am Ausgang »CLK OUT« (CLOCK OUT) für weitere Anwendungen im Mikrocomputer zur Verfügung (Bild 49). Rechts im Bild sind die Oszillogramme der Eingangs- und Ausgangs-Taktfre- quenz und die Meßpunkte an der CPU angegeben.

Bild 49: Takt-Erzeugung und oszillografische Darstellung des Taktes.

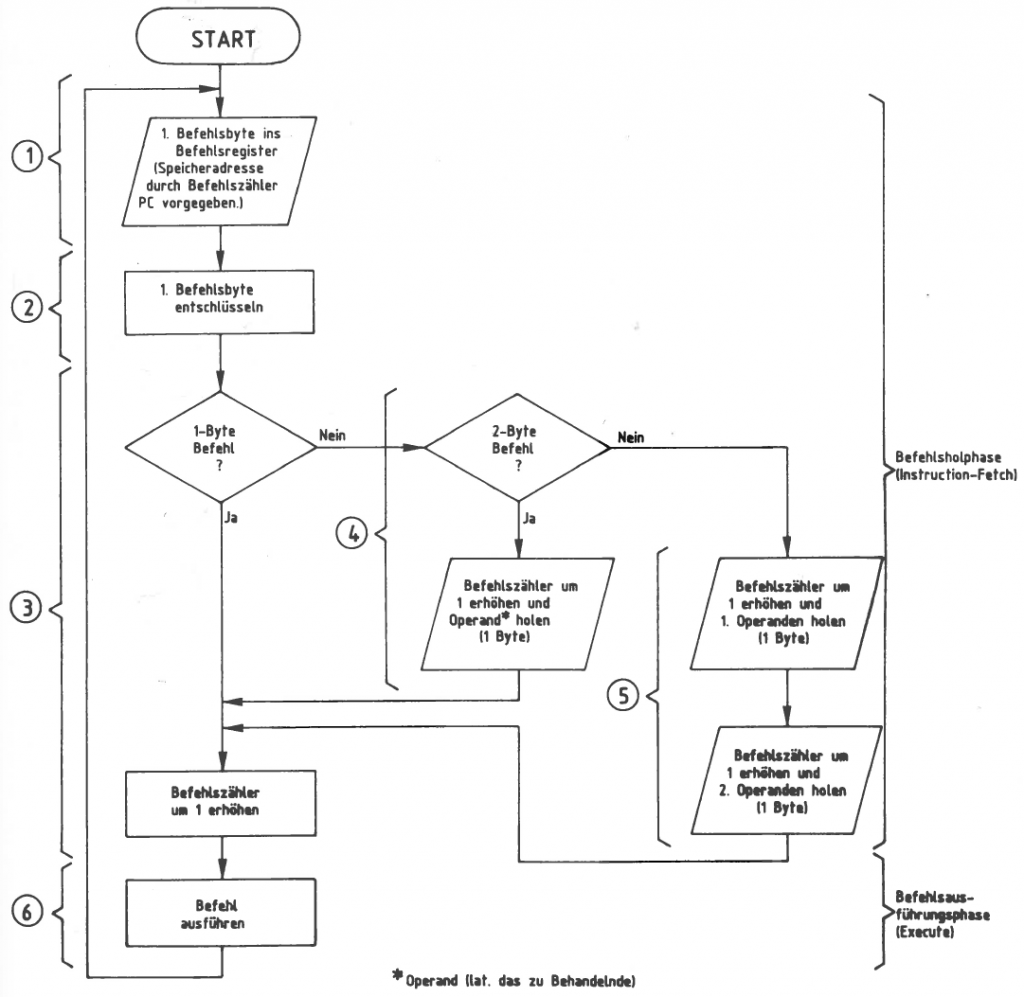

Wie schon im Flussdiagramm (Bild 48) zu sehen war, unterteilt sich die Abarbeitung eines Befehls in zwei Phasen:

- Befehlsholphase (instruction fetch),

- die Befehlsausführungs-Phase (execute).

Beide Befehlsphasen stehen in zeitlichem Zusammenhang zum Systemtakt.

Jede Befehls-Abarbeitung beginnt mit der Befehlsholphase. Bild 50 zeigt den Verlauf einiger wichtiger Signale der Befehlsholphase. Die Abarbeitung erfolgt während der Taktzyklen Tl bis T4.

Bild 50: Der Signalverlauf »Befehl holen und entschlüsseln« (Befehlsholphase).

Beschreibung des Signalverlaufes von Bild 50:

Takt T1:

Während dieser Zeit gibt der Prozessor die Adreßsignale aus. Das niederwertige Adress-Byte steht auf den Leitungen AD0 … AD7 nur etwa während eines Taktes zur Verfügung, weil diese Leitungen auch zum Datentransport verwendet werden. Mit Hilfe des ALE-Signals wird deshalb die ausgegebene Adresse zwischengespeichert.

Takt T2:

Das Steuersignal »Lesen« (RD, aktiv low) wird ausgegeben. An den Adress-/Daten-Anschlüssen AD0…AD7 liegen nun die Daten (der Be- fehl) aus dem adressierten Speicherplatz an.

Takt T3:

Innerhalb von T3 liest der Prozessor das dann stabil anstehende Befehls- byte ein.

Takt T4:

Das Lesesignal ist nicht mehr aktiv. Der Prozessor entschlüsselt jetzt den gelesenen Befehl.

Die Abarbeitung eines Befehls erfolgt schrittweise; z.B. wird bei einem 2-Byte-Befehl zuerst das erste und dann das zweite Befehls-Byte geholt und schließlich der Befehl ausgeführt. Man nennt diese Schritte auch Maschinenzyklen. Sie sind aus Takten oder Taktzyklen aufgebaut. Ein Maschinenzyklus zum Holen des Operationsteils eines Befehles (1. Befehls-Byte) besteht z.B. aus vier Takten.

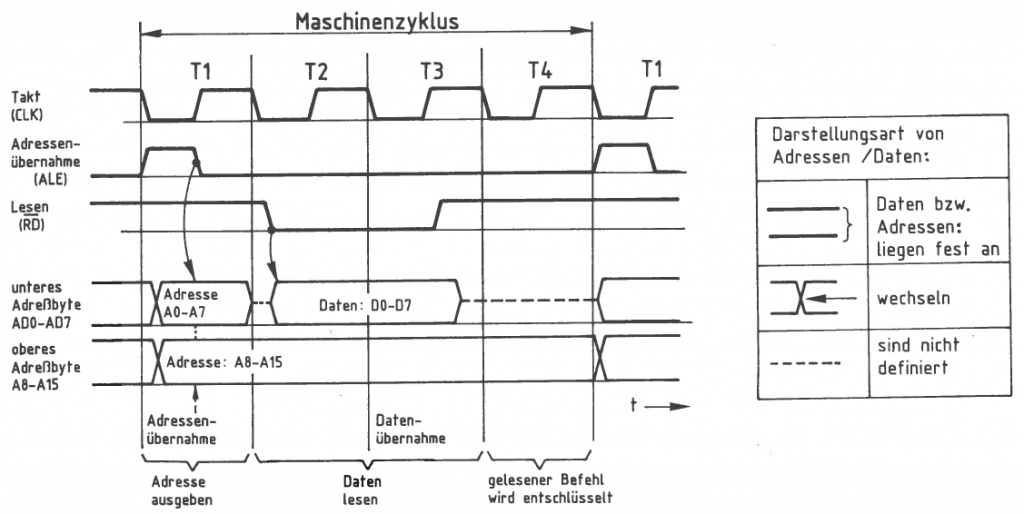

Bild 51 zeigt anhand des 2-Byte-Befehls IN XX (Daten von einer Eingabe-Baugruppe mit der Adresse XX lesen) den Signalverlauf für den gesamten Befehl.

Bild 51: Der Verlauf der Steuer-, Adress- und Datensignale für den Befehl IN XX; dabei steht XX für die hexadezimal angegebene Adresse der Eingabe-Baugruppe.

Beschreibung des Signalverlaufes aus Bild 51:

Der Signalverlauf ist in drei Maschinenzyklen unterteilt und diese wiederum in einzelne Takte.

Maschinenzyklus 1 (Ml):

Der Befehl »IN« wird geholt.

Dies entspricht dem Vorgang in Bild 50. Das hinzugekommene Steuersignal IO/M (Input-Output/Memory = Eingabe-Ausgabe/Speicher) zeigt durch L-Pegel an, daß der Befehl aus dem Speicher geholt wird.

Maschinenzyklus 2 (M2):

Die Adresse der Eingabe-Baugruppe wird geholt.

Tl:

Die Speicheradresse, unter der die Adresse der Eingabe-Baugruppe gespeichert ist, wird ausgegeben und zwischengespeichert mit dem H/L- Sprung auf der ALE-Leitung.

T2 u. T3:

Die CPU liest mit dem low-aktiven Signal READ (RD) die Adresse der Eingabe-Baugruppe aus dem adressierten Speicherplatz.

Maschinenzyklus 3 (M3):

Das Datenbyte wird von der Eingabe-Baugruppe geholt (Befehlsausführung).

T1:

Die CPU schaltet die zuvor gelesene Adresse der Eingabe-Baugruppe nun auf den Adreßbus. Der H-Pegel auf der IO/M-Leitung bedeutet, daß mit der Adresse eine Eingabe-Baugruppe und kein Speicherplatz angesprochen wird.

T2 und T3:

Die CPU übernimmt das an der Eingabe-Baugruppe anstehende Daten- byte. Während dieser Zeit führt die Steuerleitung READ L-Pegel.

Während der gesamten Befehlsphase hat das Signal WR (WRITE = Schreiben) H-Pegel und ist damit nicht aktiv. Bei Befehlen, die der CPU Anweisungen zum Schreiben von Daten in einen Speicher bzw. an eine Ausgabe-Baugruppe geben, wird das WRITE-Signal aktiv (L-Pegel). Der Beginn eines jeden neuen Maschinenzyklus wird durch H-Pegel des ALE-Signals angezeigt.

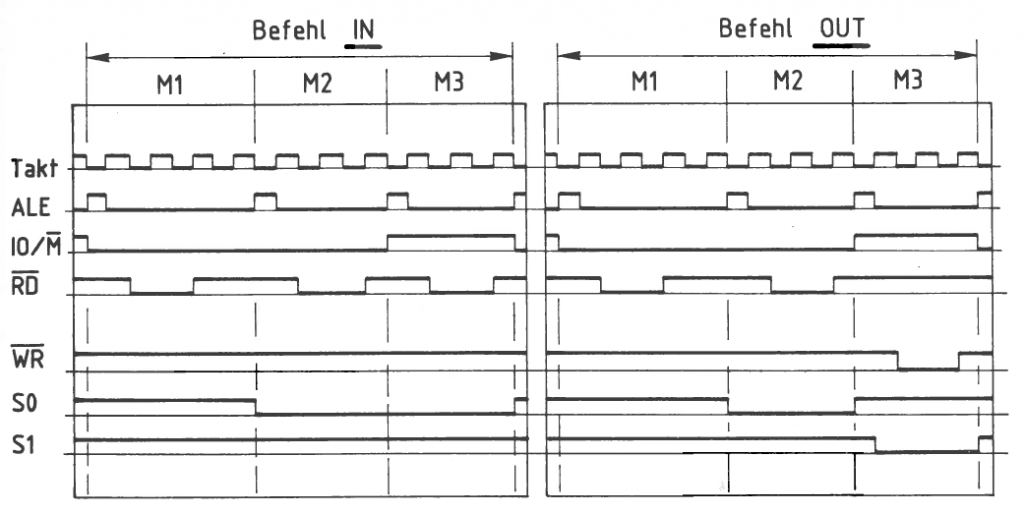

Für den Befehl IN sind die oben besprochenen Signalverläufe (ohne Adress- und Datensignale) an den jeweiligen CPU-Anschlüssen oszilloskopiert und in Bild 52 links dargestellt. Zum Vergleich zeigt Bild 52 rechts die Signalverläufe für den Befehl OUT, der Daten an eine Ausgabe-Baugruppe übermittelt

Bild 52: Steuersignale: links für den Befehl IN, rechts für den Befehl OUT.

Bis auf RD (Lesen) und WR (Schreiben) im Maschinenzyklus M3 sind die aufgenommenen Steuersignale gleich. Beim OUT-Befehl bleibt RD im dritten Maschinenzyklus auf H-Pegel, und WR geht auf L-Pegel; beim IN-Befehl sind die Pegelwerte umgekehrt.

Anhand der beiden Oszillogramme ist gut zu erkennen, wie und wann die CPU mit Hilfe der drei Steuersignale (IO/M, RD und WR) Baugruppen des Mikrocomputers anspricht.

Die Zustandsanzeige-Signale S0,S1

Über die beiden Steuersignale S0 und S1 zeigt die CPU ihren momentanen Tätigkeitszustand (Status) an. Um das zu verdeutlichen, sind in Bild 53 zusätzlich zu den in Bild 52 aufgenommenen Steuersignalen des IN- und OUT-Befehls die Signale S0 und S1 dargestellt.

Bild 53: Die Steuersignale beim IN- und beim OUT-Befehl mit den Status-Signalen S0 und S1

| Maschinenzyklus | Tätigkeit der CPU | Zustandssignal S1 | Zustandssignal S0 |

|---|---|---|---|

| M1 | Befehl aus dem Speicher lesen | H | H |

| M2 | Adresse der Eingabe-Baugruppe aus dem Speicher lesen | H | L |

| M3 | Datenbyte der Eingabe- Baugruppe lesen | H | L |

Mit dem H-Pegel an Sl signalisiert die CPU einen Lesevorgang. Führt SO gleichzeitig H-Pegel, so wird angezeigt, daß die CPU einen Befehl liest (instruction-fetch-Zyklus). Der gleichzeitige H-Pegel von SO und Sl wird benutzt, um auf der Baugruppe »Bus- Signalanzeige« die Befehlsholphase mit einer Leuchtdiode anzuzeigen. Zur Bus-Signalanzeige.

| Maschinenzyklus | Tätigkeit der CPU | Zustandsignal S1 | Zustandssignal S0 |

|---|---|---|---|

| M1 | Befehl aus dem Speicher lesen | H | H |

| M2 | Adresse der Eingabe-Baugruppe aus dem Speicher lesen | H | L |

| M3 | Datenbyte der Eingabe-Baugruppe schreiben | L | H |

Bei den Maschinenzyklen Ml und M2 stimmen die Zustandssignale beim OUT-Befehl mit denen beim IN-Befehl überein. Mit Beginn von M3 geht das Signal SO -auf H-Pegel. Zwischen den beiden ALE-Impulsen wechselt dann das Signal Sl auf L-Pegel, wodurch der im dritten Maschinenzyklus stattfindende Schreibvorgang angezeigt wird.

Außer der Anzeige der drei Tätigkeits-Zustände »Befehl lesen«, »Lesen« und »Schreiben« ist mit den zwei Signalen SO und Sl noch eine weitere Anzeige möglich, die den Halt-Zustand der CPU signalisiert. In der folgenden Tabelle sind die Zustände von SO und S1 zusammengefaßt.

| Tätigkeit der CPU | Signal S1 | Signal S0 |

|---|---|---|

| Halt | L | L |

| Schreiben | L | H |

| Lesen | H | L |

| Befehl lesen | H | H |

Rücksetzen und Starten des Prozessors

Durch Anlegen eines L-Pegels an den Eingang RESET IN (Rücksetz-Eingang) der CPU ist es möglich, den internen Befehlszähler auf 0000 (hexadezimal) zu setzen. Nimmt der Eingang wieder H-Pegel an, startet die CPU, indem sie die Adresse 0000H aussendet. Das Rücksetzen kann auf zwei Arten erreicht werden:

Automatischer Start nach dem Einschalten der Vorsorgungsspannung

Nach dem Einschalten lädt sich der Kondensator C3 über den Widerstand R18 auf; siehe Bild 54. Die CPU wird so lange angehalten, bis die Spannung am Kondensator die Umschaltschwelle (ca. 2,4 V) des in der CPU befindlichen Schmitt-Triggers erreicht hat. Diese kurze Verzögerungszeit ist nötig, damit sich die Versorgungsspannung aufbauen und stabilisieren kann und dadurch ein einwandfreies Arbeiten der CPU gewährleistet ist.

Bild 54: Zurücksetzen der CPU

Rücksetzen (Neustart) während des Betriebes des Prozessors

Mit dem Taster S2 ist es jederzeit möglich, ein Rücksetzsignal zu erzeugen. Bei Betätigung von S2 entlädt sich der Kondensator über den Widerstand R14. An RESET IN liegt für die Zeit der Betätigung von S2 L-Pegel, und die CPU arbeitet nicht. Durch Öffnen von S2 wird C3 über R18 wieder aufgeladen, und die CPU nimmt die Arbeit ab Adresse 0000H wieder auf.

Für Bild 55 wurde dieser Vorgang mit einem Oszilloskop aufgenommen. Am zusätz- lich dargestellten Signal ALE kann man den Zeitpunkt der Arbeitsaufnahme der CPU erkennen. Da die ALE-Impulse im μs-Bereich liegen -im Gegensatz zur eingestellten Zeitablenkung des Oszilloskops (100 ms/Div.) – ist nur der Beginn dieser Impulse als L-H-Sprung erkennbar.

Bild 55: RESET-IN- und ALE-Signalverlauf beim Betätigen der Reset-Taste.

Die beschriebene Rücksetzmöglichkeit dient im wesentlichen bei Programm- oder Bedienungsfehlern dazu, den Prozessor wieder unter Kontrolle zu bringen.

Die Pufferung der CPU-Ausgänge

Jeder Ausgang der CPU 8085 kann mit nur einem TTL-Eingang belastet werden. Dies genügt jedoch in MC-Systemen nicht. Bei der Adressierung z.B. von Speicherbausteinen müssen viele Eingänge angesteuert werden, weil alle Speicher parallel geschaltet sind. Zwischen CPU, Speichern und Ein/Ausgabe-Bausteinen müssen deshalb Verstärker geschaltet werden, die größere Ausgangsströme liefern und die Ansteuerung mehrerer Eingänge zulassen. Solche Verstärker nennt man Treiber oder Puffer; sie schützen außerdem die CPU bei Kurzschlüssen auf dem System-Bus

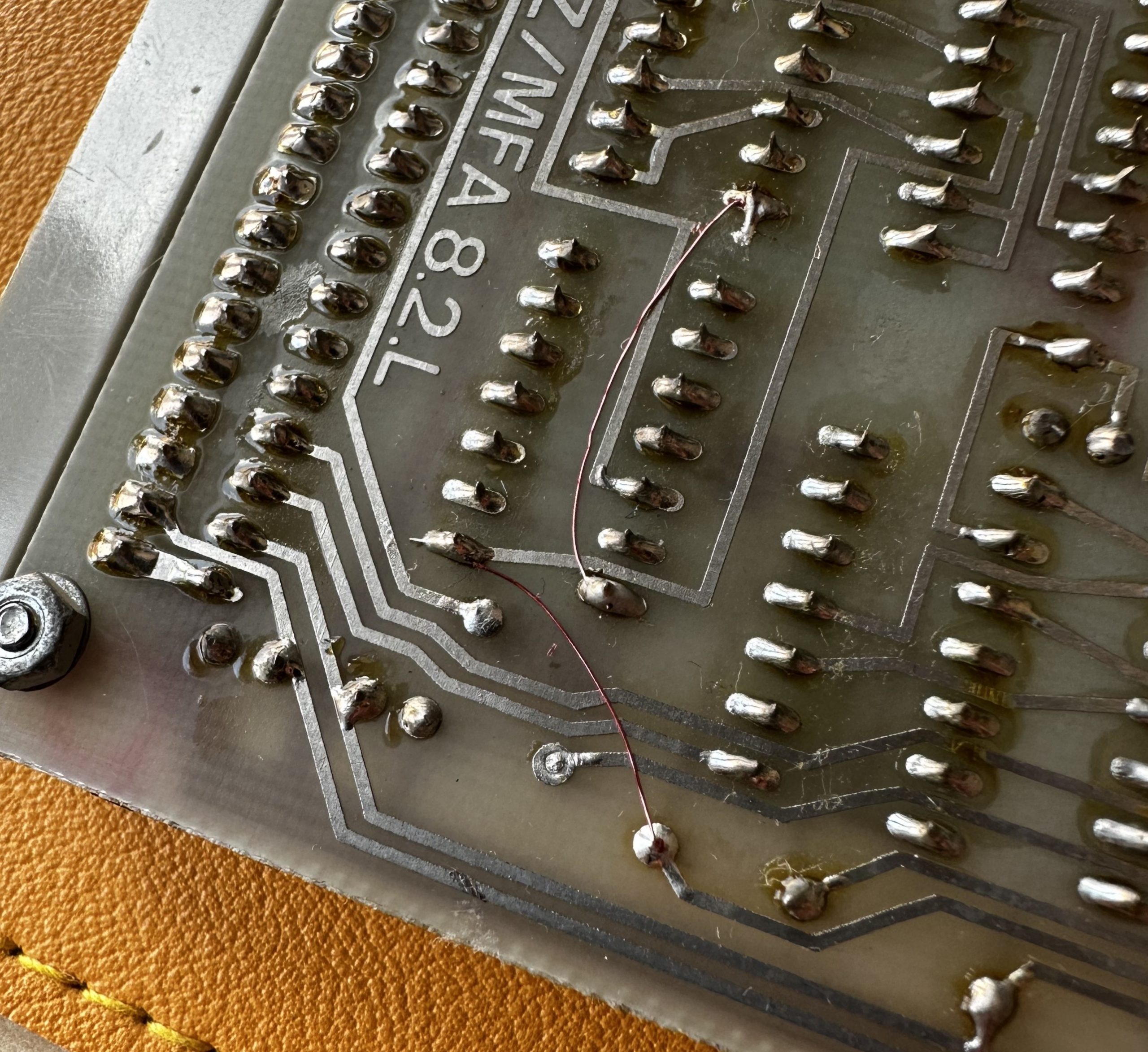

Die Zwischenspeicherung der Adressen

Wegen der begrenzten Anzahl (40) der Anschlüsse der CPU 8085 gibt sie die unteren acht Adressbits und die acht Datenbits zeitlich nacheinander (Zeitmultiplex) über die gleichen CPU-Anschlüsse AD0 . .. AD7 aus. Die Bezeichnung AD besagt, daß diese Anschlüsse sowohl für Adressen als auch für Daten benutzt werden

Eine Adresse muß nun so lange ausgegeben werden, bis der Prozessor von der adressierten Speicherstelle Daten geholt oder an sie ausgegeben hat. Damit die unteren 8 Adressbits auch während der Zeit des Datentransports verfügbar sind, werden sie zwischengespeichert. Die Übernahme der von der CPU ausgegebenen Adresse in den Zwischenspeicher erfolgt mit der abfallenden Flanke des ALE-Signals. Damit die Adressen auf den System-Bus gelangen können, muß das Steuersignal HLDA (Hold Acknowledge = Halt bestätigen) L-Pegel führen, denn das HLDA-Signal liefert H-Pegel, wenn die CPU über die HOLD-Leitung angehalten wird, und schaltet dann den Zwischenspeicher in den hochohmigen Zustand.

In Bild 56 ist die Schaltung zur Zwischenspeicherung der Adressen dargestellt. Die ausgangsseitig (mit OE) abschaltbaren 8-Bit-D-Register (IC9, IClO) dienen gleichzeitig als Treiber (Pufferung) zum System-Bus hin.

Bild 56: Die Adressen-Zwischenspeicherung

Erkennung der Datensignale und Steuerung der Datenrichtung

Nachdem mit Hilfe des·Steuersignals ALE eine Adresse an IC9 und IClO übergeben worden ist, benutzt die CPU die unteren 8 Adressleitungen auch für den Datentrans- port (siehe Abschnitt »Taktsteuerung«.

Im Gegensatz zu den Adressen, die von der CPU nur ausgegeben werden, kann die CPU Daten sowohl ausgeben als auch empfangen. Der Treiber (IC8 in Bild 57) für die Datensignale muß daher in seiner Übertragungsrichtung umschaltbar sein. Solche ICs nennt man bidirektional, d. h. in zwei Richtungen benutzbar. Bild 57 zeigt die Schaltung zur Pufferung der Datenleitungen und zur Steuerung der Datenübertragungs-Richtung.

Bild 57: Pufferung der Datenleitungen und Steuerung der Datenübertragungs-Richtung.

Zunächst wird davon ausgegangen, daß der CPU-Ausgang HLDA L-Pegel hat (die Aufgabe dieses Signals wird später beschrieben). Damit ist der »Bus-Sendeempfänger« (IC8) über den OE-Eingang für Datenverkehr freigegeben.

Die Datenübertragungs-Richtung wird durch den Pegel am DIR-Eingang bestimmt:

- Wenn die CPU Daten lesen will, schaltet sie den Steuerausgang RD (READ = Lesen) oder INTA (Interrupt Acknowledge = Unterbrechung angenommen) auf

L-Pegel. Über das UND-Gatter IC5.2 erhält der DIR-Eingang H-Pegel, und Daten werden vom System-Bus zur CPU übertragen. - Wenn die CPU Daten aussenden will, schaltet sie die Steuerausgänge RD und INTA auf H-Pegel. Der DIR-Ausgang erhält L-Pegel, und Daten werden von der CPU zum System-Bus übertragen.

Trennen der CPU vom Systembus über den CPU-Eingang HOLD

Die Trennung der CPU vom System-Bus erfolgt über den HOLD-Eingang an der CPU (hold= anhalten). Ein H-Pegel an diesem Eingang stoppt die Programm-Abarbeitung der CPU nach Beendigung des gerade laufenden Maschinenzyklus. Gleichzeitig schaltet die CPU intern den Adress-Bus, den Daten-Bus und die Steuerausgänge RD, WR und IO/M in den hochohmigen Zustand und zeigt durch H-Pegel am

Ausgang HLDA (Hold Acknowledge = Halt bestätigen) an, daß sie sich im Halt-Zustand befindet. Mit diesem H-Pegel werden die Adressbus-Puffer (IC9, IClO) und der Datenbus-Sendeempfänger (IC8) in den hochohmigen Zustand geschaltet (siehe Bilder 56 und 57). In diesem Zustand können dann von außen, z.B. über den Bus-Si- gnalgeber, Adressen und Steuersignale auf den System-Bus gegeben und Daten auf dem Daten-Bus zwischen Ausgabe- und Eingabe-Einheiten ausgetauscht werden.

Das Zusammenwirken der Baugruppen Prozessor 8085 und BUS-Signalgeber

Mit dem ON/OFF-Schalter in der Baugruppe Bus-Signalgeber läßt sich entweder der Bus-Signalgeber oder der Prozessor 8085 vom System-Bus trennen; vgl. Bild 58. Hierdurch erreicht man, daß nur immer eine Baugruppe Signale auf den System-Bus gibt und Kurzschlüsse vermieden werden, die bei unterschiedlichen Signalpegeln auf gleichen Leitungen entstehen würden.

Bild 58: Die Blockschaltbilder der Baugruppen Prozessor 8085 und Bus-Signalgeber

ON/OFF-Schalter in Stellung ON (siehe Bild 58): Das Flipflop IC4.l ist gesetzt (Q = H, Q = L); es entprellt den Schalter S11. Der L-Pegel seines Q-Ausgangs bewirkt über die HOLD-Leitung und den Inverter IC6.4, daß der CPU-Eingang HOLD H-Pegel erhält. Dadurch werden CPU und Prozessorbaugruppe (HLDA) wie oben beschrieben vom System-Bus getrennt. Die mit dem Bus-Signalgeber eingestellten Adress- und Daten-Signale stehen auf dem System-Bus zur Verfügung. Bei Betätigung einer der vier Steuertaster MEMR, MEMW, IOR und IOW nimmt die zugehörige Busleitung L-Pegel (aktiv) an.

ON/OFF-Schalter in Stellung OFF:

Das Flipflop IC4.1 ist zurückgesetzt (Q = L, Q = H). Dadurch werden drei verschiedene Funktionen ausgelöst:

Der L-Pegel seines Q-Ausgangs sperrt im Bus-Signalgeber die Treiber für die Adress- Daten- und Steuersignale (IC5 – IC6).

Der H-Pegel seines Q-Ausgangs bewirkt am CPU-Eingang HOLD einen L-Pegel. Damit wird der Halt-Zustand der CPU aufgehoben.

Der L-H-Sprung seines Q-Ausgangs beim Schalten von ON auf OFF setzt das D- Flipflop IC4.2; der Q-Ausgang erhält H-Pegel. Über den Inverter IC3.2 und die RESIN-Leitung wird der CPU-Eingang RESET IN auf L-Pegel gelegt. Hierdurch wird der Befehlszähler der CPU auf 0000H gesetzt. Mit dem dadurch von der CPU ausgegebenen RESET OUT-Signal (H) wird über Inverter IC6.6 und die RESOUT-Leitung das D-Flipflop IC 4.2 zurückgesetzt. Gleichzeitig wird die Programmabarbeitung von der CPU bei Adresse 0000H begonnen.

Die Steuersignale MEMR, MEMW, IOR, IOW

Nachdem die CPU die Adressen für einen Speicherplatz oder eine Eingabe- oder Ausgabe-Baugruppe ausgegeben hat, gibt sie mit den Pegeln auf drei Steuerleitungen an, ob sie Daten in die adressierte Baugruppe schreiben oder aus ihr lesen will. Die drei Steuerleitungen haben die Bezeichnung RD (Lesen), WR (Schreiben) und IO/M (Ein/Ausgabe-Speicher). Die folgende Tabelle (Bild 59) zeigt die Wirkungen der Steuersignale und ihre zugehörigen Signalpegel.

| Wirkung | IO /M | /RD | /WR |

|---|---|---|---|

| Speicher lesen (MEMR) | L | L | H |

| Speicher schreiben (MEMW) | L | H | L |

| Ein/Ausgabe lesen (IOR) | H | L | H |

| Ein/Ausgabe schreiben (IOW) | H | H | L |

Bild 59: Die Wirkung der Steuersignale 10/M, WR und RD.Die in der Spalte »Wirkung« in Klammern angegebenen Steuersignale müssen durch eine geeignete Decodierung aus den drei CPU- Steuersignalen gewonnen werden. Die dazu benutzte Schaltung ist in Bild 60 dargestellt.

Bild 60: Die Decodierung der CPU-Steuersignale RD, WR und IO/M.

Die Funktionstabelle des 1-aus-8-Decodierers (Bild 15) zeigt alle Signalkombinationen, die von der CPU ausgesendet werden. Diese Signalkombinationen führen an den Ausgängen Y1, Y3, Y4 und Y6 zu den gewünschten L-Pegeln für die vier Steuersignale MEMW, IOW, MEMR und IOR.

Bild 61: Die Funktionstabelle des 1-aus-8-Decodierers 74LS138.

Der dem 1-aus-8-Decodierer nachgeschaltete Leistungstreiber (IC11) mit Tristate- Ausgängen kann über die HLDA-Leitung mit H-Pegel in den hochohmigen Zustand geschaltet werden.

Die Einzelschrittsteuerung der CPU

Bei der Inbetriebnahme der CPU und während der Testphase neu erstellter Programme erweist es sich als nützlich, die CPU im Einzelschritt betreiben zu können. Man unterscheidet im Einzelschrittbetrieb zwei Möglichkeiten:

- ein Schritt besteht aus einem Befehl;

- ein Schritt entspricht einem Maschinenzyklus, besteht also möglicherweise nur aus einem Teil eines Befehls

Hier wird von der zweiten Möglichkeit Gebrauch gemacht. Hierzu werden CPU- Steuereingang READY und der CPU-Steuerausgang ALE benutzt.

Die Funktion des READY-Signals

Im zweiten Takt T2 eines Maschinenzyklus fragt die CPU den Zustand des READY- Eingangs (ready = bereit) ab. Ein L-Pegel an diesem Eingang bewirkt, daß die CPU »Wartezyklen« einfügt, bis das Signal auf H-Pegel übergeht. Erst dann wird der begonnene Lese- oder Schreibzyklus beendet. Die vor Beginn der Wartezyklen ausgegebenen Adress-, Daten- und Steuersignale stehen auf den entsprechenden Busleitungen bereit und können nachgemessen oder z.B. mit der Bus-Signalanzeige angezeigt werden.

Grundschaltung zur Einzelschrittsteuerung

Bild 62 zeigt eine einfache Schaltung, mit der es möglich ist, die CPU zu stoppen und sie – jeweils durch Betätigen einer Step-(Schritt-)Taste – einen Maschinenzyklus weiterarbeiten zu lassen.

Bild 62: Die Grundschaltung für den Einzelschrittbetrieb.

Steht zunächst der RUN/Halt-Schalter auf RUN, so liegt der READY-Eingang über den Widerstand R auf H-Pegel. Die CPU arbeitet und setzt das D-Flipflop mit dem nachsten ALE-Impuls zurück (Q = L), falls es vorher (mit der STEP-Taste oder durch Zufall beim Einschalten der Betriebsspannung) gesetzt worden war. Stellt man nun den RUN/HALT-Schalter auf HALT, so erhält die CPU ein L-Signal am READY-Eingang und stoppt. Bei Betätigung der STEP-Taste wird das D-Flipflop wieder gesetzt (Q = H); der READY-Emgang erhält H-Signal, und die CPU arbeitet weiter, bis der folgende ALE-Impuls das Flipflop zurücksetzt und sie wieder anhält.

Da ein ALE-Impuls jeweils einen Maschinenzyklus einleitet, entspricht jeder Arbeitsschritt der CPU einem Maschinenzyklus.

Gemeinsames Auftreten von HOLD und READY-Signal

Aus dem internen Zustandsdiagramm der CPU 8085 (Herstellerangabe, Datenbuch) geht hervor, daß ein aktives HOLD-Signal (H) nicht mehr von der CPU angenommen wird, wenn sie vorher durch ein READY-Signal (L) gestoppt wurde. Wenn die CPU also gerade Wartezyklen im Einzelschritt-Betrieb erzeugt und gleichzeitig der Bus- Signalgeber eingeschaltet wird, so wird das vom Bus-Signalgeber gesendete HOLD- Signal von der CPU nicht verarbeitet.

Da jetzt aber die CPU und der Bus-Signalgeber gleichzeitig Signale auf den Systembus senden, wird es bei unterschiedlichen Signalpegeln auf gleichen Leitungen zu Kurzschlüssen kommen.

Um das zu verhindern, muß das Auftreten des aktiven HOLD-Signals dazu genutzt werden, den Einzelschrittbetrieb abzuschalten, also READY auf H-Pegel zu setzen. Bild 63 zeigt die Grundschaltung, die diese Funktion übernehmen kann.

Bild 63: Die Grundschaltung zur Verhinderung des gemeinsamen Auftretens von HOLD- und READY-Signalen.

Wenn der Bus-Signalgeber (siehe Kapitel 5.1) eingeschaltet wird (ON), gelangt ein L-Pegel an den Setzeingang des D-Flipflops und setzt den Q-Ausgang auf H-Pegel. Damit verläßt die CPU den Wartezustand, wird aber gleichzeitig durch das Signal am HOLD-Eingang (H) vom Systembus getrennt.

Einzelschritt ab einer bestimmten Adresse

Bei Inbetriebnahme- und Fehlersuch-Arbeiten kann es nützlich sein, die CPU ihr Programm zunächst bis zu einer bestimmten Adresse abarbeiten zu lassen und sie von dort ab im Einzelschrittbetrieb zu steuern. Bild 64 zeigt die Grundschaltung, die diese Betriebsart ermöglicht.

Bild 64: Die Grundschaltung für den Einzelschrittbetrieb ab einer vorgewählten Adresse.

Wenn der »Adressenstop« eingeschaltet ist (ON), wird die CPU nicht durch das ALE-Signal, sondern durch das Signal vom Adreßvergleicher über den READY-Ein- gang angehalten. Die »Stop-Adresse« wird mit den Schaltern Sl bis S16 eingestellt. Der Adreßvergleicher liefert nur dann ein H-Signal, wenn die Addresse auf dem Adreßbus mit der eingestellten übereinstimmt.

Zur Steuerung des Einzelschrittbetriebs muss dann der »Adreßstop« ausgeschaltet (OFF) werden. Jeder Einzelschritt kann mit der STEP-Taste gestartet werden.

Das Zusammenwirken der Baugruppe Prozessor 8085 und BUS-Signalanzeige

Alle zur Einzelschrittsteuerung gehörenden Funktionsgruppen befinden sich auf der Baugruppe »Bus-Signalanzeige«; Das nachfolgende Bild zeigt den entsprechenden Teil der Schaltung mit den erforderlichen Verbindungen zur CPU.

Bild 65: Das Zusammenwirken des Prozessors 8085 mit der Einzelschrittsteuerung.

IC4.1 entprellt den mechanischen STEP-Taster. Der in Bild 64 als Block dargestellte »Adressenstop« besteht aus dem mechanischen Umschalter und den ICs 3.2 … 3.4.

Einzelschrittbetrieb ohne Adressstop

Voraussetzung:

- ADR.STOP-Schalter auf OFF

- RUN/HLT-Schalter auf HLT

Die CPU legt Wartezyklen ein; Adress-, Daten- und Steuersignale werden auf der Bus-Signalanzeige angezeigt.

Bei Betätigen der STEP-Taste wird der Ausgang von IC4.2 und damit READY auf H-Pegel gesetzt.

Die CPU arbeitet einen Maschinenzyklus lang und wird durch den ALE-Impuls zu Beginn des folgenden Maschinenzyklus wieder gestoppt.

Weitere Schritte werden jeweils durch Betätigen von STEP eingeleitet.

Anmerkung: Soll die CPU den Einzelschrittbetrieb bei Adresse 0000H aufnehmen, muß vor Betätigen der STEP-Taste die Reset-Taste der CPU betätigt werden.

Einzelschrittbetrieb mit Adressstop

Voraussetzungen:

- RUN/HLT-Schalter auf HLT.

- ADR.STOP-Schalter auf ON.

Vorher muß die gewünschte Stoppadresse mit DIL-Schaltern auf der Bus-Signalanzeige eingestellt werden. Die Startadresse 0000H wird durch Betätigen von Reset eingegeben.

Die CPU legt Wartezyklen ein; Adreß-, Daten- und Steuersignale werden angezeigt.

Betätigen der STEP-Taste startet die CPU. Wenn sie die gewünschte Adresse erreicht hat, wird der Ausgang vom IC4.2 und damit auch READY auf L-Pegel gesetzt.

Die CPU legt Wartezyklen ein.

Jetzt ADR.STOP-Schalter auf OFF! Einzelschrittbetrieb wie oben

Interrupt-Eingänge und Interrupt-Signale

CPU während der Programm-Abarbeitung zu unterbrechen und sie zu veranlassen, zunächst ein anderes Programm zu bearbeiten. Nach der Ausführung des Unterbrechungsprogramms bearbeitet die CPU dann das alte Programm weiter.

Die Unterbrechungs-Eingänge heißen Interrupt-Eingänge , die Unterbrechungssignale entsprechend Interrupt-Signale oder kurz Interrupts.

Beispiele für die Anwendung von Interrupts:

- periphere Geräte (z.B. Drucker, Tastatur, Lochstreifenleser etc.) melden über einen Interrupteingang, daß sie mit dem Mikrocomputer in Kontakt treten wollen;

- bei falscher Programmausführung will der Bediener den Programmablauf unterbrechen;

- Behebung von Fehlern bei Prozeß- oder Maschinen-Steuerungen.

Ein Interruptsignal bewirkt im Mikroprozessor die folgenden Aktivitäten:

- Der gerade laufende Befehl wird zu Ende geführt.

- Die Adresse des folgenden Befehls wird gespeichert, da das Programm später weiterbearbeitet werden muß.

- Erzeugung einer zum jeweiligen Unterbrechungseingang zugeordneten Adresse, Sprung dorthin und Abarbeitung des dort niedergelegten Interrupt-Bedienungsprogramms.

- Rücksprung ins Ausgangsprogramm zur gespeicherten Adresse.

Die folgende Tabelle gibt eine Übersicht über die Interrupteingänge der CPU 8085 sowie über die zur Auslösung eines Interrupts erforderlichen Signale, die erzeugten Sprungadressen und die Priorität (Vorrangigkeit) der Interrupts.

| Bezeichnung des Eingangs | Priorität | zur Adresse (hex) | Art der Auslösung des Interrupts durch |

|---|---|---|---|

| TRAP | 1 | 0024 | L-H-Flanke und H-Pegel bis zur Annahme |

| RST 7.5 | 2 | 003C | L-H-Flanke; Anforderung wird bis zur Annahme gespeichert |

| RST 6.5 | 3 | 0034 | H-Pegel bis zur Annahme |

| RST 5.5 | 4 | 002C | H-Pegel bis zur Annahme |

| INTR | 5 | * | H-Pegel bis zur Annahme |

Abhängig vom Datenbyte sind die folgenden Sprungadressen möglich:

| Datenbyte | C7 | CF | D7 | DF | E7 | EF | F7 | FF |

| Adresse | 0000 | 0008 | 0010 | 0018 | 0020 | 0028 | 0030 | 0038 |

Weitere Informationen über die Unterbrechungsbehandlung finden Sie im Datenbuch »Mikroprozessor-System SAB 8085« der Firma Siemens.

Ein aktiver Interrupt-Eingang kann oft einen unerwünschten Arbeitsablauf der CPU zur Folge haben. Deshalb ist es wichtig, die Signalpegel der Interrupt-Eingänge bei Inbetriebnahmearbeiten auf ihre richtigen Werte hin zu überprüfen. Das Bild gibt die richtigen Pegelwerte an:

Bild 67: Die Pegelwerte der nicht aktiven Interrupt-Eingänge

Serieller Daten-Eingang (SID) und -Ausgang (SOD)

Ohne großen Schaltungsaufwand ist es bei der CPU 8085 möglich, mit Hilfe zweier spezieller Befehle parallel vorliegende Daten seriell zu senden bzw. zu empfangen. Beim Senden muß das zu sendende Datenbyte im Akkumulator stehen. Es wird dann Bit für Bit über den Ausgang SOD (Seriell Output Data = serieller Datenausgang) ausgegeben. Beim Empfang über den Eingang SID (Seriell Input Data = serieller Dateneingang) gelangt das bitweise empfangene Datenbyte ebenfalls in den Akkumu- lator.

Peripherie-Geräte, wie z.B. ein Datensichtgerät oder eine Teletype (Teletypewriter = Fernschreiber, kurz TIY), stehen mit dem Mikrocomputer über den seriellen Datenaustausch in Verbindung.

Damit der Mikrocomputer mit solchen Ein/Ausgabegeräten Verbindung aufnehmen kann, sind auf den Übertragungsleitungen bestimmte genormte Pegel erforderlich. Man unterscheidet zwischen Strom- und Spannungspegel und entsprechenden Schnittstellen (Schnittstelle: Verbindung, Anpassung zwischen Mikrocomputer und externen Geräten, auch Interface genannt).

Eine 20-mA-Stromschnittstelle wird bei einer Teletype benötigt und entspricht folgender Vereinbarung:

- logisch 1 = unterbrochener Stromkreis (kein Strom)

- logisch 0 = Strom von 20 mA

Die meisten peripheren Geräte werden über eineV-24-Spannungsschnittstelle betrie- ben (z.B . Datensichtgerät); dabei gilt dann die folgende Vereinbarung:

- logisch 1 = Spannung zwischen – 3 V und -25 V

- logisch 0 = Spannung zwischen +3 V und + 25 V

Da die CPU Ausgangssignale mit Spannungen von 5 V oder OV liefert, ist zwischen ihr und Geräten mit 20-mA- und V-24-Schnittstellen eine Pegelanpassung erforderlich.

Die 20mA-Stromschnittstelle

Das Bild zeigt die 20-mA-Stromschnittstelle der Baugruppe »Prozessor 8085« und den Anschluß eines Fernschreibers (Teletype, TTY) daran.

Bild 68: 20-mA-Stromschnittstelle und Fernschreiberanschluss.

Der untere Schaltungsteil in Bild 68 mit den Eingängen Rx, RxRet ist der Empfangstelle der 20-mA-Stromschnittstelle, und der obere mit den Eingängen Tx TxRet ist der Sendeteil.

Bei Betätigung einer Taste des Fernschreibers wird in seinem Sendeteil entsprechend dem Code des Zeichens auf der Taste ein Kontakt geschaltet. Ein geschlossener Kontakt bewirkt, dass Transistor T2 leitet und der SID-Eingang H-Pegel erhält. Bei offenem Kontakt hegt SID auf L-Pegel. Soll das von der CPU aufgenommene Zeichen auch ausgedruckt werden, so muß ein eigens dafür bereitzustellendes Programm dafür sorgen, daß das Zeichen am CPU-Ausgang SOD seriell ausgegeben wird.

Ein H-Pegel an SOD sperrt Transistor T1 und unterbricht den Strom (20 mA) zum Empfangsteil des Fernschreibers. Das dort eingebaute Empfangsrelais wird nicht erregt. Bei einem L-Pegel an SOD leitet T1 und erregt das Empfangsrelais. Nachdem das gesamte Zeichen übertragen ist, wird es auf dem Druckwerk des Fernschreibers ausgedruckt.

Die V24-Spannungsschnittstelle

Bild 69: V-24-Spannungsschnittstelle und Anschluß einer Datensichtstation (Tastatur und Monitor).

Die Anpassung der TIL-Pegel auf V-24-Pegel und umgekehrt übernehmen die integrierten Bausteine IC1.1 und IC2.1. Der Schaltkreis IC1.1 benötigt dazu eine Spannungsversorgung von ±12 V.

Der Datenverkehr läuft wie folgt ab:

Ein mit der ASCII-Tastatur ausgegebenes Zeichen gelangt in paralleler Form in den »Seriellen Sender« innerhalb der Baugruppe »Video-Interface«. Er wandelt dieses Zeichen in die serielle Form um und liefert es so an die CPU. Mit Hilfe eines eigens für diesen Zweck vorhandenen Programms (Teil des Betriebsprogramms) gelangt es über den Eingang SID in den Akkumulator, das ist ein spezielles Register innerhalb der CPU. Aus dem Akkumulator wird das Zeichen dann in serieller Form über den CPU-Ausgang SOD an den seriellen Empfänger innerhalb des Video-Interfaces gesendet. Dieser wandelt das Zeichen in die parallele Form zurück und liefert es an den Videoteil. Dort wird es dann in eine Form gebracht, die eine Darstellung auf dem Bildschirm des Fernsehgerätes gestattet.

Bestückungsplan CPU-Baugruppe