Einleitung

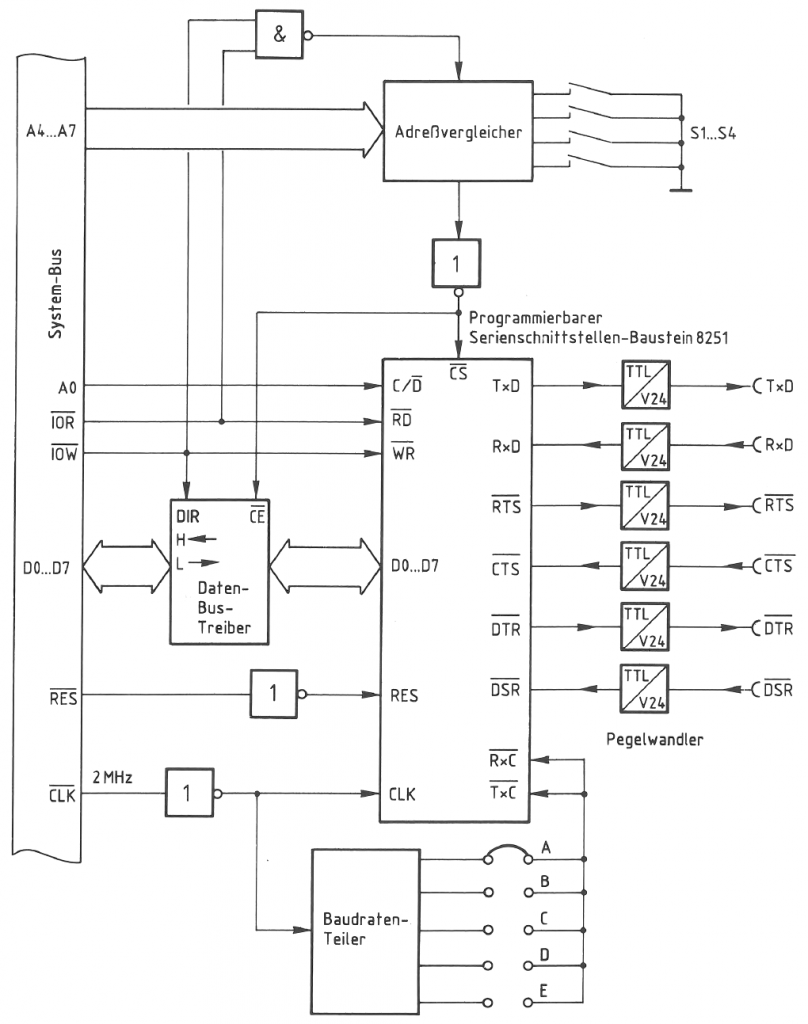

Die Funktionsbeschreibung bezieht sich nur auf das Blockschaltbild. Einzelheiten des verwendeten Schnittstellenbausteins 8251 werden im Band 2 der Fachpraktischen Übungen behandelt (BFZ/MFA 4.4. „Programmierbare Serienschnittstelle“ und BFZ/MFA 4.4.a „Kassetten-Interface“).

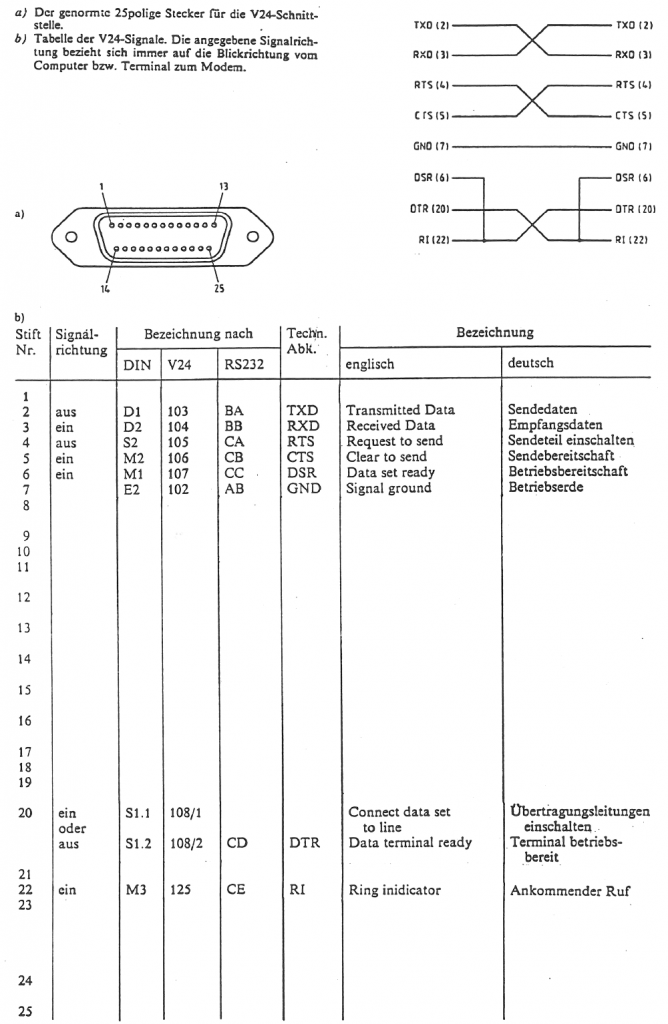

Die serielle Daten-Sendeleitung TxD, die serielle Daten-Empfangsleitung RxD sowie einige Steuerleitungen des Schnittstellenbausteins 8251 sind über TTL/V24-Pegelwandler mit einer 25poligen Buchsenleiste auf der Frontplatte der Baugruppe verbunden.

Für interne Steuerzwecke erhält der Baustein am Anschluss CLK den von einem Inverter

aufgefrischten 2-MHz-Systemtakt.

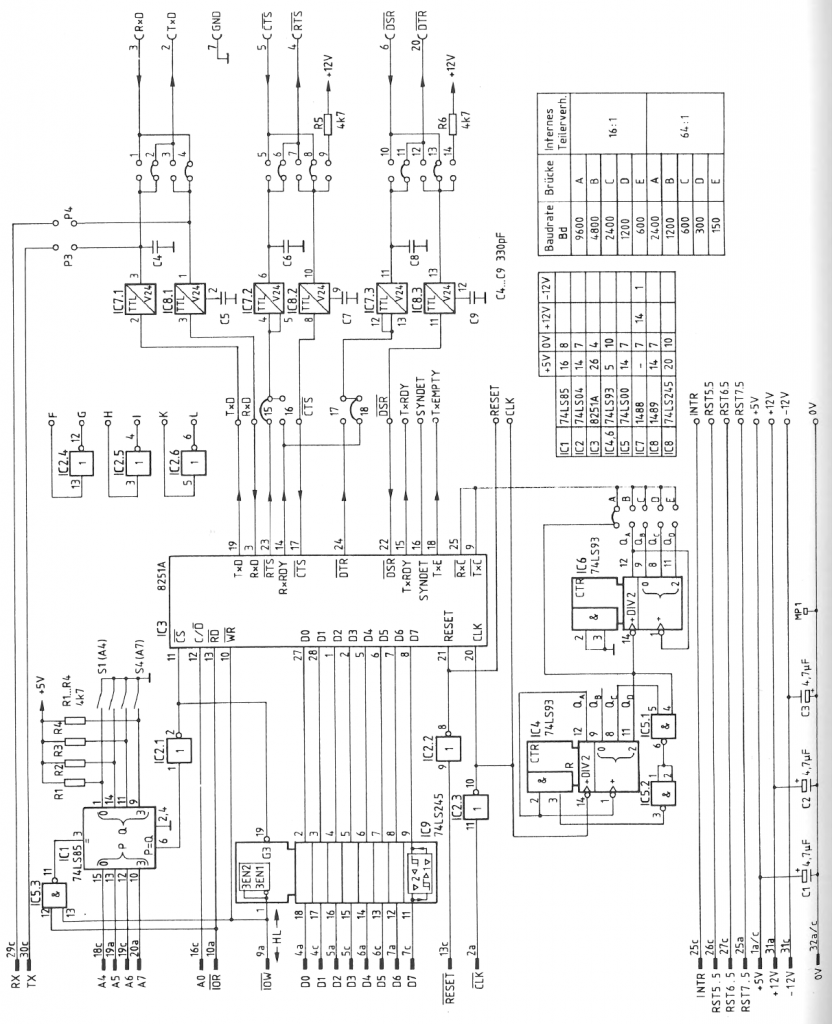

Aus dem System-Takt wird außerdem im Baudraten-Teiler der zur Parallel/Seriell-und Seriell/Parallel-Wandlung erforderliche Baudraten-Takt gewonnen und dem Baustein an den Anschlüssen RxC und TxC zugeführt. Durch Lötbrücken und geeignete Initialisierung können 7 verschiedene Baudraten eingestellt werden (siehe Tabelle im Stromlaufplan).

Der Daten-Bus ist über einen bidirektionalen Datenbus-Treiber in TristateTechnik mit den Datenleitungen des Schnittstellen-Bausteins verbunden. Der Datenbus-Treiber trennt im Ruhezustand den Datenweg und gewährleistet im aktiven Zustand einen ausreichend hohen Treiberstrom in Richtung System-Bus. Zur Aktivierung des Datenbus-Treibers muss der Anschluss CE (Chip Enable) L-Pegel erhalten.

Über den Anschluss DIR (direction, Richtung) wird mit dem Signal IOW die Arbeitsrichtung des Datenbus-Treibers gesteuert. Hierdurch wird festgelegt, ob Daten vom Prozessor zum Baustein 8251 und von dort über den Anschluss TxD seriell ausgesendet werden, oder ob der Prozessor die über den Anschluss RxD seriell empfangenen Daten liest.

Die Freigabe des Datenbus-Treibers und des Schnittstellenbausteins erfolgt durch den Adressvergleicher. Dies geschieht nur, wenn die Adresse auf den Adressleitungen A4 bis A7 mit derjenigen Baugruppen-Nummer übereinstimmt, die mit den Schaltern S1 bis S4 eingestellt ist. Zur Freigabe des Adressvergleichers muss eine der Steuerleitungen IOW oder IOR aktiv sein. Mit der Adressleitung A0 werden bei H-Pegel die Control-Register, und bei L-Pegel die Datenregister (Sender- und Empfänger-Register) des 8151 adressiert.

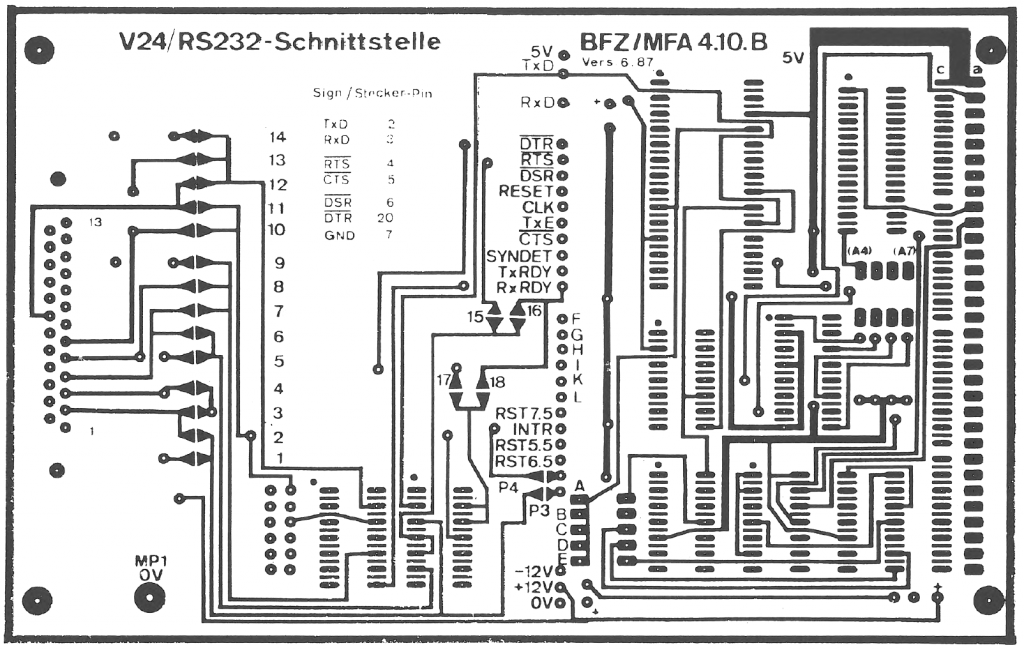

Blockschaltbild

Verbindungen Schnittstellenbaustein – 25polige Buchsenleiste

- TxD (Transmitter-Data, Senderdaten): Serieller Datenausgang des Bausteins, durch Lötbrücke 2 mit Anschlussstift 2 der 25poligen Buchsenleiste verbunden.

- RxD (Receiver-Data, Empfängerdaten): Serie 11 er Dateneingang des Bausteins, durch Lötbrücke 4 mit Anschlussstift 3 der 25poligen Buchsenleiste verbunden

- RTS (Request To Send, Sendeteil der Peripherie einschalten): Der Signalzustand dieses beliebig verwendbaren Bausteinausgangs wird bei der Initialisierung durch das Kommandowort festgelegt und kann danach auch wieder per Programm verändert werden. In der Grundverdrahtung der V24/RS232-Schnittstelle wird das Bausteinsignal RTS über die Lötbrücke 15, den Pegelwandler IC7.2 und die Lötbrücke 6 auf den RTS-Anschluss der 25poligen Buchsenleiste geführt (Anschlussstift 4).

- RxRDY (Receiver Ready, Empfänger hat ein Zeichen empfangen/ist besetzt): Ausgang, der beim Vorliegen eines Zeichens im Empfängerregister des Schnittstellenbausteins H-Pegel annimmt. In der Grundverdrahtung der Schnittstelle wird RxRDY über die Brücke 18, den Pegelwandler IC7.3 und die Brücke 11 zum Anschlussstift „DTR“ der 25poligen Buchsenleiste geführt. Hiermit kann der externe Datensender so lange gestoppt werden, bis das Empfängerregister des Bausteins von der CPU gelesen („geleert“) wurde und damit wieder bereit ist, ein neues Zeichen aufzunehmen.

- CTS (Clear To Send, Senderfreigabe): L-Signal an diesem Bausteineingang gibt den eigenen Datensender frei, H-Signal sperrt ihn. Über den Pegelwandler IC8.2 und die Lötbrücke 8 ist der CTS-Anschluss des Bausteins mit Anschlussstift 5 der 25poligen Buchse verbunden. Hier ist zur Senderfreigabe 0-Signal (+3 V bis +12 V) erforderlich. Bei 1-Signal (-3 V bis -12 V) oder offenem Eingang ist der Datensender gesperrt.

Wird anstelle der Lötbrücke 8 die Lötbrücke „9“ geschlossen, so erfolgt die Senderfreigabe nicht über die Peripherie, sondern über R5 (Datensender ist ständig freigegeben).

- DTR (Data Terminal Ready, Betriebsbereitschaft des eigenen Gerätes): Der Signalzustand dieses beliebig verwendbaren Ausgangs wird bei der Initialisierung des Bausteins durch das Kommandowort festgelegt und kann danach auch wieder per Programm verändert werden. Mit L-Pegel am Bausteinanschluss DTR kann einem Peripheriegerät mitgeteilt werden, daß die Serienschnittstelle betriebsbereit ist.

- DSR (Data Set Ready, Betriebsbereitschaft eines anderen Gerätes): Der Signal zustand dieses beliebig verwendbaren Eingangs kann über das Statuswort des Schnittstellenbausteins abgefragt werden. Mit Hilfe des Anschlusses DSR ist der Prozessor hierdurch z.B. in der Lage, die Betriebsbereitschaft eines Peripheriegerätes festzustellen. Hierzu muss dieses Gerät 0-Signal (+3 V bis 12 V) auf die DSR-Leitung legen.

Stromlaufplan

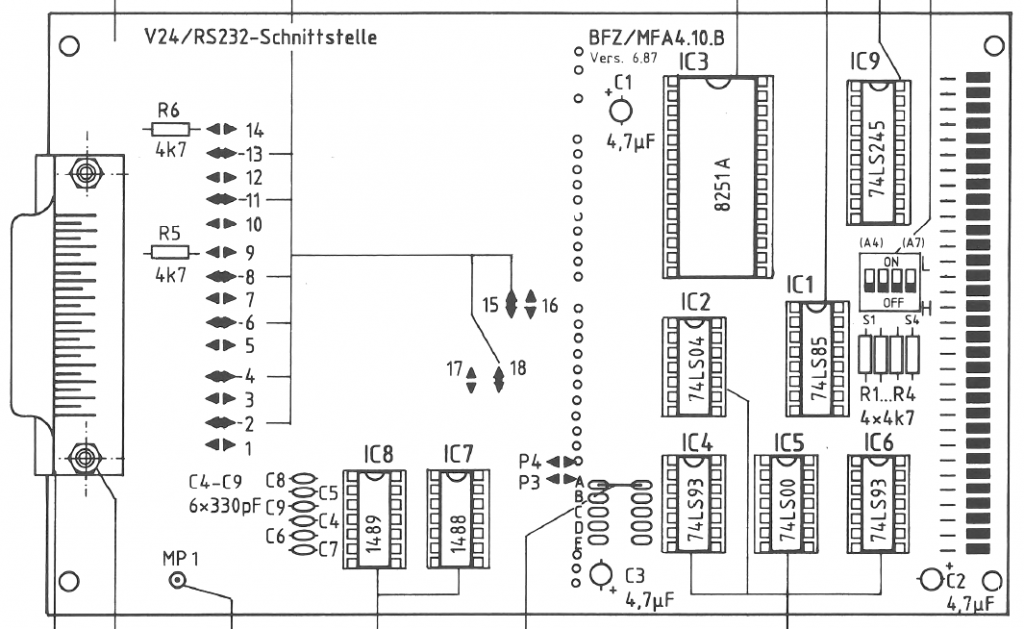

Bestückungsplan

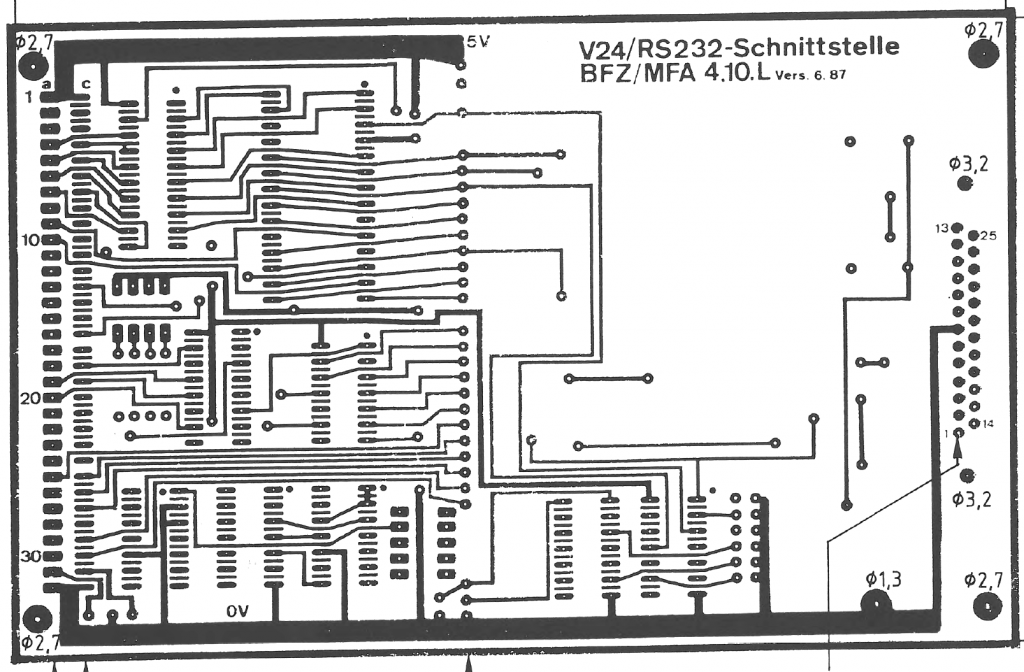

Platine

Bestückungsseite

Rückseite

Anschlussbelegung V24/RS232 Datenkabel