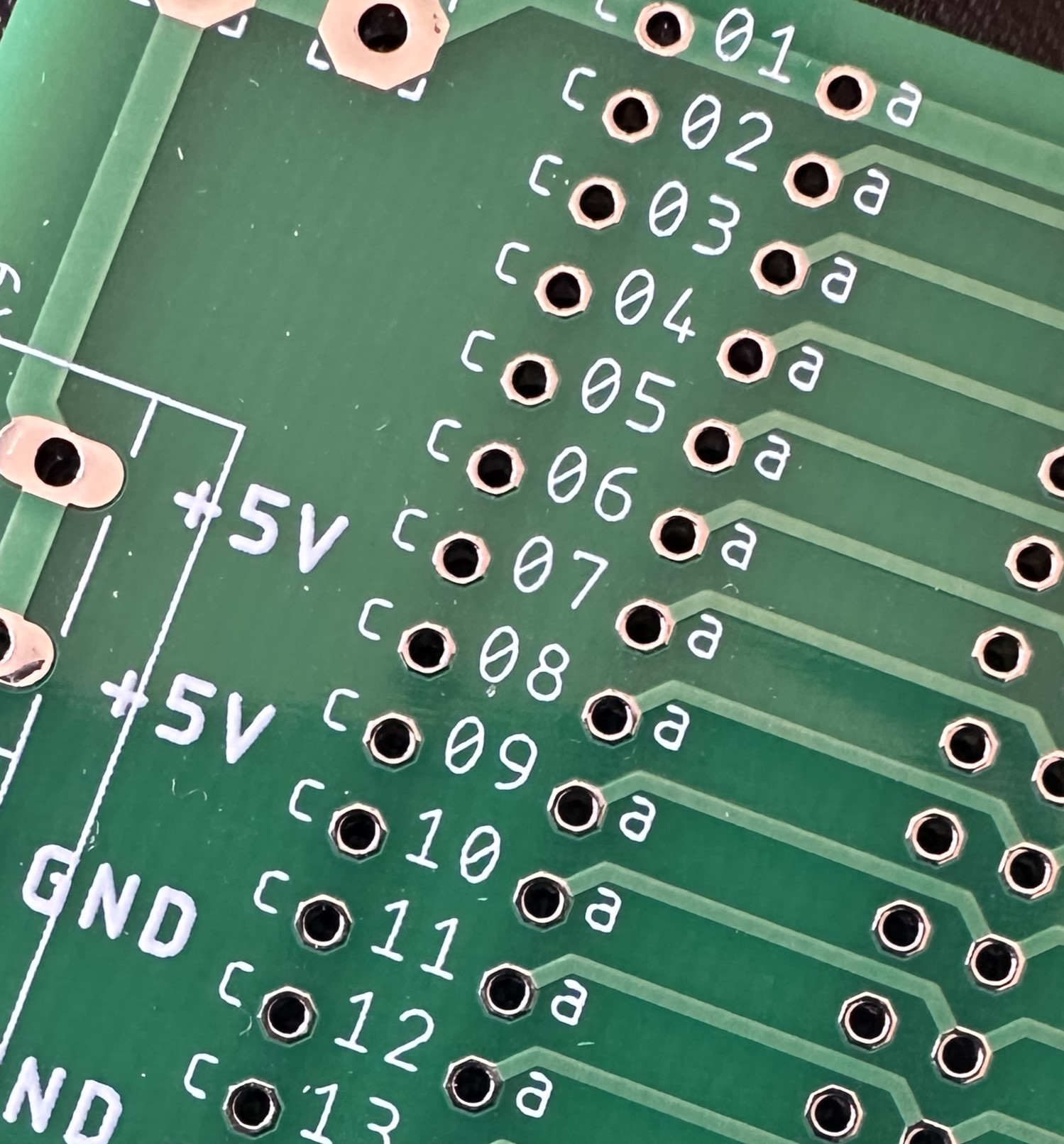

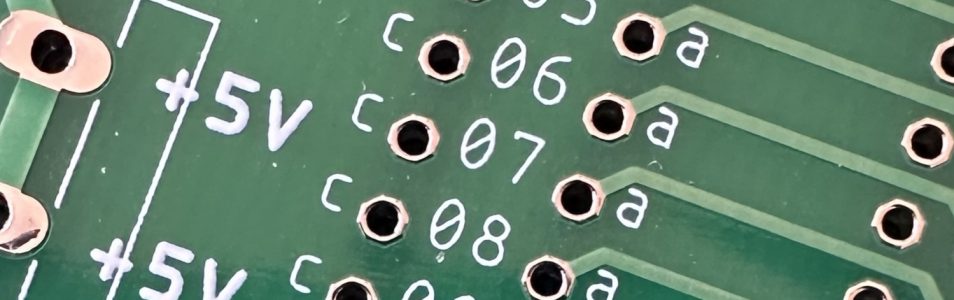

| Beschreibung | I/O | Pin | BUS A | BUS C | Pin | I/O | Beschreibung |

|---|---|---|---|---|---|---|---|

| a | c | ||||||

| + 5 Volt Pin A | 1a | +5V | +5V_c | 1c | + 5 Volt Pin C | ||

| Taktausgabe | O | 2a | /CLKOUT | /S1 | 2c | CPU-State S1 | |

| Address Ledge Enable Adressübernahem | O | 3a | /ALE | /S0 | 3c | CPU-State S0 | |

| Data | I/O | 4a | D0 | D1 | 4c | I/O | Data |

| Data | I/O | 5a | D2 | D3 | 5c | I/O | Data |

| Data | I/O | 6a | D4 | D5 | 6c | I/O | Data |

| Data | I/O | 7a | D6 | D7 | 7c | I/O | Data |

| Hold Acknowledge | O | 8a | /HLDA | INTA | 8c | O | Interrupt Acknowledge |

| In-/Out Write | O | 9a | /IOW | /MEMW | 9c | O | Memory Write |

| In-/Out Read | O | 10a | /IOR | /MEMR | 10c | O | Memory Read |

| ROM (Erzeugt von 8K-Karte) | O | 11a | /ROM | /IN | 11c | I | Input (Erzeugt von IO-Karte) |

| RAM (Erzeugt von 8K-Karte) | O | 12a | /RAM | /OUT | 12c | I | Output (Erzeugt von IO-Karte) |

| TRAP-Signal (Prio 1: Address 0024h) | I | 13a | TRAP | /RESOUT | 13c | O | Reset Out |

| nc | 14a | A18 | 14c | O | Erweiterung Siehe Entwurf: Forum VzEkC | ||

| Erweiterung | O | 15a | A19 | A16 | 15c | O | Erweiterung aus 16k + Urlader |

| Erweiterung aus 16k + Urlader | O | 16a | A17 | A0 | 16c | O | Address |

| Address | O | 17a | A1 | A2 | 17c | O | Address |

| Address | O | 18a | A3 | A4 | 18c | O | Address |

| Address | O | 19a | A5 | A6 | 19c | O | Address |

| Address | O | 20a | A7 | A8 | 20c | O | Address |

| Address | O | 21a | A9 | A10 | 21c | O | Address |

| Address | O | 22a | A11 | A12 | 22c | O | Address |

| Address | O | 23a | A13 | A14 | 23c | O | Address |

| Address | O | 24a | A15 | /INTR ok | 24c | O | Interrupt (Open Kollektor) für Interrupt Vektor-Karte |

| RST 7.5 (Prio 2: Address 003ch)) | I | 25a | RST 7.5 | INTR | 25c | I | Interrupt (Prio 5: Data-Byte C7/CF/D7/DF/E7/EF/F7/FF) |

| Ready (für Single-Step) | I | 26a | /READY | RST 5.5 | 26c | I | RST 5.5 (Prio 4: Address 002ch) |

| Reset In | I | 27a | /RESIN | RST 6.5 | 27c | I | RST 6.5 (Prio 3: Address 0034h) |

| Hold CPU | I | 28a | /HOLD | DTR | 28c | V24 aus Video 8.4 | |

| Erweiterung | O | 29a | Puls OUT | Rx | 29c | I | Receive serieller Port SID (CPU) |

| Erweiterung | 30a | Puls f. INT | Tx | 30c | O | Transmit serieller Port SOD (CPU) | |

| + 12 Volt | 31a | + 12 V | – 12 V | 31c | – 12 Volt | ||

| GND Pin A | 32a | GND_a | GND | 32c | GND Pin C |