Einleitung

Sind alle Baugruppen des MC-Baugruppensystems fertig und sorgfältig überprüft, so kann das Gesamtsystem in Betrieb genommen werden. Hierbei sollte man unbedingt schrittweise vorgehen, denn nur so lassen sich eventuell noch vorhandene Fehler finden.

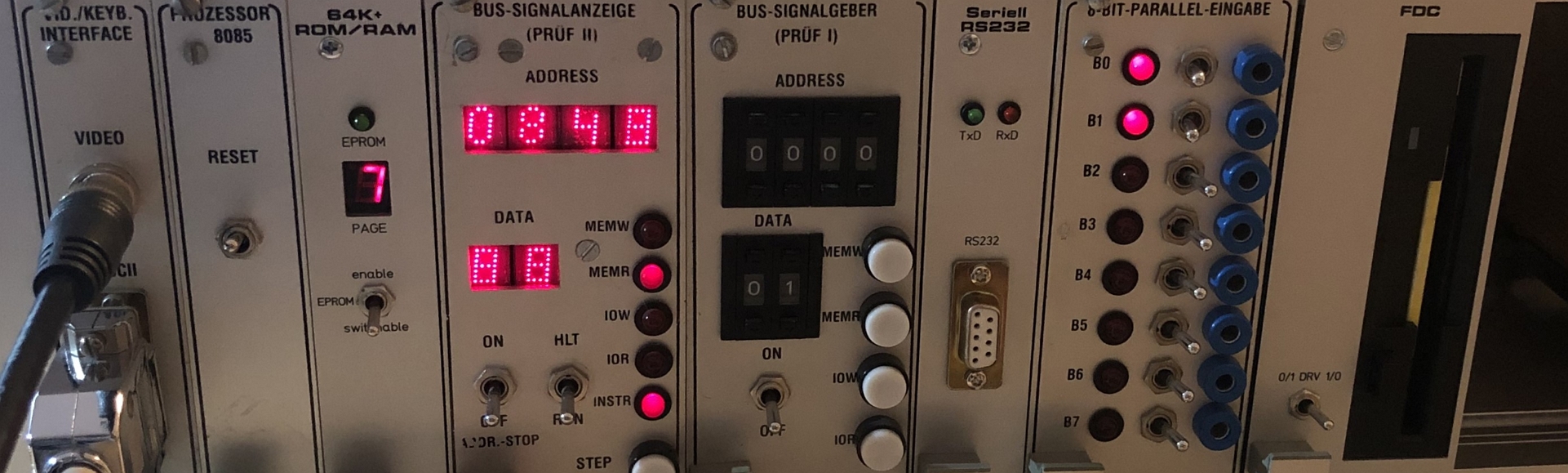

Der erste Prüfschritt beschränkt sich auf den Test des Zusammenspiels von Prozessor und RAM-Speicher. In weiteren Prüfschritten werden dann die Ausgabe und die Eingabe-Baugruppe in den Funktionstest mit einbezogen. Bei allen Prüfschritten werden mit Hilfe des Bus-Signalgebers kleine Testprogramme in den RAM-Speicher eingeschrieben. Anschließend wird das zusammenarbeiten der Baugruppen im Einzelschrittbetrieb über die Bus-Signalanzeige, und bei normaler Arbeitsgeschwindigkeit des Prozessors mit einem Oszilloskop verfolgt.

Erst danach wird das System in Verbindung mit dem Betriebsprogramm MAT 85 in Betrieb genommen und die Datensichtstation angeschlossen.

Vorkenntnisse

Die folgenden Kenntnisse und Fertigkeiten werden für die Durchführung dieser

System-Inbetriebnahme vorausgesetzt:

- Wirkungsweise und Bedienung des Bus-Signalgebers

- Wirkungsweise und Bedienung der Bus-Signalanzeige

- Wirkungsweise der CPU beim Abarbeiten eines Befehls

- Einstellen der Port-Adressen der Ein/Ausgabe-Baugruppen

- Einstellen der Basis-Adressen bei RAM/EPROM-Baugruppen

- Laden eines kleinen Programms in den RAM-Speicher mit dem Bus-Signalgeber

Diese Kenntnisse werden in den Abschnitten „Blockschaltbild und Wirkungsweise“

der entsprechenden fachpraktischen Übungen beschrieben.

Zusatzunterlagen

Im Anschluss an die Arbeitsblätter finden Sie die Bestückungspläne aller Baugruppen,

die für diese Inbetriebnahme-Übung benötigt werden.

Flussdiagramm für den Arbeitsablauf

Komponenten für die Inbetriebnahme

| Beschreibung | Bemerkung |

|---|---|

| Baugruppenträger mit Bus-Platine | BFZ/MFA 0.1 |

| Bus-Abschluss | BFZ/MFA 0.2 |

| Trafo-Einschub | BFZ/MFA 1.1 |

| Spannungsregelung | BFZ/MFA 1.2 |

| Prozessor 8085 | BFZ/MFA 2.1 |

| 8-K-RAM/EPROM bestückt mit Betriebssystem „MAT 85 Vers. 1.8“ | BFZ/MFA 3.1 |

| 8-K-RAM/EPROM bestückt mit 2-K-RAM | BFZ/MFA 3.1 |

| 8-Bit-Parallel-Ausgabe | BFZ/MFA 4.1 |

| 8-Bit-Parallel-Eingabe | BFZ/MFA 4.2 |

| Bus-Signalgeber | BFZ/MFA 5.1. |

| Bus-Signalanzeige | BFZ/MFA 5.2 |

| Adapterkarte | BFZ/MFA 5.3 |

| ASCII – Tastatur | BFZ/MFA 8.1 |

| Video-Interface | BFZ/MFA 8.2 |

| Video-Gerät | |

| Zweistrahl-Oszilloskop | |

| FPÜ „Prozessor 8085“ zur vertiefen des theoretischen Hintergrundes der einzelnen Arbeitsschritten | BFZ/MFA 2.1 |

Hinweise zum Arbeitsablauf

In dieser Übung werden Sie das Mikrocomputersystem schrittweise in Betrieb nehmen. Alle zur Inbetriebnahme vorgegebenen Arbeitsblätter enthalten:

- Angaben über den Sinn des jeweiligen Arbeitsschrittes oder der Messung

- Angaben über Vorbereitungen und einzustellende Bedingungen

- Anweisungen zu einzelnen Testschritten mit Erläuterungen der zugehörigen Ergebnisse.

Nach Beendigung eines Arbeitsabschnittes wird die notwendige Theorie zum vorangegangenen Inbetriebnahmeschritt behandelt. Es wird empfohlen, nach dem Durcharbeiten dieses Theorieteils ggf. die Arbeitsschritte noch einmal zu wiederholen.

Inbetriebnahme

Inbetriebnahme von CPU- und RAM-Baugruppe im Einzelschritt- und Normalbetrieb

Mit Hilfe des Bus-Signalgebers wird in den RAM-Speicher ein kleines Programm (Schleife) eingegeben. Hierzu wird die CPU vom System-Bus getrennt. Nach der Programmeingabe wird die Abarbeitung des Programms durch den Prozessor im Einzelschritt mit Hilfe der Bus-Signalanzeige und bei normaler Arbeitsgeschwindigkeit mit einem Oszilloskop verfolgt.

RAM-Baugruppe:

- Basisadresse mit den DIL-Schaltern auf 0000 stellen.

- RAM-Baustein 6116 in den Sockel IC8 stecken.

Adressbereich 0000-07FF

Bus-Signalanzeige:

- Mit den DIL-Schaltern S1 bis S16 die Adresse für den Adressvergleicher auf 0000 stellen.

Folgende Baugruppen in den Baugruppenträger stecken:

- Bus-Signalgeber

- Bus-Signalanzeige über Adapterkarte

- Prozessor 8085

- RAM-Baugruppe (nach Umstellung der Basisadresse).

Betriebsspannung einschalten.

Schalten Sie den RUN/HLT-Schalter an der Bus-Signalanzeige auf RUN. Die CPU arbeitet jetzt mit „Normalgeschwindigkeit“.

Oszilloskopieren Sie mit einem Zweistrahl-Oszilloskop der Reihe nach die in folgender Tabelle angegebenen Signale. Dabei wird das Ausgangssignal des Adressvergleichers auf der Bus-Signalanzeige für die externe Triggerung des Oszilloskops verwendet. Aufgrund der Schalterstellung der DIL-Schalter auf der Bus-Signalanzeige liefert der Adressvergleicher immer dann ein Triggersignal, wenn die Adresse 0000 am Adressbus ansteht.

Das Oszilloskop sollte folgenden Signalverlauf anzeigen:

Diskussion der Messergebnisse

Nach dem Einschalten der Versorgungsspannung sendet die CPU 8085 über den Adressbus die Adresse 0000H aus und aktiviert das Steuersignal MEMR. Daraufhin speichert sie das Datenwort aus der adressierten Speicherzeile intern ab. Dieses Datenwort wird als Befehl aufgefasst. Der Befehlsdecoder der CPU entschlüsselt den Befehl und löst den notwendigen weiteren Steuerungsablauf aus. Handelt es sich z.B. um einen Ein-Byte-Befehl, so wird er sofort ausgeführt; ist es dagegen ein Drei-Byte-Befehl, so muss die CPU zunächst noch zwei weitere Bytes aus dem Speicher holen, bevor sie den Befehl ausführt. Danach liest die CPU das nächste Befehlsbyte aus dem Speicher.

Damit die CPU im Sinne des Anwenders arbeitet, muss in die Speicherzeilen eine entsprechend sinnvolle Befehlsfolge, ein Programm, geladen werden.

Will man die Arbeitsweise mit einem Oszilloskop prüfen, so muß das Programm die CPU veranlassen, eine sich periodisch wiederholende Befehlsfolge zu durchlaufen. Eine solche Befehlsfolge heißt Programmschleife oder kurz Schleife.

Im Arbeitsschritt A1 bestand diese Schleife aus einem einzigen Befehl, nämlich dem Drei-Byte-Befehl

C3 00 00:

springe zu dem Befehl, dessen Adresse in den beiden folgenden Bytes angegeben wird, also zur Adresse 0000.

Da das Befehlsbyte C3 unter der Adresse 0000 abgespeichert ist, veranlasst dieser Befehl die CPU immer wieder nach 0000 zurückzuspringen; es entsteht somit eine Schleife.

Über die Einzelschrittsteuerung und die angezeigten Adress-, Daten- und Steuersignale konnten Sie den Ablauf des Programms gut verfolgen. Das Oszilloskop-Diagramm zeigt Ihnen dagegen die Signalfolge, die Sie bei Normalbetrieb der CPU mit dem Oszilloskop aufnehmen konnten.

Das Signal am Messpunkt 1 der Signalanzeige wechselt immer dann auf H-Pegel, wenn der Adressbus die Adresse 0000 führt. Diese Adresse haben Sie dem Adressvergleicher auf der Bus-Signalanzeige mit den 16 DIL-Schaltern vorgegeben. Das Signal am Messpunkt 1 ist das Ausgangssignal dieses Adressvergleichers. Es wurde zur externen Triggerung des Oszilloskops verwendet. Dadurch haben alle aufgenommenen Signale den richtigen Zeitbezug zueinander.

Das ALE-Signal nimmt jeweils zu Beginn eines neuen Maschinenzyklusses für eine halbe Taktperiode (CLK) H-Pegel an. Sie können deutlich erkennen, daß der Maschinenzyklus M1 vier Taktperioden (T1 – T4) andauert und die Zyklen M2 und M3 nur je drei. Ursache dafür ist die Befehlsentschlüsselung, die während des Taktzyklusses T4 erfolgt.

Ein L-Pegel auf MEMR zeigt an, dass die CPU Daten aus dem Speicher liest. Um den Drei-Byte-Befehl zu lesen, sind drei Speicherzugriffe erforderlich. Die jeweils gelesenen Datenworte sind in den Signalverlauf für MEMR eingetragen. Die Pegel auf den Adressleitungen A0 und A1 zeigen an, zu welchen Zeiten die Adressen 0, 1 und 2 ausgegeben werden.

Inbetriebnahme von CPU, RAM und Ausgabe-Baugruppe

In den RAM-Speicher wird ein Programm geladen, das die CPU veranlasst, in einer Schleife den Datenwert 55 (Hex) an die Ausgabe-Baugruppe auszugeben. Die Prüfung erfolgt wieder im Einzelschritt- und Normalbetrieb.

Stellen Sie bei der „8-Bit-Parallelausgabe“ die Port-Adresse 13H ein. Stecken Sie die Baugruppe zusätzlich in den Baugruppenträger und schalten Sie die Betriebsspannung ein.

Mögliche Experimente:

- Ändern Sie das Programm so ab, daß die bisher dunklen LED’s leuchten.

- Laden Sie ein Programm, das in schneller Folge abwechselnd zuerst die LED’s B0, B2, B4, B6 und dann die LED’s B1, B3, B5 u. B7 leuchten lässt.

Diskussion der Beobachtungsergebnisse

Im Arbeitsschritt A2 wurde die 8-Bit-Parallel-Ausgabe in die Prüfung mit einbezogen.

Das eingegebene Prüfprogramm bestand aus drei Befehlen.

- Befehl: Lade den Datenwert 55 Hin den Akkumulator der CPU.

- Befehl: Gib den Wer~ der sich im Akkumulator befindet, an die Ausgabebaugruppe aus, deren Port-Adresse 13 beträgt.

- Befehl: Springe zurück zum 1. Befehl und fahre dort mit der Programmbearbeitung fort.

Die Kommentare zu den Anzeigen im Einzelschrittbetrieb erklären die Arbeitsweise des Programms.

Zu den Experimenten:

Mit dem zweiten Byte des 1. Befehls lässt sich bestimmen, welche LED’s am Ausgabeport leuchten. Zur Durchführung des 1. Experimentes ist folgendes Programm erforderlich:

| Adresse | Daten |

|---|---|

| 0000 | 3E |

| 0001 | AA |

| 0002 | D3 |

| 0003 | 13 |

| 0004 | C3 |

| 0005 | 00 |

| 0006 | 00 |

Zur Durchführung des 2. Experimentes muss das Programm wie folgt eingegeben werden:

| Adresse | Daten | Bemerkung |

|---|---|---|

| 0000 | 3E | Akku laden |

| 0001 | 55 | mit dem Wert für die Bits B0, B2, B4 |

| 0002 | D3 | Akku an |

| 0003 | 13 | Port 13 ausgeben |

| 0004 | 3E | Akku laden |

| 0005 | AA | mit dem Wert für die Bits B1, B3, B5 .. |

| 0006 | D3 | Akku an |

| 0007 | 13 | Port 13 ausgeben |

| 0008 | C3 | Rücksprung zum Start (0000) |

| 0009 | 00 | |

| 000A | 00 |

Inbetriebnahme von CPU, RAM, Ausgabe- und Eingabe-Baugruppe

In den RAM-Speicher wird ein Programm geladen, das die CPU veranlasst, in einer Schleife Daten von der Eingabe-Baugruppe zu lesen und sie an der Ausgabe-Baugruppe auszugeben. Die Prüfung erfolgt im Einzelschritt- und Normalbetrieb.

Stellen Sie bei der „8-Bit-Parallel-Eingabe“ die Portadresse 12 H ein. Stecken Sie die Baugruppe zusätzlich in den Baugruppenträger, schalten Sie die Betriebsspannung ein.

Oszilloskopieren Sie der Reihe nach die in folgender Tabelle angegebenen Signale. Das Ausgangssignal des Adressvergleichers der Bus-Signalanzeige dient wieder als Triggersignal für die externe Triggerung. Tragen Sie die Signalverläufe in das vorbereitete Diagramm ein.

| Signal | Messbar an | Bemerkung |

|---|---|---|

| U MP1 | MP1-Signalanzeige | Externer Triggereingang |

| ALE | MP3-Signalanzeige | Kanal 1 |

| /MEMR | MP7-Signalanzeige | Kanal 2 |

| /IOR | MP6-Signalanzeige | Kanal 2 |

| /IOW | MP5-Signalanzeige | Kanal 2 |

| A0 | 16c – Adapter | Kanal 2 |

| A1 | 17a – Adapter | Kanal 2 |

| A2 | 17c – Adapter | Kanal 2 |

| A4 | 18c – Adapter | Kanal 2 |

Diskussion der Meßergebnisse

Im Arbeitsschritt A3 wurde die 8-Bit-Parallel-Eingabe-Baugruppe mit in die Prüfung einbezogen. Das Prüfprogramm bestand aus drei Befehlen.

- Befehl: Lies die acht Bits des Eingabe-Ports mit der Portadresse 12 (das gelesene Datenwort wird im Akku gespeichert).

- Befehl: Gib den Akkuinhalt an das Ausgabe-Port mit der Portadresse 13.

- Befehl: Springe zum 1. Befehl zurück.

Im Einzelschrittbetrieb ließ sich die Arbeitsweise dieses Programms gut verfolgen. Im Betrieb mit normaler Prozessorgeschwindigkeit zeigt sich, dass hier durch ein Programm zwei Baugruppen miteinander „verdrahtet“ worden sind; jeder Schaltereingabe folgt, anscheinend ohne Zeitverzögerung, die entsprechende Anzeige.

Versuchen Sie einmal, das folgende Programm zu laden und seine Wirkung zu erkunden.

| Adresse | Daten | Bemerkung |

|---|---|---|

| 0000 | DB | Lade Akku mit von Eingabebaugruppe |

| 0001 | 12 | mit der Adresse 12h |

| 0002 | 2F | Invertiere den Akku-Inhalt |

| 0003 | D3 | Schreibe Akku an Ausgabebaugruppe |

| 0004 | 13 | mit der Adresse 13h |

| 0005 | C3 | Sprung zur Adresse 0000h |

| 0006 | 00 | |

| 0007 | 00 |

Das Diagramm zeigt die Oszillogramme, die Sie bei Normalbetrieb der CPU aufnehmen konnten. Der auf die Adresse 0000 eingestellte Adressvergleicher liefert wieder das Triggersignal zur Sicherstellung des richtigen Zeitbezugs. Die eingetragenen Bezeichnungen IN 12, OUT 13 und JMP 0000 sind leicht merkbare Kurzbezeichnungen für die drei Befehle dieses Programms. Die Schreibweise der Befehle in dieser Weise nennt man Mnemo-Code. Die Abkürzungen entstammen der englischen Sprache, JMP z.B. ist die Abkürzung von jump (= springe).

Dem Verlauf des ALE-Signals kann man entnehmen, dass die Befehle IN und OUT je drei Maschinenzyklen enthalten. Während des M1-Zyklusses werden die Befehlsworte DB bzw. D3 gelesen und entschlüsselt; während M2 werden die Portadressen 12 bzw. 13 gelesen, und während M3 werden die Befehle ausgeführt. Die Ausführung des IN-Befehls erfolgt mit dem Steuersignal /IOR, die des OUT-Befehls mit dem Steuersignal /IOW.

Den Pegeln der Adressenleitungen können Sie entnehmen, welche Adresswerte die CPU im Verlauf der Programmbearbeitung ausgibt Die Ausführung des Befehls IN erfordert es, dass nach Ausgabe der Adresse 1 zunächst die Port-Adresse 12 ausgesendet wird, ehe unter der Adresse 2 der OUT-Befehl gelesen wird. Auch die Ausführung dieses Befehls unterbricht das „normale“ Hochzählen des Adresszählers der CPU.

Inbetriebnahme von CPU-, RAM- und EPROM-Baugruppe und Datensichtstation und MAT 85

In diesem Prüfschritt wird die CPU durch das Betriebsprogramm MAT 85 gesteuert. Dieses Betriebsprogramm befindet sich in den EPROM’s der EPROMBaugruppe. Es beginnt bei der Speicheradresse 0000 und erfordert RAM-Speicher im letzten K-Byte-Block des Systemspeichers (FC00 – FFFF). Die RAM-Baugruppe ist deshalb so umzurüsten, daß dieser Speicherbereich von einem RAM-IC überdeckt wird.

RAM-Baugruppe:

- Basisadresse auf EOOO stellen; (letzte 2K des Bereichs)

- RAM-IC (6116) in Sockel IC11 stecken;

EPROM-Baugruppe:

- Basisadresse auf 0000 stellen;

- überprüfen, ob die EPROM’s in der richtigen Reihenfolge eingesteckt sind.

Stecken Sie folgende Baugruppen in den Baugruppenträger:

- Prozessor 8085-Baugruppe

- RAM-Baugruppe

- EPROM-Baugruppe

- Video-Interface, zum Anschliessen von Tastatur und Bildschirm

- Bus-Signalanzeige

Betriebsspannung und Bildschirm einschalten.

Diskussion der Beobachtungsergebnisse

Wenn die oben aufgeführten dargestellten Kommandos auf dem Bildschirm erscheinen, ist die Inbetriebnahme des Systems abgeschlossen.

Wenn die Kommandos nicht erscheinen, überprüfen Sie noch einmal die folgenden Angaben:

CPU-Baugruppe:

- V-24-Brücken vorhanden?

- Elko C3 = 4,7 μF?

- IC1 und IC2 in Ordnung?

(evtl. je ein neues IC einsetzen)

Video-Interface:

- Lötbrücken P0-P1, P4-P5, P6-P7

- P6-P10 u. P12-P13 verbunden?

EPROM-Baugruppe:

- Basis-Adresse auf 0000?

- Brücken P1-P2 u. P7-P8 vorhanden?

- EPROM-Reihenfolge richtig?

RAM-Baugruppe:

- Basis-Adresse auf E000?

- Brücken P3-P4 u. P5-P6 vorhanden?

- RAM auf Steckplatz IC11?

Sollten alle Punkte erfüllt sein, müssen Sie die Einzelinbetriebnahmen der Baugruppen noch einmal durchführen.

Baugruppen

CPU-Baugruppe

RAM-Baugruppe

Für die Erstinbetriebnahme Adresse auf 0000h einstellen (Schalter auf L)

Ausgabe-Baugruppe

Eingabe-Baugruppe

BUS-Signalanzeige – Baugruppe

BUS-Signalgeber – Baugruppe

EPROM – Baugruppe (ROM)

Video-Interface – Baugruppe