Einleitung

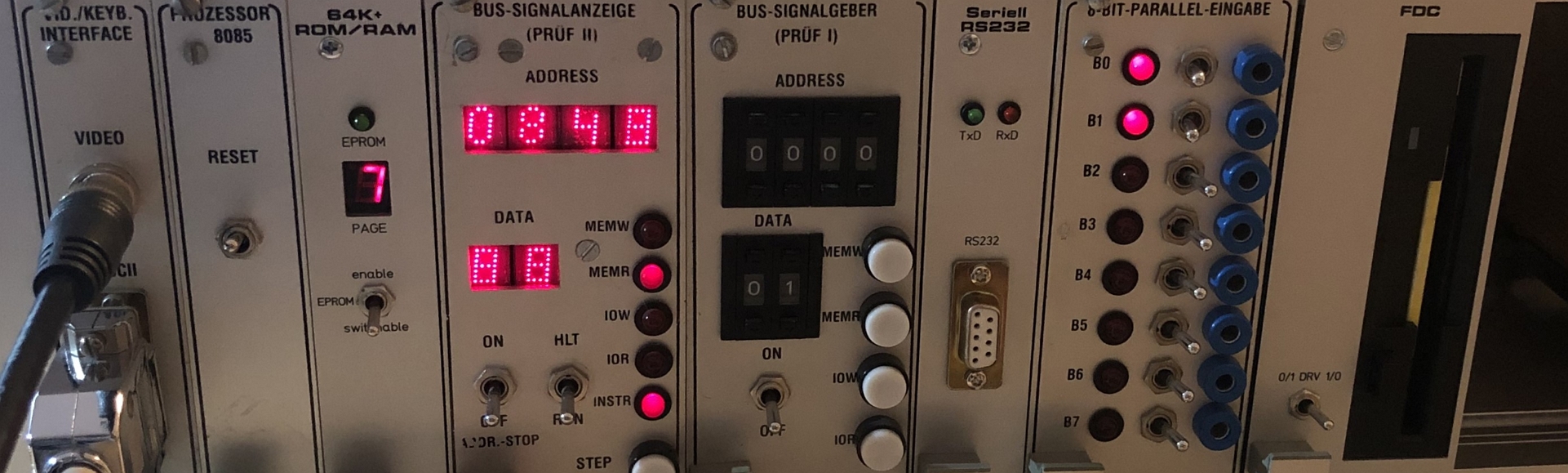

Jeder vollständig aufgebaute Mikrocomputer besitzt neben der Zentraleinheit (CPU) und den verschiedenen Speicherbaugruppen auch Eingabe- und Ausgabe-Einheiten, über die der Datenfluss zum Prozessor hin und vom Prozessor weg stattfindet. Eingabe- und Ausgabe-Einheiten werden in der Mikrocomputertechnik häufig mit dem englischen Begriff »Port« (Hafen, Öffnung) bezeichnet; sie sind »Nahtstellen« zwi- schen Geräten und Anlageteilen außerhalb des Mikrocomputers und dem Mikrocomputer-System selbst.

Die Schaltung der 8-Bit-Parallel-Eingabe-Baugruppe

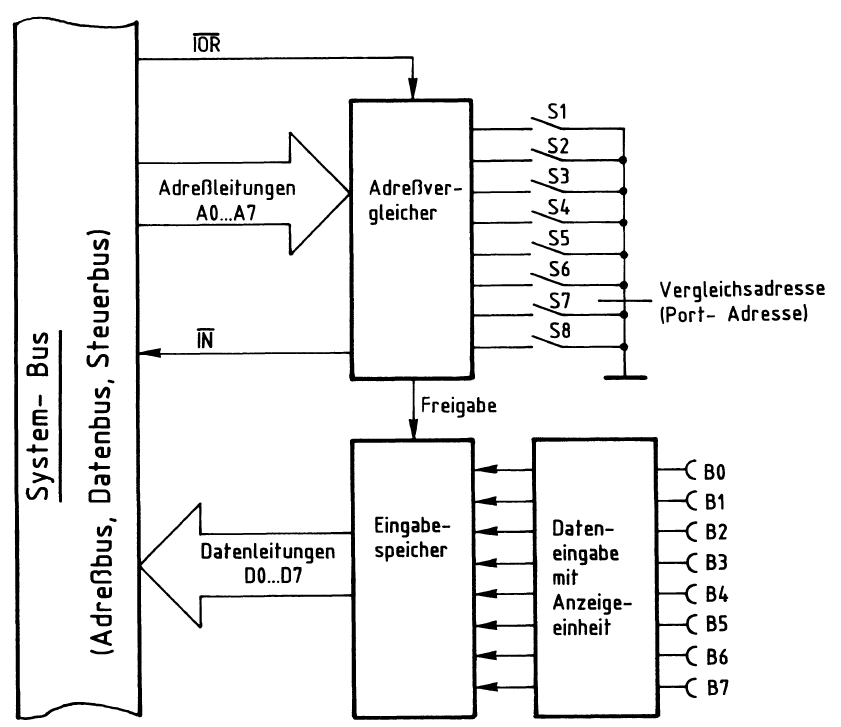

Diese Baugruppe besteht aus den Schaltungsteilen Dateneingabe mit Anzeige-Ein- heit, Eingabespeicher und Adreßvergleicher: Bild 1.

Bild 1: Blockschaltbild der Baugruppe »8-Bit-Parallel-Eingabe«.

Über die Steckbuchsen B0…B7 kann eine Datenquelle an die Eingabebaugruppe angeschlossen werden. Die eingegebene Daten-Bitkombination – das Datenwort – wird im Funktionsblock »Dateneingabe mit Anzeigeeinheit« durch Leuchtdioden angezeigt und an den Eingabespeicher abgegeben. Wenn das Signal »Freigabe« erfolgt, schaltet der Eingabespeicher die acht Datenbits über die Leitungen D0…D7 auf den System-Bus. Das Freigabesignal stammt aus dem Block »Adressvergleicher«, der folgende Aufgabe und Wirkungsweise hat:

In einem Mikrocomputer sind häufig mehrere Eingabebaugruppen vorhanden, die ihre Daten auf den Datenbus geben sollen. Um Kurzschlüsse auf den Datenleitungen zu vermeiden, darf jeweils nur immer eine Datenquelle mit dem System-Bus verbun- den sein. Erst wenn deren Daten verarbeitet sind, wird die nächste Baugruppe zur Abgabe ihrer Daten veranlaßt. Zur Steuerung des Datenempfangs verwendet der Mikroprozessor das Signal IOR (In/Out-Read, Eingabe/Ausgabe Lesen) und die acht Adreßleitungen A0 …A7. Aufgabe des Adreßvergleichers ist es nun, mit Hilfe dieser Signale den Eingabespeicher zu steuern.

Eine Freigabe des Eingabespeichers erfolgt nur dann, wenn:

- das Signal IOR L-Pegel führt und

- die Bitkombination der Adreßleitungen A0 bis A7 mit der durch die Schalter S1 bis S8 eingestellten Bitkombination übereinstimmt; man sagt auch, wenn die Baugruppe adressiert ist.

Mit den acht Schaltern lassen sich 2^8 = 256 verschiedene Bitkombinationen oder

Adressen einstellen. Diese Adressen nennt man auch Port-Adressen. Beim Einsatz mehrerer Eingabebaugruppen ist beim Einstellen der Port-Adressen (mit S1 … S8) darauf zu achten, dass jeder Baugruppe eine andere Adresse zugeordnet wird. Mit dem Pegel auf der Leitung IN kann man in einem Mikrocomputer-Demonstrationsmodell eine Anzeige ansteuern, die kennzeichnet, daß eine Eingabebaugruppe angegesprochen.

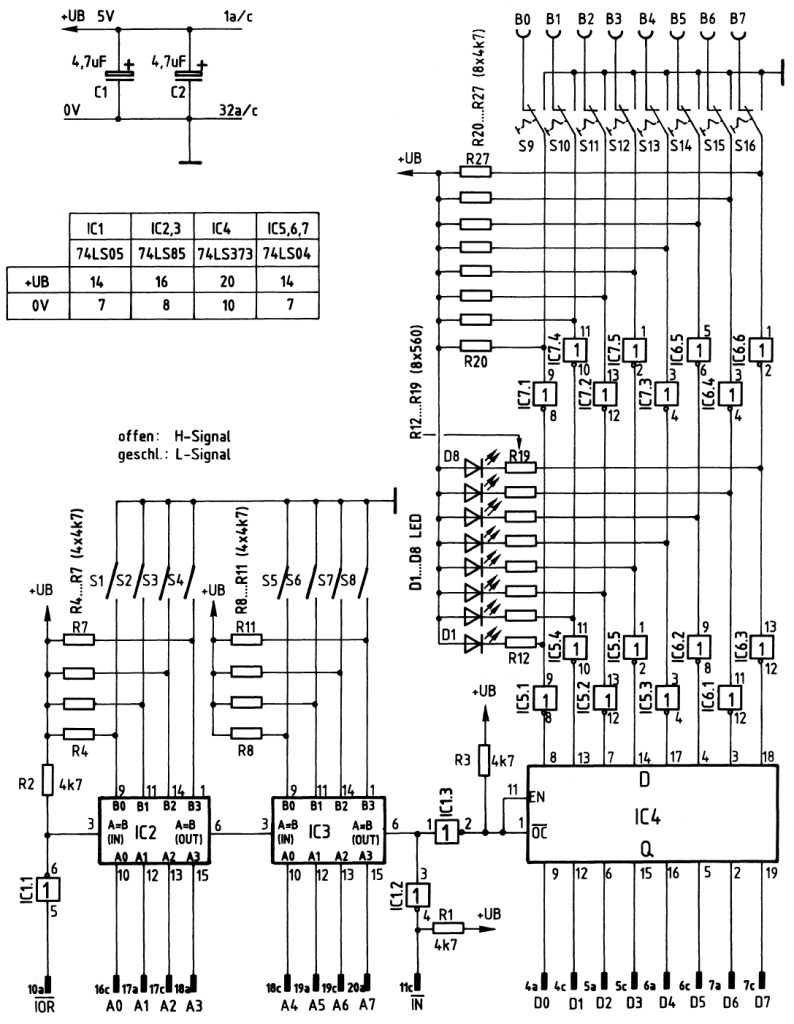

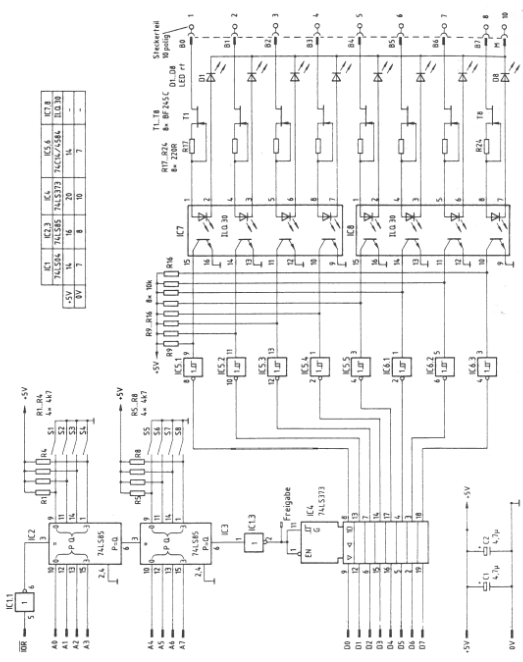

Bild 2 zeigt den Stromlaufplan der Baugruppe 8-Bit-Parallel-Eingabe, der zu allen folgenden Erläuterungen mit herangezogen werden sollte.

Stromlaufplan

Bild 2: Der Stromlaufplan der 8-Bit-Parallel-Eingabe.

Dateneingabe mit Anzeige-Einheit

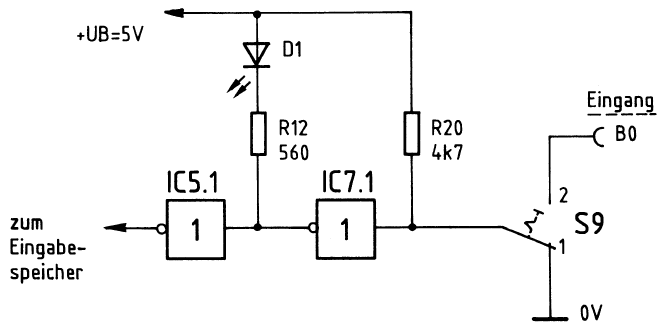

Bild 3 zeigt den Stromlaufplan der »Dateneingabe mit Anzeige-Einheit«, allerdings nur für ein Bit. Diese Schaltung ist insgesamt 8mal vorhanden; dargestellt ist sie lediglich für das niedrigstwertige Bit B0.

Bild 3: Das Prinzip der Dateneingabe mit Anzeige-Einheit.

In der gezeichneten Schalterstellung von S9 (Bild 3) ist die Eingangsbuchse BO abge- schaltet, und der Eingang von IC7.1 liegt auf L-Potential (0 V). Hierdurch führt der Ausgang dieses Inverters ein H-Signal, und die LED Dl leuchtet nicht. Das IC5.l wird mit dem H-Signal angesteuert, invertiert nochmals und gibt ein L-Signal an den Eingabespeicher ab.

Wenn S9 in die Schalterstellung 2 umgeschaltet ist, ist B0 angeschlossen. Hierbei müssen zwei Betriebsfälle unterschieden werden: entweder offener Eingang, d.h. kein Anschluß einer externen Datenquelle, oder Anschluß einer Datenquelle an B0. Bei offener Eingangsbuchse erhält der Eingang von IC7.1 über R20 einen H-Pegel. Hierdurch führt der Ausgang ein L-Signal und Dl leuchtet. IC5.1 invertiert nochmals und gibt ein H-Signal an den Eingabespeicher ab.

Bei Anschluß einer Datenquelle an B0 sind folgende Punkte zu beachten:

- Der Pegel an den Eingangsbuchsen muß zwischen 0V und +5 V liegen, also TTL-Pegel entsprechen.

- Die externe Datenquelle muß bei einem L-Signal an BO einen Strom aufnehmen bzw. nach Masse durchschalten können, der sich aus dem Eingangsstrom von IC7.1 und dem Strom durch R20 ergibt. Zusammen beträgt dieser Strom etwa 1,5 … 2 mA; somit entspricht eine Eingangsbuchse lastmäßig zwei TTL-Gatter-Eingängen.

- Viele Datenquellen besitzen einen sogenannten Tristate-Ausgang. Bei einem sol- chen gibt es neben den Signalzuständen H und L noch einen dritten Zustand, der oft mit »High-Z« bezeichnet wird. High-Z bedeutet, daß der Ausgang hochohmig geschaltet ist. Das aber entspricht einer offenen Eingangsbuchse und wird als H-Pegel bewertet.

- An die Eingangsbuchsen der Baugruppe können sowohl gewöhnliche als auch open-collector-Schaltkreise angeschlossen werden, da der erforderliche Kollektor- Arbeitswiderstand innerhalb der Eingabekarte vorhanden ist.

Durch das Hintereinanderschalten der beiden Inverter IC7.1 und IC5.l (siehe Bild 3) wird das Eingangssignal letztlich ohne Invertierung an den Eingabespeicher abgegeben. IC7.1 dient dabei als LED-Treiber, damit der LED-Strom von ca. 8 mA nicht direkt am Eingang geschaltet werden muß. IC5.l hebt die durch IC7.l bewirkte Signalumkehr wieder auf.

Eingabespeicher

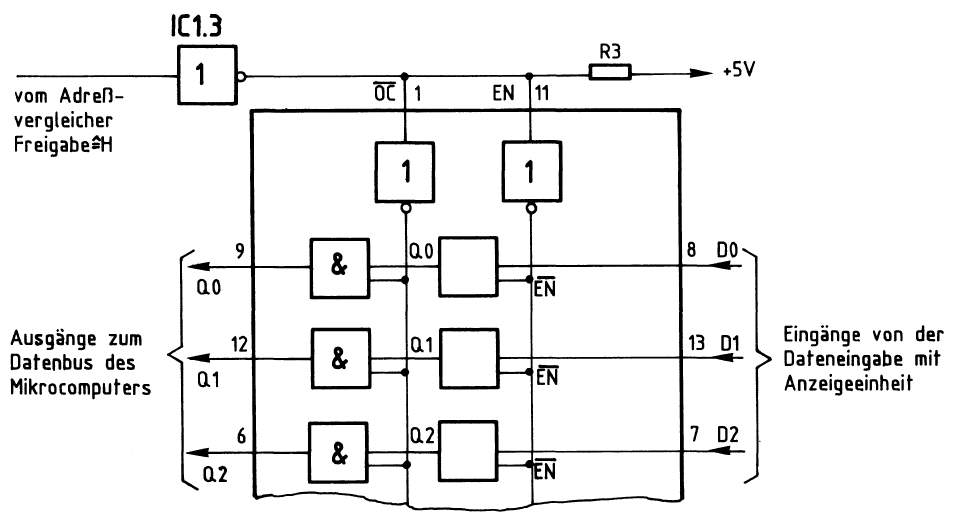

Die mit den Schaltern oder über die Eingangsbuchsen eingegebenen Daten werden in einem Eingabespeicher (siehe Bild 1) gespeichert, bis der Mikrocomputer die Daten abruft. Bild 4 zeigt einen Schaltungsauszug des Eingabespeichers und die dazugehörige Funktionstabelle.

Bild 4: Der Eingabespeicher und die Funktionstabelle des ICs 74LS373.

Der Schaltkreis 74LS373 (Bild 4) enthält acht zustandsgesteuerte D-Flipflops mit getrennten Eingängen D0 … 7 und getrennten Ausgängen Q0 … Q7, aber gemein- samen Steuereingängen OC und EN. Die Steuereingänge OC und EN besitzen fol- gende Wirkungsweise:

0C ist eine Abkürzung von »Output Control« und bedeutet »Steueranschluss für die Ausgänge der Flipflops (Q0 … Q7)«. Wenn Q0 L-Signal erhält, sind die Ausgänge der D-Flipflops (Q0 … Q7) mit den entsprechenden IC-Anschlüssen (Q0 … 7) verbunden. Die Daten der Flipflops gelangen dann zum Datenbus des Mikrocomputers. Der Betriebszustand »L-Signal an Q0« tritt aber nur dann ein, wenn der Mikroprozessor die Daten der Baugruppe liest; dieser Betriebszustand wird vom Prozessor gesteuert.

In allen anderen Fällen erhält der Anschluß OC ein H-Signal, und die acht Flipflop- Ausgänge sind innerhalb des ICs vom Datenbus getrennt. Sie befinden sich dann im dritten Signalzustand »High-Z«, da der Baustein Tristate-Ausgänge besitzt (s.o.).

EN ist eine Abkürzung des Wortes »enable« und bedeutet »Steueranschluß für die Eingänge der Flipflops«. Enable heißt »ermöglichen«. Aus diesen Zusammenhängen kann die Wirkungsweise des Anschlusses EN abgeleitet werden: Bei einem H-Signal an EN werden die Daten der Eingänge D0 … D7 von den Flipflops zustandsgesteuert übernommen, während bei L-Signal an EN die Eingänge der Flipflops abgeschaltet sind. Zustarldsgesteuert bedeutet, daß der Zustand H oder L an den Eingängen der Flipflops sogleich angenommen bzw. gespeichert wird, ohne daß eine bestimmte Taktflanke eintreffen muß.

In dieser Baugruppe sind die beiden Steueranschlüsse OC und EN miteinander ver- bunden und werden über ICl.3 vom Adreßvergleicher angesteuert. Dadurch ergeben sich folgende Betriebszustände:

- H-Signal an OC/EN (Baugruppe nicht adressiert bzw. gelesen):

Die Eingänge der acht Flipflops sind aktiviert, und die Daten von D0 … D7 werden übernommen und gespeichert. Wenn sich die Eingangssignale ändern, wird auch der Inhalt der Flipflops verändert. Die Ausgänge Q0 … Q7 der Flipflops sind jedoch vom Datenbus getrennt. Der Prozessor erhält keine Daten von der Baugruppe; in ihren D-Flipflops stehen jedoch immer aktuelle Daten zur Verfügung.

- L-Signal an OC/EN (Baugruppe adressiert und gelesen):

Die Ausgänge der acht Flipflops sind zum Datenbus des Mikroprozessors durchgeschaltet, die Eingänge jedoch abgetrennt. Der Mikroprozessor liest die Daten der Baugruppe und verhindert durch gleichzeitige Eingangsblockade, daß sich die Daten beim Lesen noch ändern können. Durch das Lesen werden die Daten der Flipflops nicht gelöscht.

Bei einem erneuten H-Signal an OC/EN werden von den Flipflops stets die aktuellen Eingangsdaten übernommen und damit die alten Daten überschrieben.

Adressvergleicher

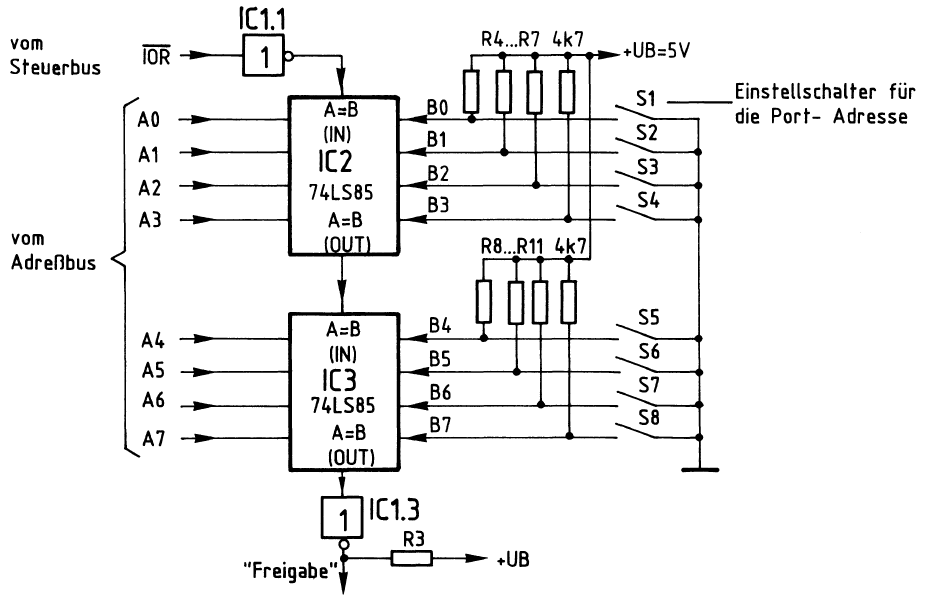

Bild 5 zeigt den Stromlaufplan des Adressvergleichers

Bild 5: Der Adreßvergleicher der Eingabe-Baugruppe.

Der jeweilige Ausgang der beiden hintereinander geschalteten 4-Bit-Vergleicher (A=B OUT) führt nur dann H-Pegel, wenn die folgenden beiden Bedingungen erfüllt sind:

- Der Eingang »A=B IN« muß H-Signal führen;

- die logischen Signale der Eingänge A und B müssen paarweise gleich sein, also A0 = B0, A1 = B1 usw.

Zum Lesen der Daten einer Eingabebaugruppe steuert der Mikroprozessor das Signal IOR auf L-Pegel und schaltet außerdem die Adresse der gewünschten Eingabebau- gruppe auf die Adreßleitungen A0 bis A7.

Das L-Signal, das dann an IOR auftritt, wird von ICl.1 invertiert, und der Eingang »A=B IN« von IC2 erhält H-Pegel. Wenn jetzt die Pegel der vier Adressenpaare A0-B0, Al-Bl, A2-B2 und A3-B3 übereinstimmen, sind beide genannten Bedingungen erfüllt, und IC2 gibt an seinem Ausgang »A=B OUT« ein H-Signal ab. Hiermit wird der Eingang »A=B IN« von IC3 angesteuert. Wenn die Pegel der vier Adressenpaare A4-B4, A5-B5, A6-B6 und A7-B7 ebenfalls übereinstimmen, erscheint auch am Ausgang »A=B OUT« von IC3 ein H-Signal. Es wird von ICl.3 invertiert und löst mit L-Pegel die Freigabe des Eingabespeichers aus.

Die acht Widerstände R4 … R11 erzeugen bei geöffneten Schaltern S1 … S8 jeweils H-Pegel an den Eingängen B0…B7. Je nach Schalterstellung kann somit eine Ver- gleichs- oder Port-Adresse zwischen 00000000 (binär) und 11111111 (binär) eingestellt werden, die mit der Adresse von A0 … A7 verglichen wird. Bei Gleichheit wird, wenn die Leitung IOR L-Pegel führt, das Freigabe-Signal ausgelöst.

Drückt man die Port-Adresse nicht binär, sondern hexadezimal aus, so kann sie mit den Schaltern zwischen 00 und FF eingestellt werden. Das Hintereinanderschalten der beiden 4-Bit-Vergleicher wird häufig »Kaskadierung« genannt; der Eingang »A=B IN« heißt dann »Kaskadierungs-Eingang«. Im Prinzip können auf diese Weise be- liebig große Adreßvergleicher aufgebaut werden. Außer den »A=B«-Ein- und Ausgängen besitzen die ICs vom Typ 74LS85 noch Ein- und Ausgänge für »A>B« und »A<B«, die in dieser Baugruppe jedoch nicht benutzt werden.

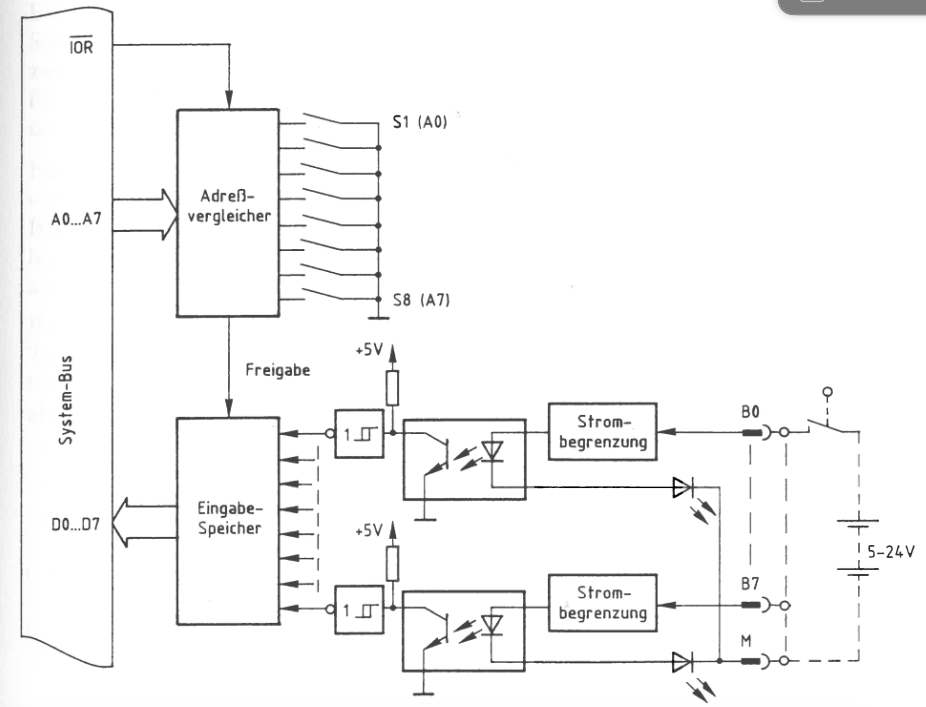

Die galvanische Trennung der Eingänge

Die 8-Bit-Parallel-Eingabe-Baugruppe mit galvanisch getrennten Eingängen ist für den Anschluß von Modellen und Anlagen an den Mikrocomputer vorgesehen. Die Baugruppe sollte immer dann eingesetzt werden, wenn die Gefahr von Stör-Einkopp- lungen besteht, wie z.B. beim Schalten von induktiven Lasten. Darüber hinaus wird sie notwendig, wenn Sensoren und Signalgeber mit externen Betriebsspannungen an den Mikrocomputer angeschlossen werden sollen. Zur galvanischen Trennung besitzen die acht Eingänge Optokoppler.

Die Eingangsspannung der Baugruppe darf bei der hier vorgestellten Ausführung bis zu 24 V betragen (Gleichspannung), wobei Werte zwischen 0 V und 2 V dem L-Pegel und Werte zwischen 5 V und 24 V dem H-Pegel entsprechen. Der maximale Ein- gangsstrom bei H-Pegel beträgt ca. 10 mA. Da diese Werte weitgehend den Daten industrieüblicher SPS-Steuerungen entsprechen, ist die Baugruppe auch für den Aus- bau des Mikrocomputers zur SPS-Steuerung geeignet (vgl. Kapitel 3).

Bei offenem Eingang (z.B. B0) fließt im Eingangskreis kein Strom, und der Fototran- sistor des Optokopplers ist gesperrt. Hierdurch erhält der Eingang des invertierenden Schmitt-Triggers H-Pegel und der Eingang des Eingabe-Speichers L-Pegel. Wird z.B. an B0 eine Spannung zwischen 5 V und 24 V angelegt, so fließt ein auf ca. 10 mA begrenzter Strom durch die LED des Optokopplers und durch die Kontroll-LED (auf der Frontplatte der Baugruppe). Die Optokoppler-LED steuert den Fototransistor durch, so daß der Eingang des invertierenden Schmitt-Triggers nun L-Pegel und der Eingang des Eingabe-Speichers H-Pegel erhält.

Die Eingabe-Daten gelangen nur bei Freigabe des Eingabe-Speichers auf den Daten- Bus. Die Freigabe erfolgt, wie oben beschrieben, wenn der Prozessor die richtige Port-Adresse (mit S1 bis S8 einstellbar) und das Steuersignal IOR ausgibt

Bild 6: Das Blockschaltbild der 8-Bit-Parallel-Eingabe-Baugruppe mit galvanischer Trennung der Eingangs-Signale vom Mikrocomputer-System.

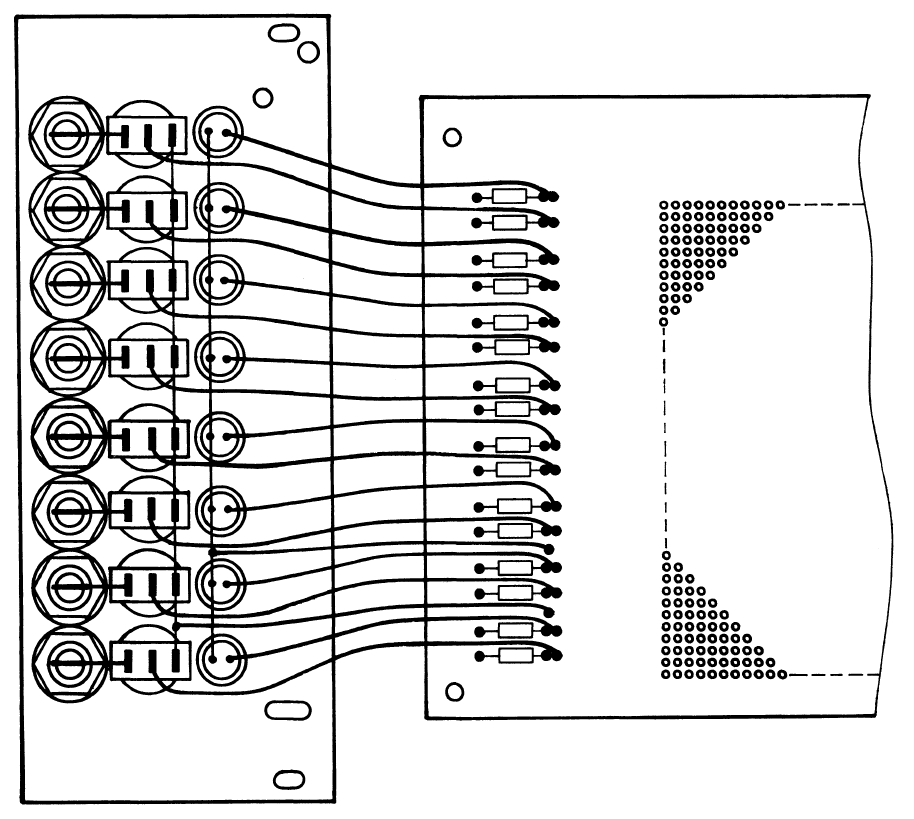

Bild 7: Der Stromlaufplan der 8-Bit-Parallel-Eingabe mit galvanischer Trennung

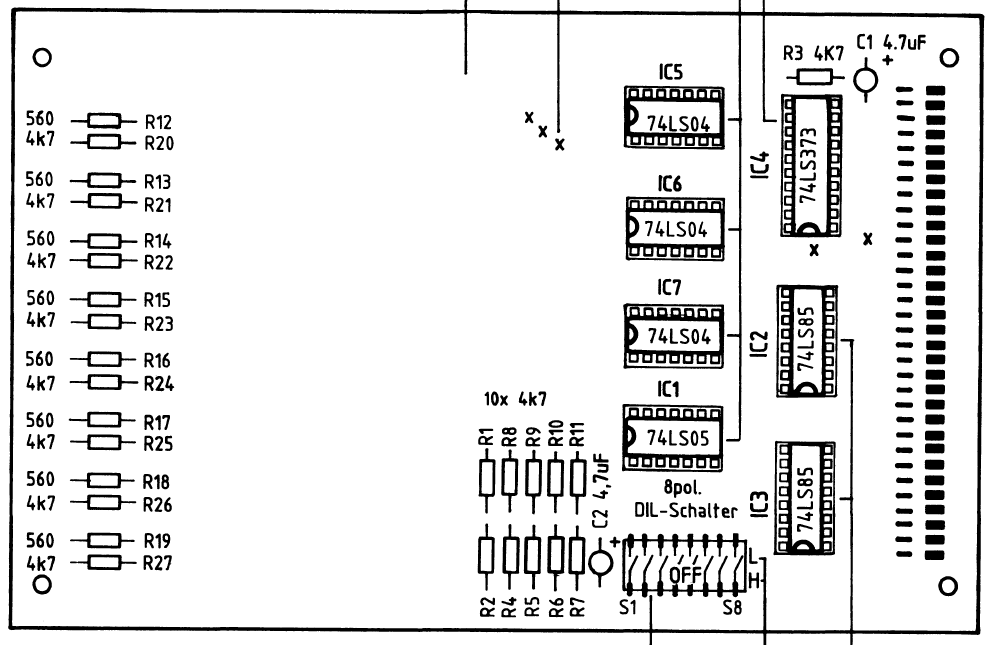

Bestückungsplan

Verdrahtungsplan