Einleitung

Viele elektronische Verarbeitungssysteme werden im Bereich der Mess-, Regelungs- oder Steuerungstechnik eingesetzt. Die Anwendung der digitalen Schaltungstechnik ist heute so weit verbreitet, daß vielfach analoge Systeme vom Markt verdrängt wurden. Digitale Signale können im Gegensatz zu analogen Signalen direkt verarbeitet oder gespeichert werden. Ein weiterer Vorteil liegt in der digitalen Signalübertragung. Die Signale werden auf dem Übertragungsweg kaum verfälscht. Deshalb wird man in der Praxis die analogen Signale so früh wie möglich digitalisieren.

Die meisten Messfühler für elektrische und nichtelektrische Größen (z.B. Temperatur, Druck, Drehzahl) liefern analoge elektrische Signale. Vor ihrer Verarbeitung in digitalen Systemen müssen diese analogen elektrischen Signale in Digitalwerte umgewandelt werden. Dies geschieht mit sogenannten Analog/Digital-Wandlern. Soll das Ergebnis einer digitalen Verarbeitung auf analoge Signalempfänger gegeben werden, so ist hier zuvor eine Digital/Analog-Wandlung auszuführen.

Beide Wandlungsarten lassen sich mit dem Einschub der hier vorgestellten Baugruppe »AD/DA-Wandler« durchführen: 1 Kanal analog-ein, 1 Kanal analog-aus. Die Baugruppe ist beliebig adressierbar und läßt sich wie eine Eingabe- oder Ausgabe-Baugruppe ansprechen. Obwohl beim Benutzen der Hardware-Wandler Kenntnisse über verschiedene Wandlungsverfahren nicht erforderlich sind, ist es hilfreich, die Prinzipien der AD- und der DA-Wandlung zu kennen.

Bei den hier eingesetzten 8-Bit-Wandlern werden sowohl für die AD- als auch für die DA-Wandlung nur jeweils ca. 20 μs benötigt. Daher läßt sich die Baugruppe sowohl für analoge Meßdaten-Erfassung als auch für regelungstechnische Vorgänge einsetzen.

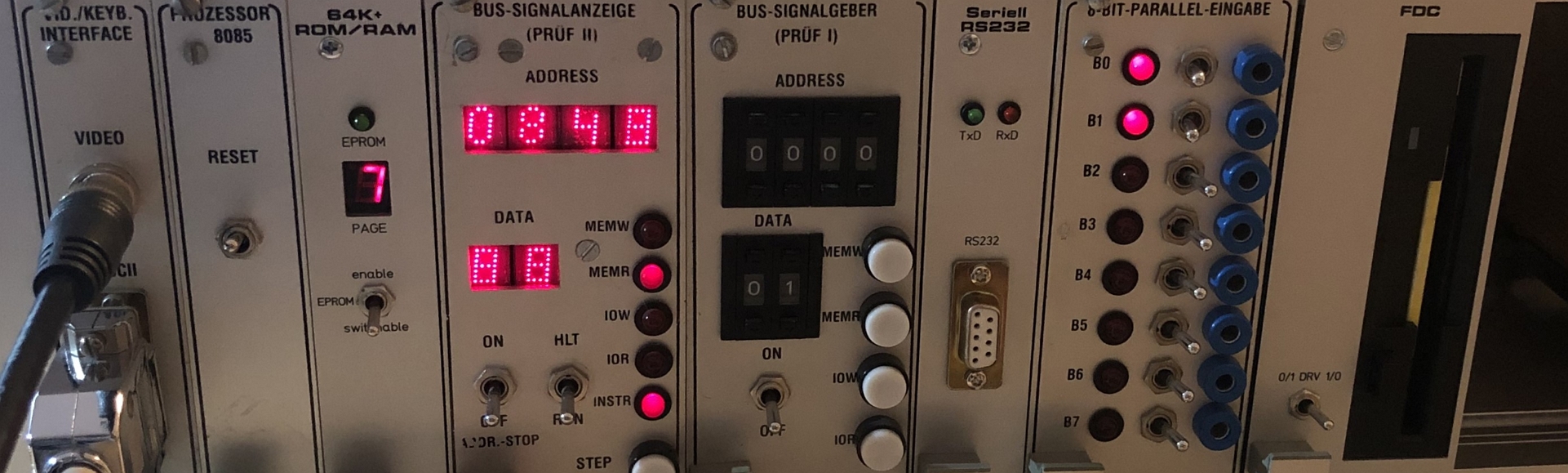

Blockschaltbild und Arbeitsweise der AD/DA-Baugruppe

Bild 99 zeigt das Blockschaltbild der AD/DA-Wandler-Baugruppe, die im wesentlichen aus den Schaltungsteilen Adreßvergleicher, AD-Wandlerbaustein und DA-Wandlerbaustein besteht. Vor der Beschreibung spezieller Einzelheiten wird zunächst die grundsätzliche Wirkungsweise der Baugruppe anhand dieses Blockschaltbildes erklärt.

Bild 99: Das Blockschaltbild der AD- und DA-Wandler-Baugruppe

Wenn der Adreßvergleicher die Gleichheit der Adresse (A0 … A7) mit der eingestellten Baugruppen-Nummer signalisiert, so ist zur Einleitung der AD-Wandlung das IOR-Steuersignal erforderlich und zur DA-Wandlung das IOW-Steuersignal. Mit Hilfe der UND-Gatter werden die beiden Aktivierungs-Signale ADF (Analog/Digital-Freigabe) und DAF (Digital/Analog-Freigabe) erzeugt.

Mit ADF wird die AD-Wandlung eingeleitet, die dafür sorgt, daß der am IN-Eingang anliegende analoge Wert als entsprechende digitale Größe am Ausgang des ADWandler-Bausteins erscheint. Von hier aus gelangt er zum System-Bus.

Das DAF-Signal gibt den DA-Wandler-Baustein frei. Damit ist am OUT-Anschluss der analoge Wert verfügbar, der als digitale Größe vom System-Bus ausgesendet wurde.

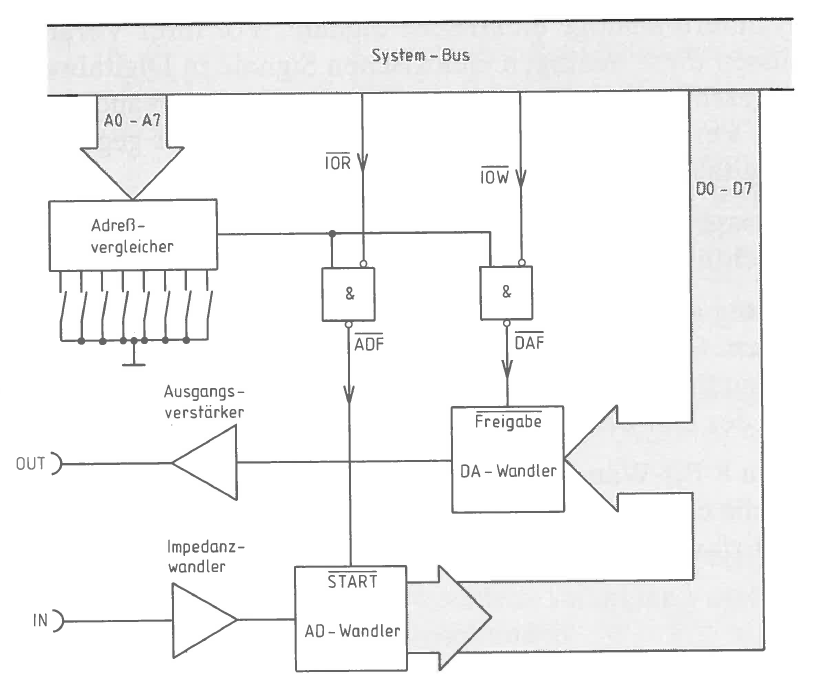

Der AD-Wandler-Baustein ZN 427

Bild 100: Das Blockschaltbild des 8-Bit-AD-Wandler-Bausteins ZN 427.

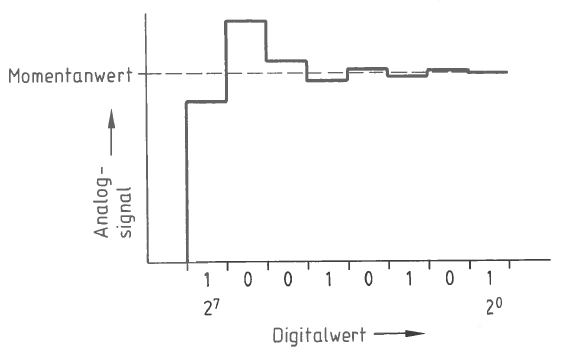

Der ZN 427 benutzt das sogenannte sukzessive Approximations-Verfahren (schrittweise Annäherung). Dieses wird auch als Iterations- oder Wägeverfahren bezeichnet und benötigt sehr kurze Konversionszeiten (Wandlungszeiten). Man beginnt mit dem Bit mit dem höchsten Stellenwert (MSB = 27). Ergibt das MSB einen Wert, der kleiner ist als das analoge Eingangssignal, so wird dieses Bit gesetzt. Danach wird die Summe aus MSB und dem Bit 26 gebildet und mit dem Eingangssignal verglichen. Ist z.B. die Summe aus MSB und Bit 26 zu groß, so entfällt 26, und es wird die Summe aus

MSB und Bit 25 gebildet. Mit dieser Methode nähert man sich immer mehr dem Eingangssignal an.

Bild 101: Das Prinzip der sukzessiven Approximation; vgl. Text.

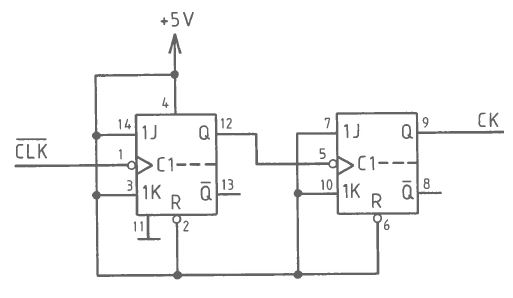

Die Erzeugung des Takt-Signals

Für die AD-Wandlung ist ein Taktsignal erforderlich. Dieses wird mit Hilfe von zwei Binärteilern im IC 74LS73 aus dem 2-MHz-Systemtakt gewonnen. Dadurch erhält man am Ausgang der Binärteiler ein 500-kHz-Signal

Bild 102: Die Erzeugung des CK-Signals mit 500 kHz aus dem 2-MHz-Systemtakt

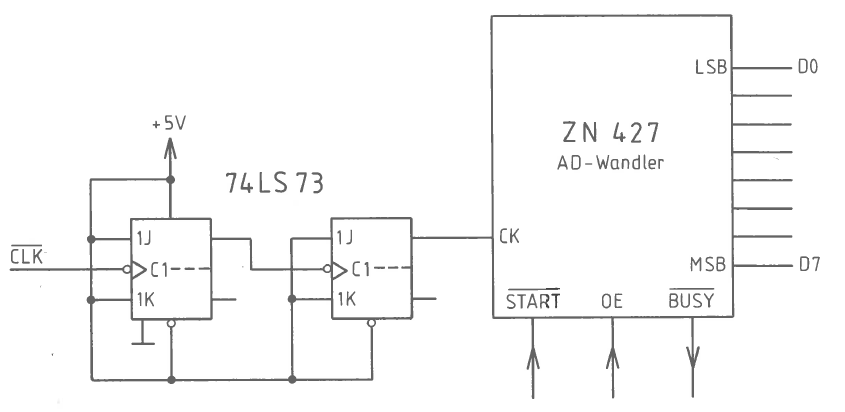

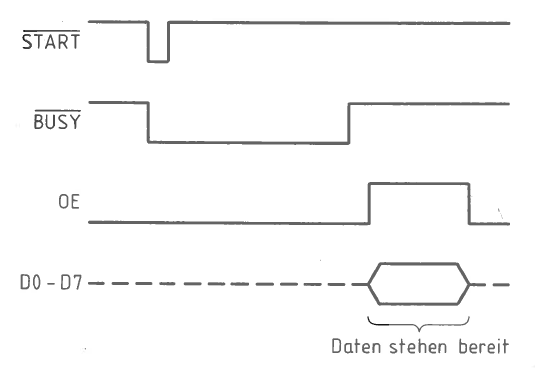

Die zeitliche Steuerung der AD-Wandlung

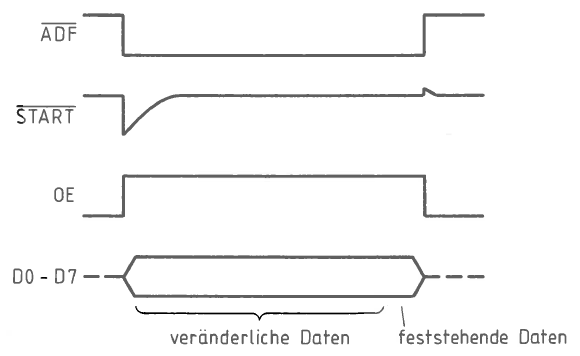

Bild 103: Die Daten- und Steuer-Signale am Baustein ZN 427.

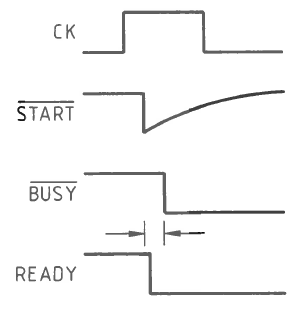

Über die Binärteiler erhält der ZN427 ständig das Taktsignal. Damit wird aber noch keine Wandlung eingeleitet. Die Wandlung beginnt erst dann, wenn der Eingang START einen Startimpuls bekommt. Während der Wandlungszeit von 18 μs Dauer liefert der Ausgang BUSY ein L-Signal und zeigt damit an, daß der ZN427 mit der Wandlung beschäftigt ist und für keinen neuen Startimpuls bereit ist; siehe Bild 104.

Der Eingang OE (Output Enable) steuert die Tristate-Ausgänge D0 … D7 des Wandlers. Mit einem L-Signal an OE werden die Datenausgänge vollkommen abgeschaltet. Das H-Signal an OE gibt die Ausgänge wieder frei, so daß ein Zugriff auf die Daten möglich ist.

Bild 104: Das Zeitdiagramm der AD-Wandlung beim ZN427.

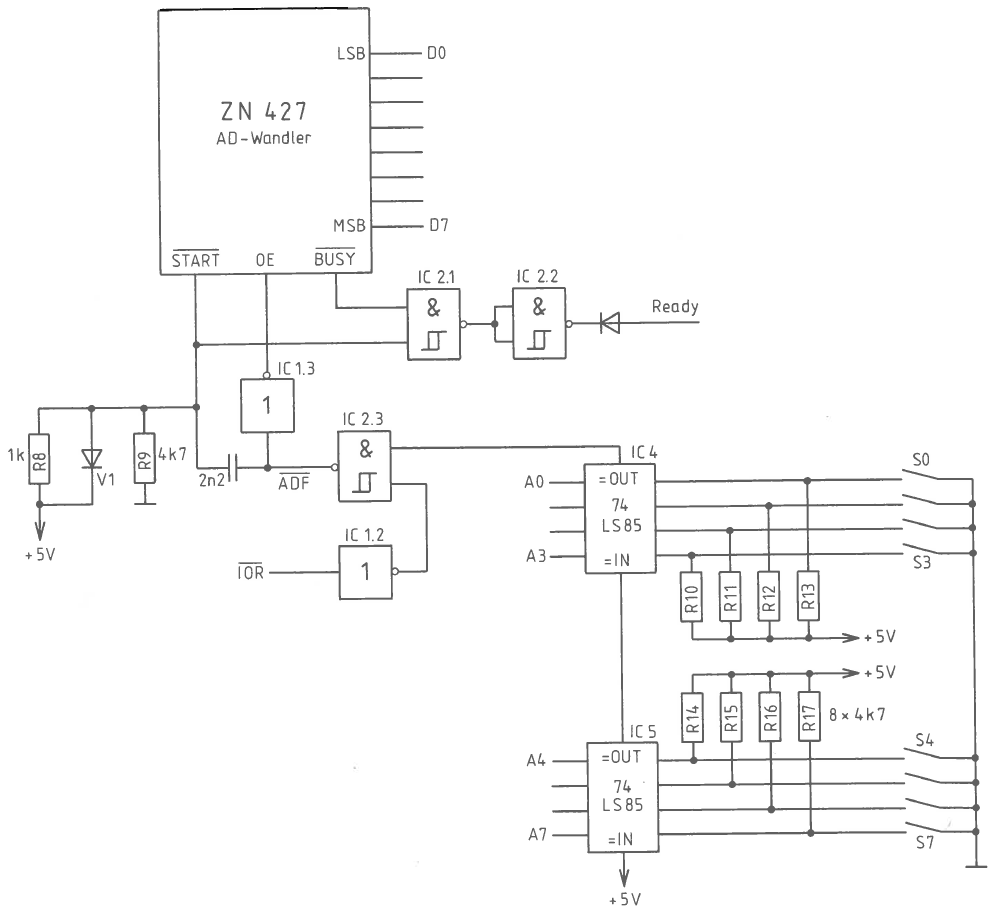

Die Erzeugung der Signale START, OE und READY

Soll eine AD-Wandlung eingeleitet werden, so müssen zunächst die Adressvergleicher IC4 und IC5 Gleichheit signalisieren. Auf die Arbeitsweise des 8-Bit-Adressvergleichers wird hier nicht eingegangen; siehe z.B. Kapitel

Bild 105: Die Erzeugung der Steuersignale.

Mit Hilfe von ICl.2 und IC2.3 wird das OUT-Signal von IC4 mit dem IOR-Signal des System-Bus verknüpft. Am Ausgang von IC2.3 erscheint jetzt das ADF-Signal (Analog/Digital-Freigabe). Der low-Pegel von ADF ist während der gesamten Wandlungszeit (ca. 18 μs) vorhanden. Zum Starten ist aber ein kurzzeitiger Impuls erforderlich. Deshalb wird das ADF-Signal mit Hilfe der Widerstände R8 und R9 sowie des Kondensators C2 differenziert. Die Diode Vl begrenzt bei der steigenden Flanke von

ADF das START-Signal auf ca. 5,7 Volt.

Der Eingang OE erhält während der gesamten Wandlungszeit einen H-Pegel (Bild 106). Innerhalb dieser Zeit liefern die Tristate-Ausgänge D0 … D7 veränderliche digitale Signale.

Bild 106: Das Zeitdiagramm von ADF, START und OE.

Erst am Ende der Wandlung, wenn das digitale Ergebnis bereitsteht, übernimmt die CPU den digitalen Wert. Während der Wandlung wird sie über den READY-Anschluss angehalten. Die CPU läßt sich über den READY-Anschluß aber nur dann anhalten, wenn zwischen der fallenden Flanke von IOR und dem L-Pegel am READY-Eingang nicht mehr als ca. 80 μs liegen. Das BUSY-Signal des Wandlers reagiert

allerdings auf den START-Impuls mit einer Verzögerung von ca. 250 μs.

Bild 107: Das Zeitdiagramm von START, BUSY und READY

Aus diesem Grunde kann der BUSY-Ausgang nicht direkt den READY-Eingang ansteuern. Das READY-Signal wird deshalb aus dem START-Impuls und dem BUSY-Signal gebildet; siehe Bilder 105 und 107. So ergibt sich nur noch eine Verzögerung von maximal 50 μs. Um das gleichzeitige Arbeiten mit Baugruppen zu ermöglichen, die ebenfalls das READY-Signal benutzen, wird in die READY-Leitung eine

Germanium-Diode gelegt. Dadurch erhält man eine ODER-Verknüpfung der einzelnen Baugruppen.

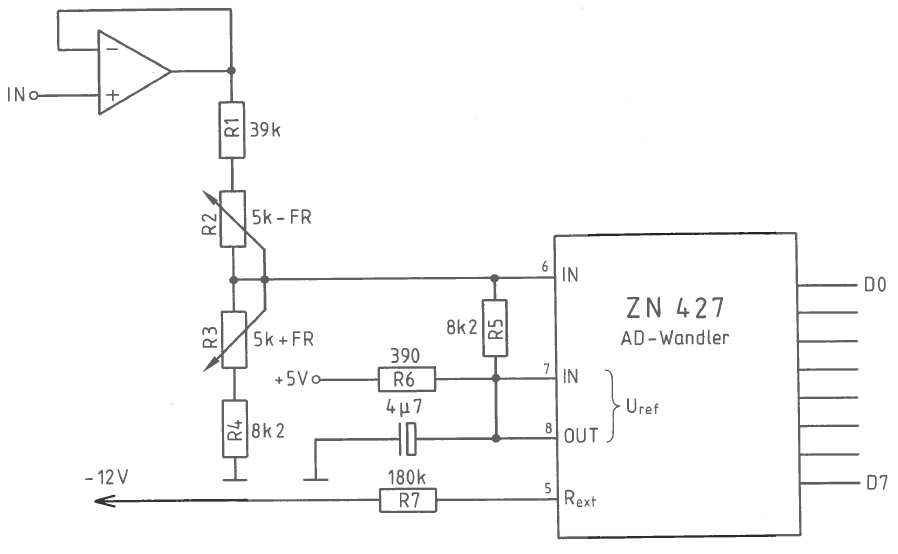

Der Analog-Eingang des ZN427

Der AD-Wandler ZN427 erhält das analoge Eingangssignal über den Eingang IN (Pin 6). Er besitzt einen zulässigen Analogbereich von 0 V bis zu dem Pegel, der am Referenzspannungs-Eingang (Pin 7) anliegt. Da in der vorliegenden Schaltung dem Referenzspannungs-Eingang die intern erzeugte Referenzspannung zugeführt wird, darf der Pegel am Anschluß 6 den Wert von 2,5 V nicht überschreiten

Bild 108: Der Eingangsspannungs-Teiler.

Wird ein bipolarer Analogbereich gewünscht, so muß am Anschluß 6 mit Hilfe von richtig dimensionierten Spannungsteilern (R1 – R5 in Bild 108) der niedrigste Analogwert am Eingang den Pegel 0 V an Pin 6 und der höchste Analogwert den Pegel von +2,5 V ergeben.

Bei der Berechnung von R1 – R5 wird hier von einem Analogbereich ausgegangen, der sich von -12,8 V bis + 12,7 V erstreckt. So erhält man am digitalen Ausgang D0 … D7 eine Zuordnung von 1 Digit pro 0,1 V. Für einen anderen Eingangsspannungsbereich müssen die Widerstände R1 – R5 geändert werden.

Bei unipolaren Operationen gilt:

R1 + R2 = Uemax / 2,5V * 4kOhm

R3 + R4 = Uemax / (Uemax – 2,5V) * 4 kOhm

Der Widerstand R5 sollte durch eine Reihenschaltung aus einem 1-MOhm-Potentiometer und einem 680-kOhm-Festwiderstand ersetzt werden. Bei bipolaren Operationen gilt:

R1 + R2 = Uemax / 2,5V * 4kOhm

R3 + R4 = Uemax / (Uemax – 2,5V) * 4 kOhm

Über den Widerstand R7 wird ein interner Differenzverstärker mit einer negativen Spannung versorgt. Steht keine Spannung von -12 V zur Verfügung, so muß R7 entsprechend der folgenden Tabelle geändert werden:

| U/V | -3 | -5 | -10 | -12 | -20 | -25 | -30 | -35 |

| R/kOhm | 47 | 82 | 150 | 180 | 220 | 330 | 390 | 470 |

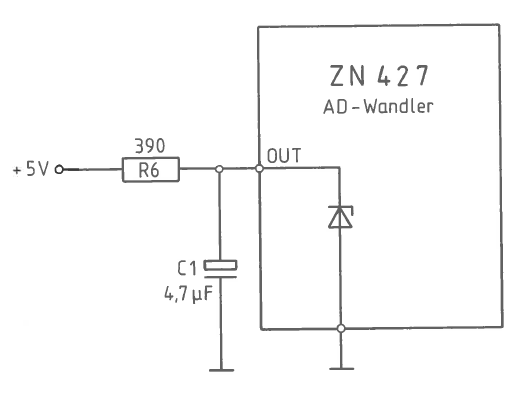

Die interne Referenzspannungs-Erzeugung

Der AD-Wandler ZN427 besitzt eine interne 2,5-V-Z-Diode. Mit Hilfe des vorgeschalteten externen Widerstandes R6 wird die 2,5-V-Referenzspannung erzeugt (Bild 109). Der Kondensator C1 sorgt für eine zusätzliche Stabilisierung der Referenzspannung.

Bild 109: Die interne Referenzspannungs-Erzeugung am ZN427.

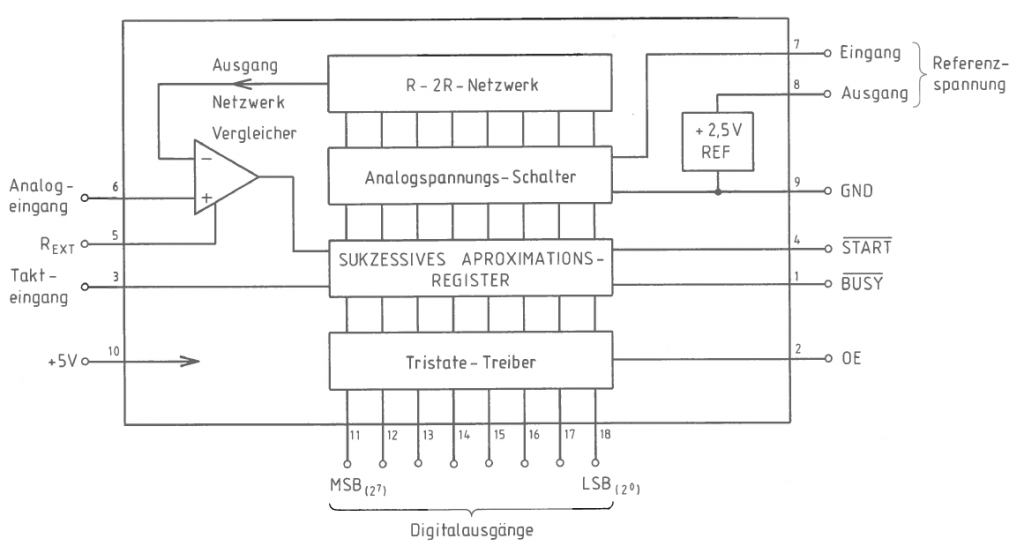

Der DA-Wandler-Baustein ZN428

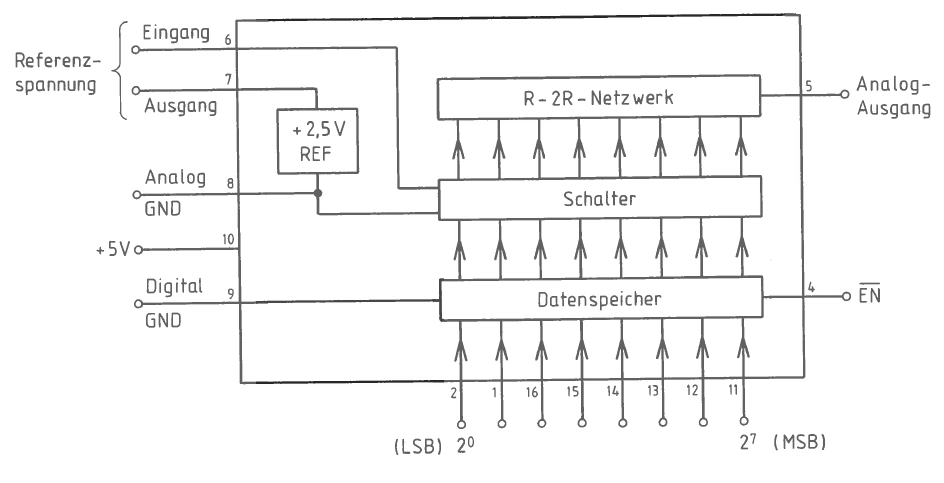

Bild 110: Das Blockschaltbild des 8-Bit-DA-Wandler-Bausteins ZN428.

Der ZN428 besitzt einen Datenspeicher für die digitale Eingangsinformation. Die Ausgänge dieses Datenspeichers werden einem R-2R-Widerstandsnetzwerk zugeführt.

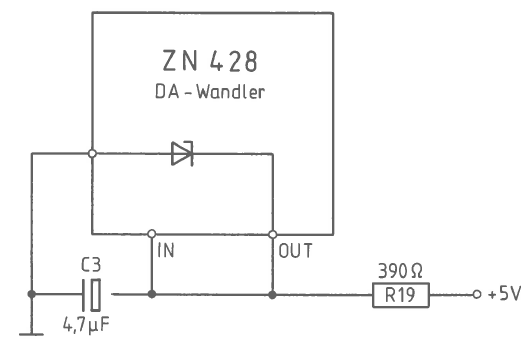

Am Ausgang des Netzwerks kann das analoge Ausgangssignal abgegriffen werden. Ähnlich wie der ZN427 besitzt auch der DA-Wandler ZN428 eine interne Referenzspannungs-Quelle. Die intern erzeugte Referenzspannung von 2,5 V wird direkt dem Referenzspannungs-Eingang zugeführt.

Bild 111: Die Versorgung des Referenzspannungs-Eingangs am ZN428.

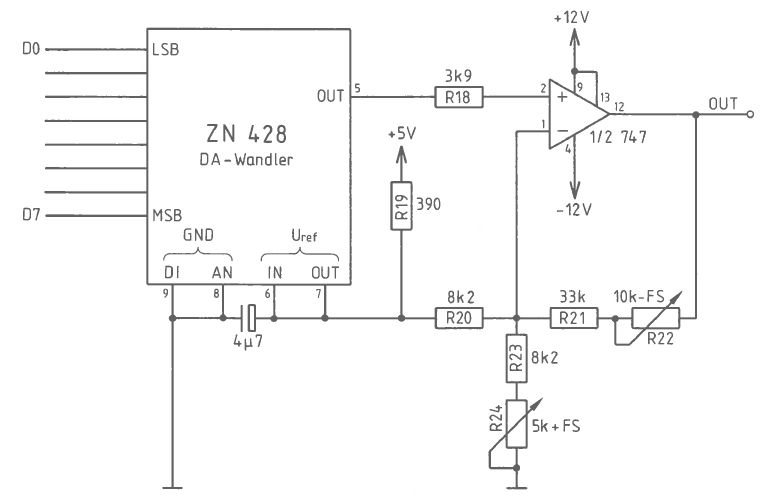

Der analoge Ausgang des ZN428

Der analoge Ausgang des DA-Wandlers (Pin 5) liefert Ausgangsspannungen von 0 V bis 2,5 V. Die nachgeschaltete Operationsverstärkerschaltung sorgt für einen Bereich von -12,8 V bis + 12,7 V. Das entspricht einer Schrittweite von 1 Digit pro 0,1 V. Aufgrund der hier verwendeten Versorgungsspannung des Mikrocomputer-Systems von ± 12 V reduziert sich der Bereich bei gleicher Schrittweite auf ± 10 V am Ausgang des Operationsverstärkers.

Bild 112: Die Erzeugung der analogen Ausgangsspannung

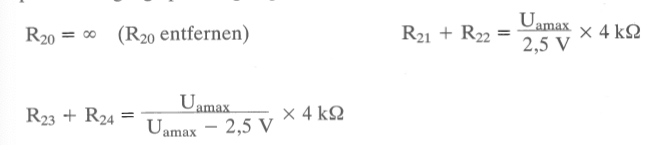

Mit Hilfe der Widerstände R20 – R24 läßt sich die analoge Ausgangsspannung den jeweiligen Erfordernissen anpassen.

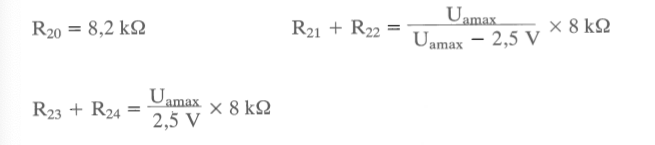

Für unipolare Ausgangsspannungen gilt:

Für bipolare Ausgangsspannungen gilt:

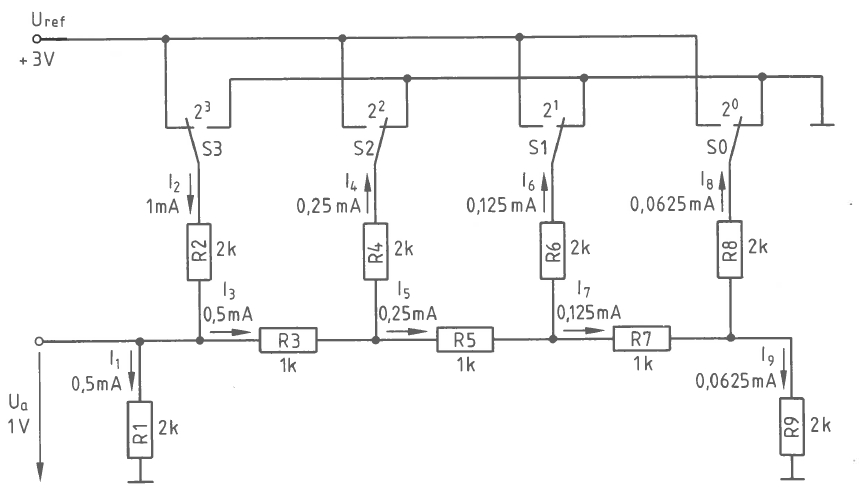

Das Prinzip des R-2R-Widerstandsnetzwerks

Bild 113: Das R-2R-Netzwerk, hier gezeigt mit dem Digitalwert 1000

Das R-2R-Netzwerk besitzt nur Widerstände mit zwei unterschiedlichen Werten, wobei ein Widerstand den doppelten Wert des anderen besitzt. Bild 113 zeigt das Prinzip eines 4-Bit-Netzwerks zur DA-Wandlung.

Dieser Wandler besteht im wesentlichen aus einer Referenzspannungs-Quelle, den Widerständen und den Umschaltern S0 – S3. In einer integrierten Schaltung werden die Umschalter aus elektronischen Elementen (z.B. Schalttransistoren) hergestellt.

Durch die Dimensionierung der Widerstände ergeben sich bei den eingezeichneten Schaltstellungen (Digitalwert = 1000) die Ströme 11 bis 19 . Der Strom 11 erzeugt am Widerstand R1 eine Spannung, die proportional zum eingestellten Digitalwert ist (0,125 V/Digit). Die Ausgangsspannung (hier 1,000 V) kann jetzt mit Hilfe eines Operationsverstärkers auf den gewünschten Wert gebracht werden.

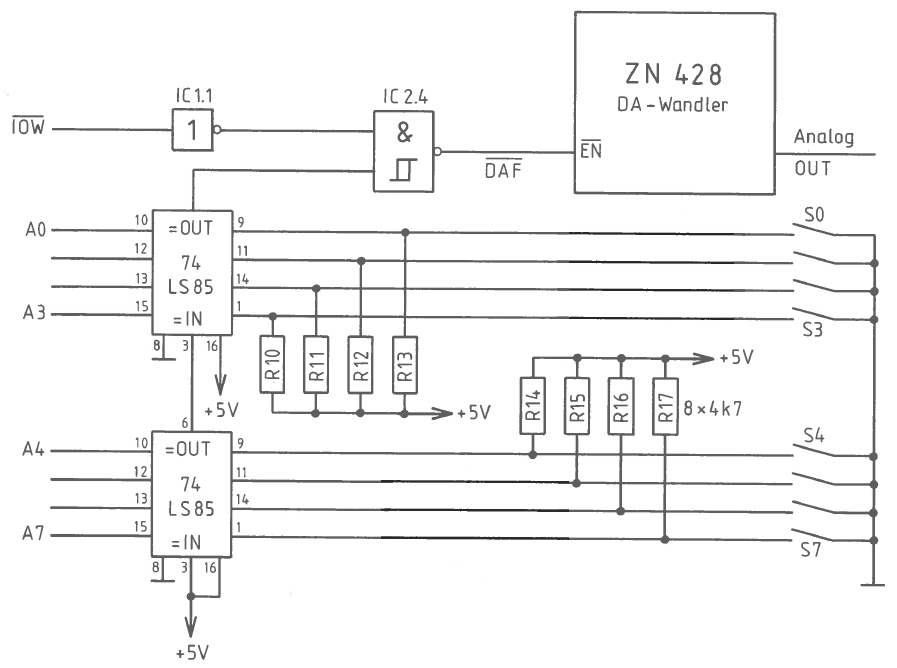

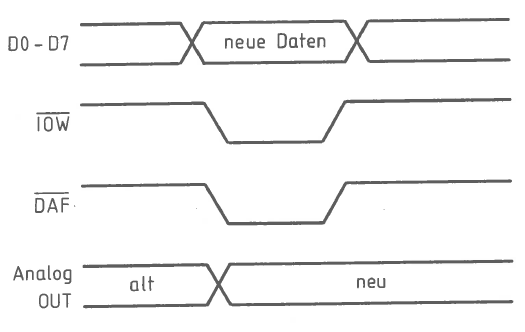

Die zeitliche Steuerung von IOW, DAF und EN

Mit Hilfe von ICl.1 und IC2.4 wird das OUT-Signal des Adressvergleichers mit dem IOW-Signal des Systems verknüpft. Am Ausgang von IC 2.4 erscheint jetzt das DAF-Signal (Digital/ Analog-Freigabe).

Bild 114: Die Erzeugung des DAF-Signals.

Das DAF-Signal wird direkt zur Steuerung des internen Datenspeichers benutzt. Erhält der Eingang EN einen L-Pegel, so wird der Digitalwert vom internen Speicher übernommen und ist damit am Ausgang (Pin 5) als Analogsignal verfügbar. Nimmt das DAF-Signal wieder H-Pegel an, so bleibt der Digitalwert gespeichert

Bild 115: Die zeitliche Steuerung der DA-Wandlung.

Die Programmbefehle zur Wandlung

Im Gegensatz zur Baugruppe 4.5 Analog/Digitalwandler, ist diese Baugruppe hier mit Hardware-Wandlern versehen. Daher genügt zur AD- wie zur DA-Wandlung jeweils ein einziger Befehl (IN bzw. OUT; dabei ist XX die Hex-Adresse der Baugruppe)

Für die AD-Wandlung:

IN XX

für die DA-Wandlung:

OUT XX

(hierzu muss das auszugebende Byte im Akku stehen).

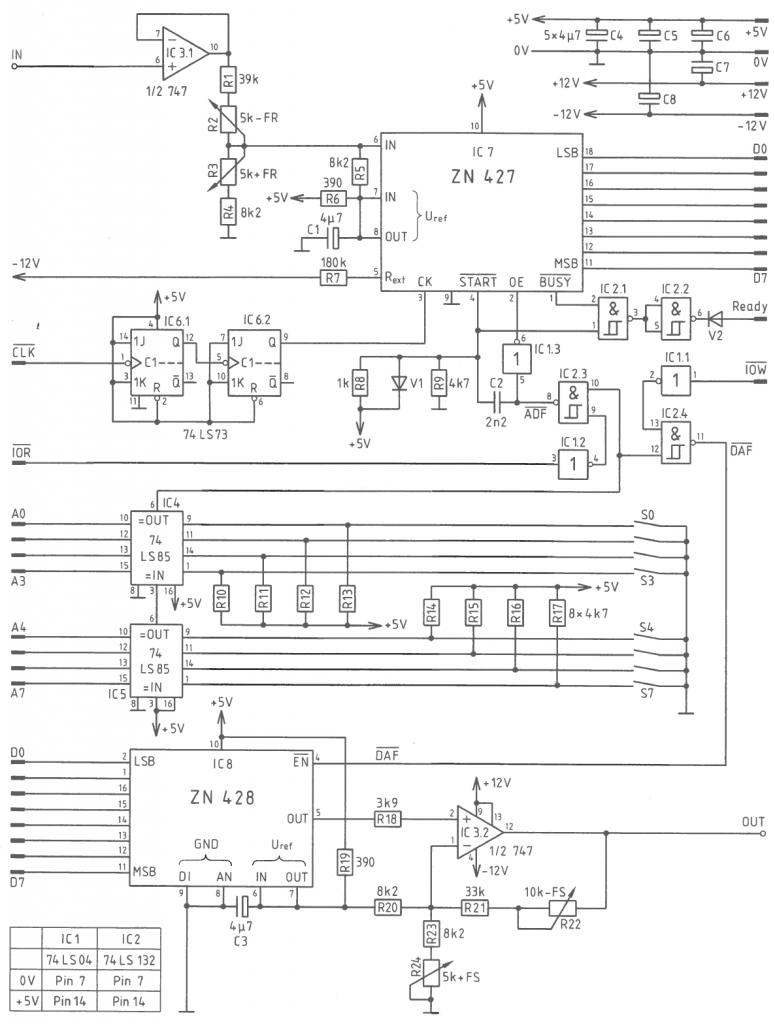

Schaltbild

Bild 116: Der Gesamt-Stromlaufplan der AD/DA-Baugruppe mit Hardware-Wandlern

Bestückungsplan

Leiterbahn

Frontblende