Einleitung

Die 64-K-RAM-Baugruppe ist für den Betrieb des im Vorwort vorgestellten MFA- Mikrocomputers unter dem Betriebssystem CP/M vorgesehen. Die Baugruppe enthält acht 8-KByte-RAM-Bausteine und ein EPROM mit wahlweise 2, 4, 8, 16 oder 32 KByte Speicherkapazität.

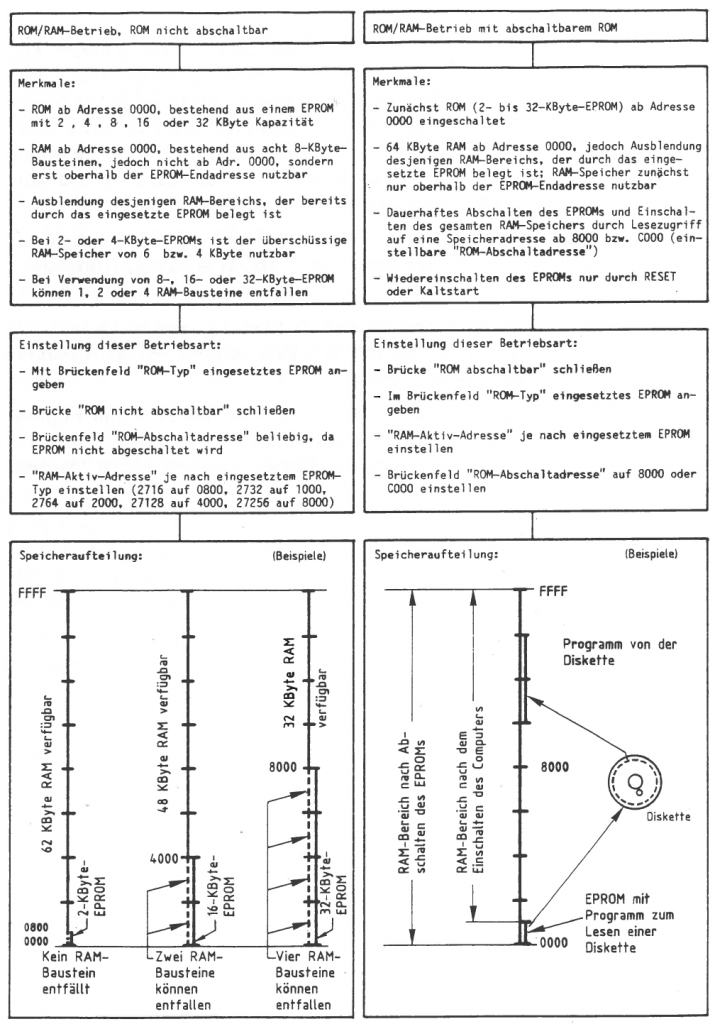

Unter CP/M wird das EPROM nach dem Laden des Betriebssystems abgeschaltet, so daß anschließend der ganze 64-K-RAM-Bereich zur Verfügung steht. Für andere Anwendungen ist es möglich, RAM und EPROM gemeinsam zu benutzen, wobei der nutzbare RAM-Bereich um die Kapazität des EPROMs verringert wird.

Nähere Einzelheiten zum CP/M-Betrieb des MFA-Mikrocomputers können hier nicht ausgeführt werden; es wird nur die 64-K-Baugruppe mit Schaltung und Anwendungsprinzip vorgestellt.

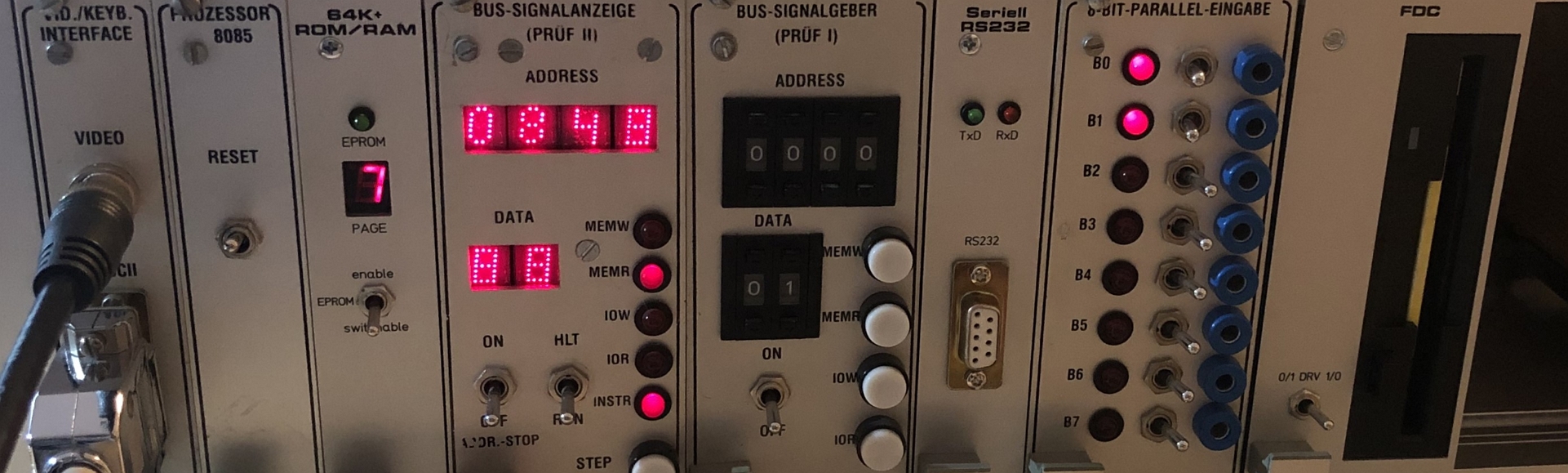

Bild 43: Die 64-K-Baugruppe.

Die 64-KByte-RAM-Baugruppe kann wahlweise im »ROM/RAM-Betrieb, ROM nicht abschaltbar« oder im »ROM/RAM-Betrieb mit abschaltbarem ROM« eingesetzt werden. Die Einrichtung der Baugruppe für die gewünschte Betriebsart erfolgt durch Lötbrücken auf mehreren Brückenfeldern.

Datenbus-Treiber, 1-aus-8-Decoder und Speicher

Der Daten-Bus der Baugruppe ist über einen Datenbus-Treiber mit dem System-Bus verbunden. Die Arbeitsrichtung des Datenbus-Treibers wird mit dem Signal MEMR gesteuert; siehe Stromlaufplan.

Mit den Adressleitungen A0 bis A12 werden die einzelnen Speicherzeilen der RAM- Bausteine und des EPROMs adressiert. Je nach verwendetem EPROM (2716 … 27256) werden die Adressleitungen A11, A13 und A14 im Brückenfeld »ROM-Typ« an die unterschiedlichen Anschlussbelegungen der EPROMs angepasst.

Die Adreßleitungen A13 bis A15 führen auf einen 1-aus-8-Decoder, der jeweils einen der 8-KByte-RAM-Bausteine über dessen CS-Anschluß freigibt.

Die OE-Anschlüsse aller RAM-Bausteine sind zusammengeführt. Daten des RAM- Speichers können nur dann gelesen werden, wenn die OE-Anschlüsse L-Pegel erhalten. Die Schreib-Lese-Umschaltung der RAM-Bausteine erfolgt über MEMW.

ROM-RAM-Umschaltung

Zur ROM-RAM-Umschaltung gehören der Adreßvergleicher mit dem Brückenfeld »RAM-Aktiv-Adresse«, die ODER-Verknüpfung »OR1«, der Inverter und die ODER-Verknüpfung »OR2«.

Beim Einschalten des Mikrocomputers (oder bei Betätigung der Reset-Taste) wird das Abschalt-Flipflop über das Signal RES zurückgesetzt, so daß der Ausgang Q an die ODER-Verknüpfung OR1 einen L-Pegel abgibt.

Der zweite Eingang von OR1 erhält nach dem Einschalten vom Ausgang P>=Q des Adressvergleichers ebenfalls L-Pegel, da die vom Prozessor ausgegebene Adresse 0000 stets kleiner als die mit dem Brückenfeld »RAM-Aktiv-Adresse« einstellbare Vergleichsadresse ist. Die ODER-Verknüpfung OR1 gibt daher zunächst L-Pegel ab. Hiermit wird der CS-Anschluss des EPROMs angesteuert und das EPROM aktiviert.

Bei aktivem EPROM muß der RAM-Speicher abgeschaltet sein. Die RAM-Abschaltung erfolgt durch H-Pegel an den OE-Anschlüssen der RAM-Bausteine. Dieser H-Pegel stammt von der ODER-Verknüpfung OR2 und wird durch Invertierung des Ausgangssignals von OR1 (CS-Signal für das EPROM) gebildet.

Durch das beschriebene Verfahren wird nach dem Einschalten bzw. Reset stets das EPROM aktiviert und der RAM-Speicher abgeschaltet.

Mit dem Brückenfeld »RAM-Aktiv-Adresse« wird eingestellt, ab welcher Speicheradresse statt des EPROMs der RAM-Speicher aktiv sein soll. Einstellbar sind die Adresswerte 0800, 1000, 2000, 4000 und 8000. Der einzustellende Wert richtet sich nach dem EPROM-Typ.

Sobald der Prozessor eine Adresse ausgibt, die gleich oder größer der eingestellten RAM-Aktiv-Adresse ist, führt der Adressvergleicher am Ausgang P >= Q einen H-Pegel und schaltet über OR1 das EPROM ab.

Zum Lesen von Daten aus dem Speicher steuert der Prozessor die MEMR-Leitung auf L-Pegel. Da das EPROM z. Zt. nicht aktiviert ist, führen jetzt beide Eingänge von OR2 L-Pegel, wodurch die OE-Anschlüsse der RAM-Bausteine L-Pegel erhalten und der RAM-Speicher zum Lesen von Daten freigegeben ist.

Zum Einschreiben von Daten in den RAM-Speicher ist L-Pegel an den OE-Anschlüssen nicht erforderlich.

Arbeitet der Prozessor wieder unterhalb der RAM-Aktiv-Adresse, nimmt der Ausgang P>=Q des Adressvergleichers wieder L-Pegel an. Hierdurch wird wieder vom RAM auf das EPROM umgeschaltet. Das Abschalt-Flipflop ist an dieser Umschaltung nicht beteiligt.

ROM-Abschaltung

Beim Einschalten des Mikrocomputers ist zunächst immer das EPROM aktiviert. Für bestimmte Anwendungsfälle der Speicherbaugruppe wie z.B. das Arbeiten unter dem Betriebssystem CP/M muß der Speicher bereits ab der Adresse 0000 mit RAM beginnen. Da CP/M nicht in EPROMs gespeichert wird, sondern auf einer Diskette, muss das EPROM ein Programm enthalten, mit dessen Hilfe CP/M von der Diskette in den RAM-Speicher geladen wird. Nach diesem als »BOOTEN« bezeichneten Ladevorgang wird das EPROM nicht mehr benötigt und muss abgeschaltet werden.

Die Abschaltung des EPROMs erfolgt durch das Abschalt-Flipflop in Verbindung mit den Brücken »ROM nicht abschaltbar/abschaltbar« und »ROM-Abschalt-Adresse«.

Bedingungen für das Abschalten des EPROMs: – Brückenfeld »ROM nicht abschaltbar/abschaltbar« in Stellung »abschaltbar«; – Speicher-Lesezugriff des Prozessors auf die mit dem Brückenfeld »ROM-Abschalt-Adresse« eingestellte oder eine höhere Adresse.

Nur wenn beide Bedingungen gemeinsam erfüllt sind, wird das Abschalt-Flipflop gesetzt und hierdurch das EPROM dauerhaft abgeschaltet. Anschließend kann auf das EPROM nicht mehr zurückgegriffen werden. Dieser Zustand bleibt bis zum nächsten Reset erhalten.

Bild 44: Die Anwendungsmöglichkeiten der 64-K-RAM-Baugruppe

Bild 45: Der Stromlaufplan der 64-K-RAM-Baugruppe

Bestückungsplan

Bild 45.2: Der Bestückungsplan der 64-K-RAM-Baugruppe