Einleitung

Die meisten elektronischen Geräte oder elektronisch gesteuerten Anlagen besitzen Schaltungsteile zur Erzeugung von Zeitverzögerungen, weil fast alle technischen Prozesse definierte und reproduzierbare Zeitwerte erfordern. Dies trifft auch in der Mikrocomputertechnik zu, in der jedoch viele der bisherigen Problemlösungen anders realisiert werden.

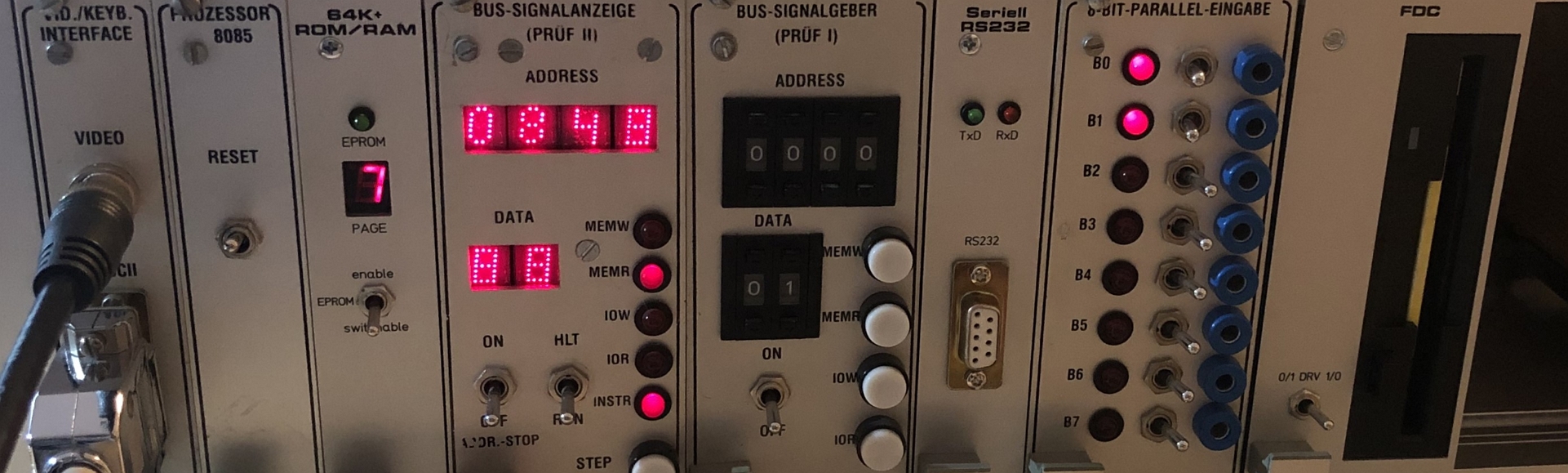

Die Übung „Zähler und Zeitgeber“ beschreibt den Aufbau und die Funktion einer Erweiterungsbaugruppe des BFZ/MFA-Computers, mit der sich vor allem Zeitverzögerungen und Impulszählungen, aber auch die Funktion von Rechteckgeneratoren und Monostabilen Kippstufen realisieren lassen. Hierbei wird eine in der Mikrocomputertechnik übliche Schaltungstechnik angewendet. Die Baugruppe „Zähl er und Zeitgeber“ kann wie jede andere Karte des BFZ/MFAComputers direkt in den 19-Zoll-Baugruppenträger eingeschoben werden und ist ohne Abgleich betriebsbereit.

Methoden der Zeitverzögerung

Zeitverzögerungen können auf unterschiedliche Arten erzeugt werden. Oft angewendet wird z.B. das Verfahren der Kondensatorladung bzw. Entladung über einen Widerstand. Die Spannung des Kondensators ändert sich dabei nach einer eFunktion, deren Spannungsverlauf in Abhängigkeit der Zeit genau berechnet werden kann. Beispiele hierfür sind Monostabile Kippstufen, die in TTL- und CMOSTechnik erhältlich sind. Weit verbreitet sind auch sogenannte „Timer-Bausteine“ wie z.B. der Typ 555, der ebenfalls nach dem Prinzip der Kondensatorladung arbeitet.

Seit der Einführung der Digitaltechnik versucht man, elektronische Schaltungen mit möglichst wenig „analogen“ Bauelementen wie Kondensatoren und Widerständen auszuführen. Hier werden Zeitverzögerungen häufig nach folgen der Methode erzielt: Ein mehrstelliger digitaler Zähler wird durch ein Taktsignal solange verändert, bis ein bestimmter Zählerstand erreicht ist. Die Anzahl der hierfür erforderlichen Takte bestimmt zusammen mit der verwendeten Taktfrequenz die sich ergebende Zeit.

Hierbei stellt man den Zähler zuerst auf einen bestimmten Wert ein und taktet ihn bis zum Zählerstand Null abwärts. In diesem Moment tritt an einem bestimmten Ausgang des Zählers ein Signal auf, das den Ablauf der gewünschten Verzögerungszeit anzeigt. Das Einstellen des Zählerstandes nennt man oft „Programmieren“. Geeignete programmierbare Zählerbausteine sind in TTL- und CMOS-Technik verfügbar.

Auch in der Mikrocomputertechnik verwendet man zur Erzielung von Zeitverzögerungen im allgemeinen das Zählverfahren. Hierbei muß allerdings zwischen einer „Software-Lösung“ mittels eines geeigneten Computer-Programms und einer „Hardware- Lösung“ mit Hilfe einer Zusatzschaltung zum Grundaufbau des Mikrocomputers unterschieden werden.

Bei der Software-Lösung wird ein beliebiges CPU-Register als Zählregister verwendet und zunächst mit einem Zähleranfangswert geladen. Anschließend erfolgt das schrittweise Verringern des Registerinhaltes um den Wert 1. Dies geschieht so oft, bis im Register der Wert Null erreicht ist. Die gesamte Steuerung dieses Vorgangs ilbernimmt ein Programm, das meistens als „Zeitschleife“ bezeichnet wird.

Die Hardware-Lösung arbeitet nach dem gleichen Prinzip. Sie verwendet jedoch keine CPU-Register, sondern zusätzlich angeschlossene äußere Zählstufen. Hierdurch wird der Prozessor von der Aufgabe des Verringerns von Registerinhalten freigehalten. Auch bei der Hardware-Lösung wird zur Ansteuerung der Zusatzschaltung ein Computerprogramm benötigt. Es ist jedoch meistens wesentlich kilrzer als eine Zeitschleife.

Bei der in dieser Übung beschriebenen Lösung wird ein spezielles Mikrocomputer- Timer-IC der Bausteinfamilie 8080/8085 verwendet. Es besitzt mehrere Betriebsarten und ist äußerst vielseitig einsetzbar. Die Schaltungstechnik dieses Timer-ICs ist vollständig an das Bus-System eines Mikrocomputers angepasst. Mit ihm können beliebige Zeitwerte zwischen wenigen Mikrosekunden und

mehreren Jahren mit Quarzstabilität erzeugt werden.

Blockschaltbild, Aufbau und Wirkungsweise der Baugruppe

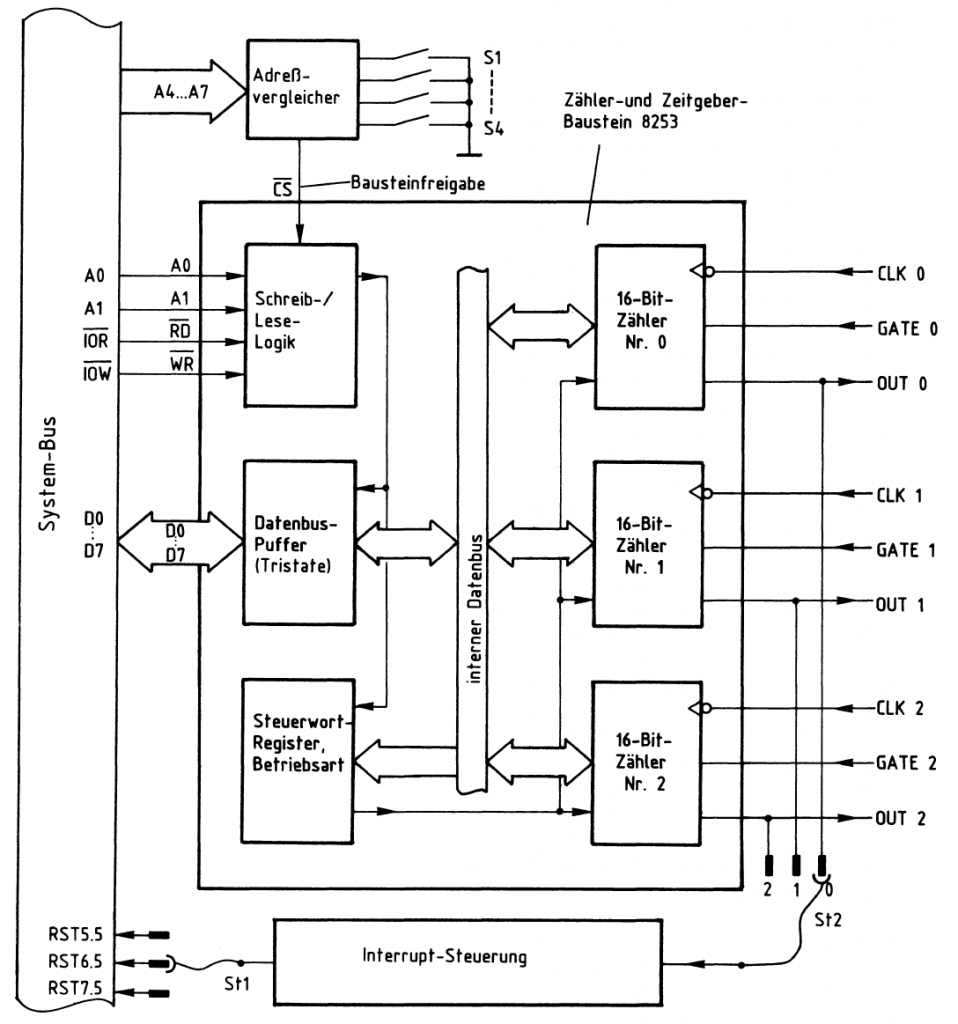

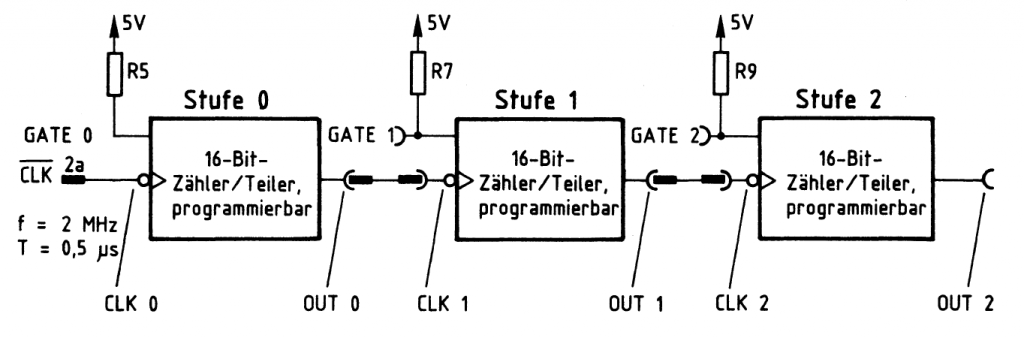

Bild 1 zeigt das Blockschaltbild der Baugruppe „Zähler und Zeitgeber“, die aus den Schaltungsteilen „Adreßvergleicher“, „Programmierbarer Zähler-und ZeitgeberBaustei n 8253“ und „Interrupt-Steuerung“ besteht. Vor der Behandlung spezieller Einzelheiten wird die grundsätzliche Wirkungsweise der Baugruppe anhand dieses Blockschaltbildes erklärt.

Der Zähl er- und Zeitgeber-Baustein 8253 enthält drei voneinander unabhängige 16-Bit-Zähler, die immer als Abwärtszähler arbeiten (Bild 1). Das Taktsignal wird jedem Zähler über seinen Takteingang „CLK“ (clock = Takt) zugeführt. Jeder Zähler besitzt nur einen Ausgang „OUT“, der in Abhängigkeit vom Zählerstand H- oder L-Pegel führt.

Bild 1: Blockschaltbild der Baugruppe Zähler und Zeitgeber

Die Zähleranfangswerte sind durch Programmierung einstellbar. Hierdurch kann die Zahl der Takte bis zum Erreichen des Zählerstandes Null und damit z.B. die Dauer einer Zeitverzögerung vom Anwender festgelegt werden. Ober die mit „GATE“ (gate = Steuereingang) bezeichneten Steuereingänge läßt sich der Zählvorgang jeder Stufe von außen beeinflussen. Die aktuellen Zählerstände lassen sich vom Prozessor jederzeit abfragen.

Jeder der drei Zähler kann in einer von sechs möglichen Betriebsarten verwendet werden. So ist es z.B. möglich, den Zähler 0 als „Monostabile Kippstufe“, den Zähler 1 als „Programmierbaren Frequenzteiler“ und den Zähler 3 als „Programmierbaren Rechteckgenerator“ zu betreiben.

Die Programmierung der jeweiligen Betriebsart erfolgt durch Einschreiben entsprechender Steuerworte in das Steuerwort-Register des Bausteins. Dies bezeichnet man als 11 Initialisierung11• Die verwendeten Steuerworte enthalten auch Informationen darUber, wie die Zählweise (BCD oder dual) oder die Art des Ladens oder Lesens des Zählerstandes geschieht.

Der Block „Schreib-/Lese-Logik“ empfängt Adress- und Steuersignale vom System-Bus und erzeugt alle fUr den Funktionsablauf erforderlichen internen Steuersignale. Hierzu muß vom „Adreßvergleicher“ Uber die Leitung „Bausteinfreigabe11 das Freigabesignal mit L-Pegel an CS anstehen. Diese Freigabe erfolgt nur dann, wenn die Baugruppe vom Prozessor „angesprochen“ wird, d.h., wenn die Bit-Kombination der Adreßleitungen A4 bis A7 gleich ist mit der Bitkombination, die mit den Schaltern S1 bis S4 eingestellt wurde (Baugruppennummer). Ober den Datenbus-Puffer werden vom Prozessor die bereits erwähnten Steuerworte und die jeweiligen Zähleranfangswerte in den Baustein geschrieben und die aktuellen Zählerinhalte aus dem Baustein gelesen. Hierbei wird der Baustein wie eine Ein-/Ausgabe-Baugruppe behandelt. Bei nicht angesprochener Baugruppe befindet sich der Datenbus-Puffer im hochohmigen Zustand (Tristate).

Mit Hilfe des Schaltungsteils „Interrupt-Steuerung“ ist es möglich, den Prozessor in seiner laufenden Arbeit zu unterbrechen, wenn ein Ereignis eintritt, auf das er sofort reagieren soll. Dies kann z.B. der Ablauf einer Zeitverzögerung beim Erreichen des Zählerstandes Null sein. Der Ausgang eines Zählers

kann für derartige Unterbrechungssteuerungen über die Steckbrücke ST2 mit dem Eingang der „Interrupt-Steuerung“ verbunden werden, deren Ausgang durch die Steckbrücke STl wahlweise auf eine der Interrupt-Leitungen RST 5.5 bis RST 7.5 geschaltet werden kann. Diese Umschaltmöglichkeiten erlauben es, jeden Zählerausgang auf jede Interruptleitung zu schalten, wobei aber immer nur eine dieser Möglichkeiten nutzbar ist.

Der Adressvergleicher und die Baugruppennummer

Der Mikroprozessor steuert die Baugruppe „Zähler und Zeitgeber“ wie jede andere Ein- und Ausgabe-Einheit an. Da immer nur eine einzige Einheit aktiviert sein darf, müssen alle im System vorhandenen Ein- und Ausgabe-Einheiten unterschiedliche Baugruppennummern besitzen. Aus diesem Grund ist die Baugruppennummer der Baugruppe „Zähler und Zeitgeber“ mit Hilfe von Schaltern einstellbar.

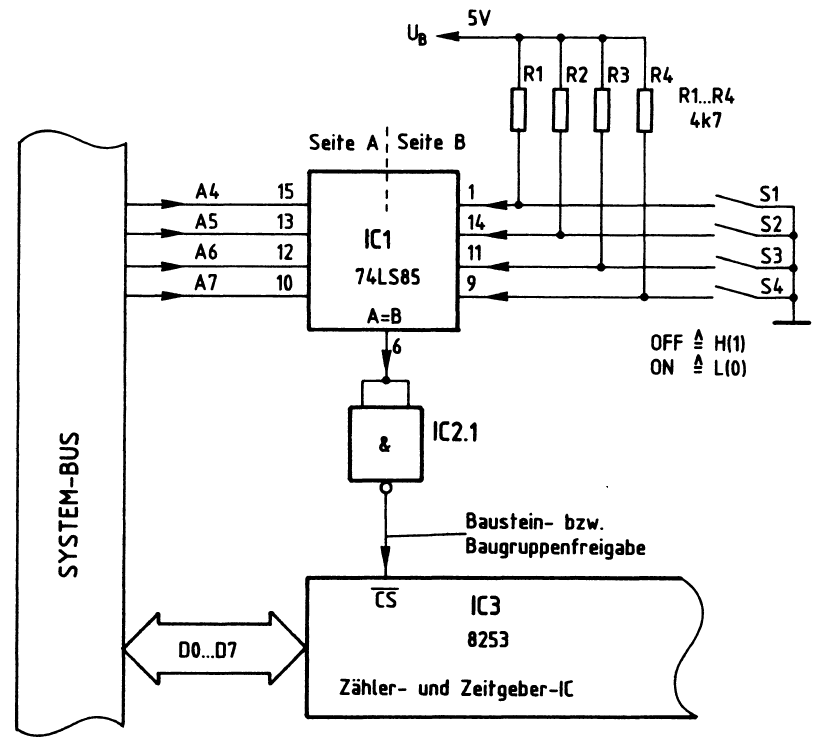

Ein Adreßvergleicher übernimmt die Aufgabe, die Baugruppe nur dann zu aktivieren, wenn der Prozessor diejenige Adresse aussendet, die der eingestellten Baugruppennummer entspricht. Bild 2 zeigt die Schaltung des Adreßvergleichers.

Bild 2: Baugruppenadresse, Bausteinfreigabe

Nur wenn die Bitkombination auf den Adreßleitungen A4 bis A7 der mit den Schaltern Sl bis S4 eingestellten Bitkombination entspricht, gibt der 4-BitVergleicher ICl an seinem Ausgang „A=B“ ein H-Signal ab (Bild 2). Da der Zähler- und Zeitgeber-Schaltkreis IC3 zur Aktivierung jedoch ein L-Signal benötigt, wird das Ausgangssignal von ICl durch IC2.1 invertiert. Die Baugruppe kann nun Daten empfangen oder an den Prozessor abgeben.

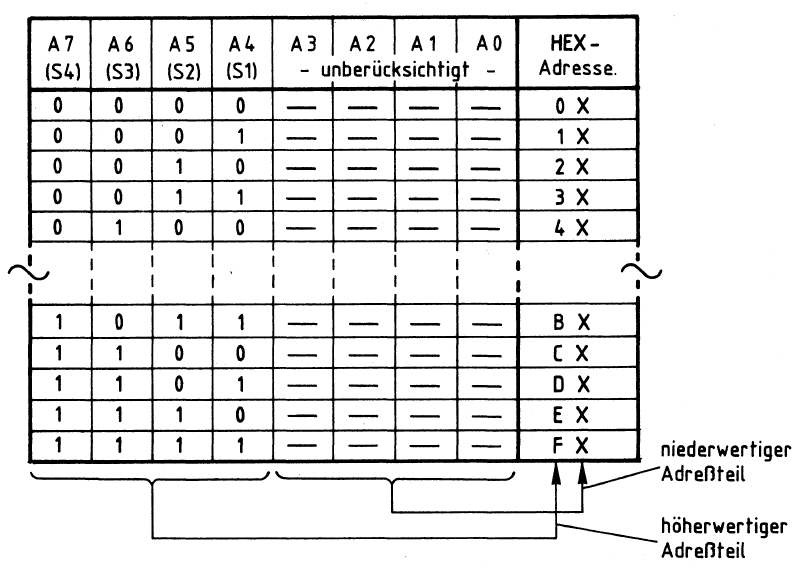

Der Prozessor gibt stets eine vollständige 8-Bit-Adresse an A0 bis A7 aus, wenn er eine Ein- oder Ausgabe-Einheit anspricht. Beim hier vorgenommenen Adressvergleich werden jedoch die Adressleitungen A0 bis A3 nicht berücksichtigt. Aus diesem Grund steht nicht der volle Adressbereich von 00H bis FFH mit 256 verschiedenen Adresswerten nur Verfügung, sondern mit den Schaltern S1 bis S4 können lediglich 16 verschiedene Signalzustände (Bausteinadressen) eingestellt werden. Da diese Schalter den vier höherwertigen Adress-Bits A4 bis A7 zugeordnet sind, kann die Baugruppennummer nur die hexadezimalen Werte von 0X bis FX annehmen. „X“ steht hier für die vier niederwertigen Adress-Bits AO bis A3, die beim Adressvergleich nicht benutzt werden. Die Tabelle in Bild 3 zeigt die Bildung der möglichen Baugruppennummern.

Bild 3: Bildung der Baugruppennummern der Baugruppe „Zähler und Zeitgeber“

Im fachpraktischen Teil dieser Obung werden die Schalter bei der Inbetriebnahme

der Baugruppe folgendermaßen eingestellt:

| S4 (A7) | S3 A(6) | S2 (A5) | S1 (A4) |

|---|---|---|---|

| OFF | ON | OFF | OFF |

| 1 | 0 | 1 | 1 |

Hierdurch ergibt sich die Baugruppennummer „BXH“. Prinzipiell kann jede der 16 möglichen Baugruppennummern verwendet werden. Es ist aber darauf zu achten, dass sämtliche Ein- oder Ausgabe-Baugruppen eines Mikrocomputer-Systems unterschiedliche Adressen besitzen, da es anderenfalls zu Schäden am Gerät kommen kann.

Die Adressierung der drei Zähl er und des Steuerwort-Registers

Beim Laden von Zähleranfangswerten, beim Lesen von aktuellen Zählerständen und beim Einschreiben von Steuerworten muß dem Zähler- und Zeitgeberbaustein über die Adressanschlüsse A0 und A1 mitgeteilt werden, welcher der vier internen Blöcke (drei Zähl er und Steuerwort-Register) am gewünschten Datenverkehr beteiligt sein soll. Bild 4 zeigt die Adressierung der Blöcke durch die Adressleitungen A0 und A1

| A1 | A0 | Zähler/Register |

|---|---|---|

| 0 | 0 | Zähler 0 |

| 0 | 1 | Zähler 1 |

| 1 | 0 | Zähler 2 |

| 1 | 1 | Steuerwort-Register |

Bild 4: Zähler- und Steuerwort-Register- Adressierung

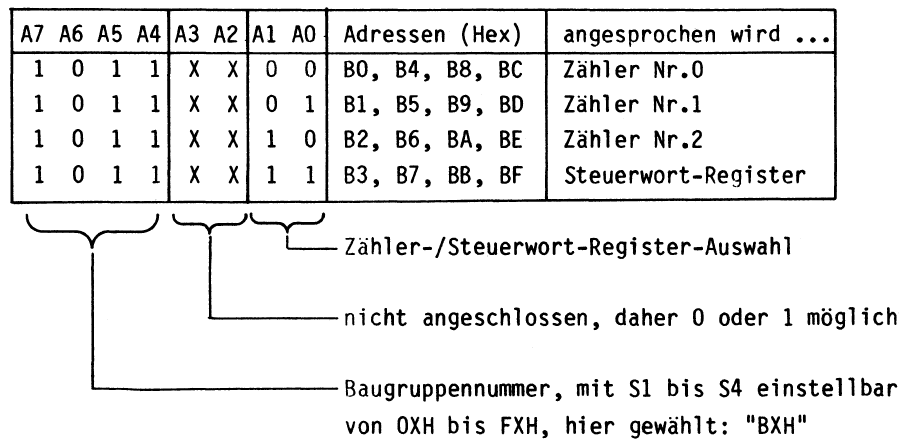

Da die Bausteinanschlüsse A0 und A1 mit den Adressleitungen A0 und A1 des System-Busses verbunden sind und die Adressleitungen A4 bis A7 zur Bausteinfreigabe verwendet werden, ergibt sich die vollständige Adressbildung unter Verwendung der Adressleitungen A0 bis A7 wie in Bild 5 dargestellt:

Bild 5: Adreßbildung mit allen Adreßleitungen von A0 bis A7

Die Bitkombination an A4 bis A7 (Bild 5) stellt jeweils den Wert „BXH“ dar und entspricht der mit S1 bis S4 eingestellten Baugruppennummer. Die Bitkombination an A0 und Al bestimmt, ob Zähler 0, 1 oder 2 oder das Steuerwort-Register des Zähler- und Zeitgeber-ICs angewählt wird.

Die Adreßleitungen A2 und A3 sind nicht angeschlossen, daher kann ihr Signalzustand „1“ oder „O“ sein. Hieraus ergeben sich vier mögliche Adressen für jeden Zähler und das Steuerwort-Register. Das Zählregister Nr. 0 kann beispielsweise unter den Adressen B0H, 84H, 88H und BCH angesprochen werden und das Steuerwortregister unter den Adressen 83H, 87H, BBH und BFH. Diese Mehrfachadressierung ist durch die einfache Schaltung bedingt.

Alle Adressen beginnen aber stets mit dem gleichen, durch S1 bis S4 gebildeten Hex-Zahlenwert (in diesem Fall mit „B““}. Um Verwirrungen zu vermeiden, sollten die Zähl er und das Steuerwort-Register fortlaufend z.B. unter den Adressen B0H, B1H, B2H und B3H angesprochen werden. Aus diesen Zahlenwerten ist sofort erkennbar, welcher der vier Blöcke angesprochen wird. Es wäre aber ebenso möglich, sie unter den Adressen 88H, 85H, BEH und 87H zu adressieren.

Der Aufbau der Zähler

Der Prozessor kann jeden Zähler mit frei wählbaren Zähleranfangswerten laden. Weiterhin besteht die Möglichkeit, den aktuellen Zählerstand jedes Zählers zu lesen. Da die Zähler 16 Bit umfassen, der Datenbus des verwendeten Prozessors jedoch nur 8 Bit besitzt, muss das Laden und Lesen der Zählerwerte in mehreren Schritten erfolgen. Zur Erklärung dieser Vorgänge zeigt Bild 6 den inneren Aufbau eines Zählers.

Bild 6: Aufbau eines Zählers

Das Laden des Zähleranfangswertes

Der Prozessor sendet den gewünschten Zähleranfangswert über 00 bis 07 des Systembusses und den Datenbus-Puffer zunächst in das 16-Bit-Zwischenregister (Bild 6). Hierbei gibt es auf Grund der vorhergegangenen Initialisierung des Bausteins drei unterschiedliche Möglichkeiten:

- Es ist festgelegt worden, dass der empfangene Wert als niederwertiges Byte (NW-Byte) des Zähleranfangswertes in das 16-Bit-Zwischenregister gelangt.

- Es wurde bestimmt, dass der empfangene Wert als höherwertiges Byte (HW-Byte) des 16-Bit-Zähleranfangswertes in das 16-Bit-Zwischenregister kommt. In beiden Fällen erhält der nicht angesprochene Teil des 16-Bit-Zählers automatisch den Wert 00 zugewiesen.

- Voll ständiges Laden des 16-Bit-Zähl ers in zwei Schritten: Zuerst das niederwertige Byte und anschließend das höherwertige Byte.

Das eigentliche Zählregister wird stets erst beim Start der Zählfunktion mit dem Wert des Zwischenregisters geladen.

Das Lesen des aktuellen Zählerstandes

Das dritte als „Zwischenspeicher“ bezeichnete 16-Bit-Register (Bild 6} ermöglicht es, den aktuellen Zählerstand verfälschungssicher zu lesen. Hierzu kann der momentane Wert des Zählers durch ein bestimmtes Programmierwort in den Zwischenspeicher übergeben und anschließend über den Datenbus ausgelesen werden. Dies geschieht (wie beim Laden des Zähleranfangswertes) in einem oder in zwei Schritten.

Für die drei Zählstufen des Zähler- und Zeitgeber-Bausteins steht im Gegensatz zur Darstellung von Bild 6 allerdings nur ein gemeinsamer Zwischenspeicher zur Verfügung, der jedoch durch das Steuerwort jedem der drei Zähler (auch nacheinander wechselnd} zugewiesen werden kann.

Grundsätzlich ist es auch möglich, den aktuellen Zählerstand direkt zu lesen, ohne ihn vorher zwischenzuspeichern. In diesem Fall muss aber die Zählfunktion während des Auslesens z.B. durch L-Signal am GATE-Eingang oder durch Unterdrücken der Taktimpulse unterbrochen werden, damit sich der Zählerstand beim Lesen nicht verändern kann.

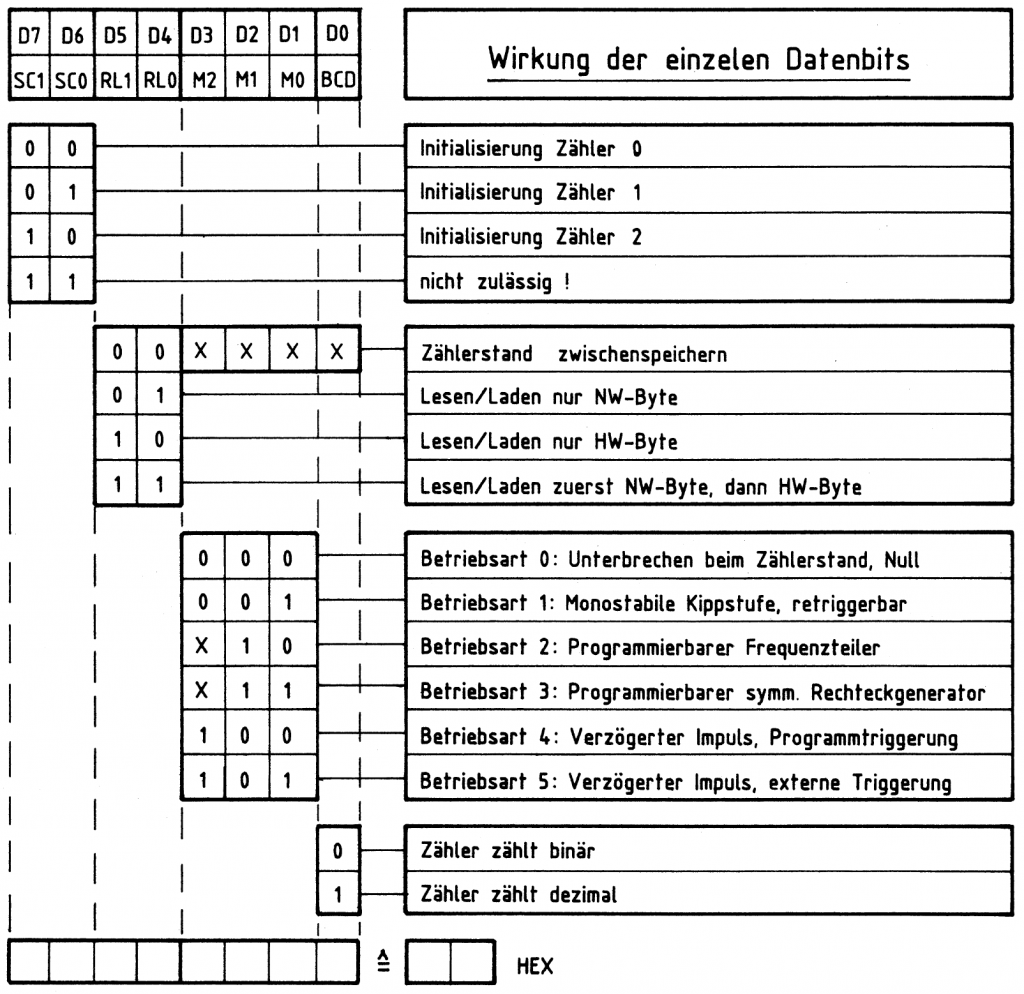

Initialisierung der Zähler

Die drei Zähler des Zähler- und Zeitgeber-Bausteins müssen durch Einschreiben geeigneter Steuerworte in das Steuerwort-Register initialisiert, d.h. in ihrer Arbeitsweise programmiert werden. Hierzu sind folgende Schritte erforderlich:

- Der Akkumulator des Prozessors muß mit dem Wert des erforderlichen Steuerwortes, das häufig auch als „Statuswort“ bezeichnet wird, geladen werden. Hierzu eignet sich der Befehl „MVI A,konst“ des Prozessors 8085.

- Das sich nun im Akku befindliche Statuswort wird an das Steuerwort-Register ausgegeben. Hierzu ist der Befehl „OUT adr“ des Prozessors 8085 notwendig. Die Adresse für das Steuerwort-Register ist B3H, da in dieser Übung von der Baugruppennummer „BXH“ ausgegangen wird.

Vergleichen Sie Bild 5!

Bei der Initialisierung ist zu beachten, daß nach dem Anlegen der Betriebsspannung kein definierter Grundzustand des Steuerwort-Registers vorliegt. Daher muß die Initialisierung des Bausteins bei jedem Kaltstart des Mikrocomputers neu erfolgen.

Da der Baustein keinen RESET-Anschluß besitzt, bleibt eine einmal vorgenommene Initialisierung auch bei Betätigung der RESET-Taste des Prozessors erhalten. Die Zähler können aber jederzeit durch Einschreiben neuer Steuerworte auf andere Betriebsarten uninitialisiert werden.

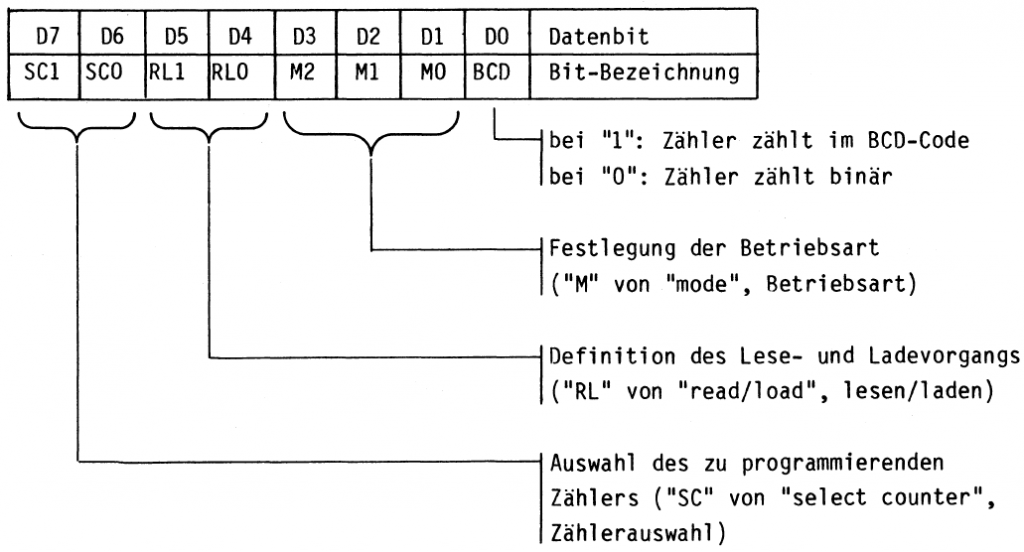

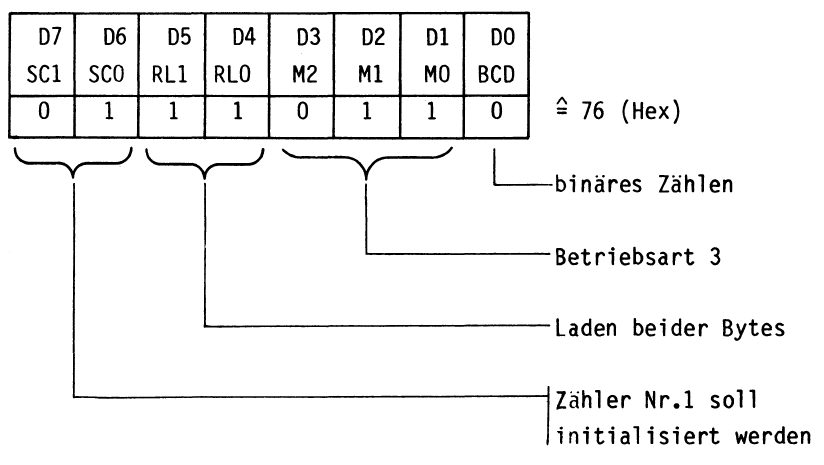

m Gegensatz zu den Zählerständen kann das Steuerwort-Register nicht vom Prozessor gelesen werden. Wenn die programmierte Betriebsart gelesen oder kontrolliert werden soll, muss eine Kopie der Initialisierung im RAM-Speicher des Mikrocomputers abgelegt werden. Jedes Steuerwort zur Initialisierung besitzt acht Bit (DO bis D7) mit folgenden Funktionen:

- Festlegung, ob im BCD-Code oder binär gezählt werden soll (Bit 00)

- Festlegung einer von sechs Betriebsarten (Bits D1, 02 und 03)

- Definition des Lese- und Ladevorgangs (Bits 04 und D5)

- Auswahl der zu programmierenden Zählstufe (Bits 06 und 07)

Bild 7 stellt den Aufbau des Steuerwortes dar. Die Bezeichnungen der einzelnen Bits sind dem Datenbuch entnommen und geben Hinweise auf deren Bedeutung. Anschließend werden die Einzelheiten des Steuerwortes erklärt, ohne jedoch auf jede Kombinationsmöglichkeit einzugehen. Hierzu geben die Datenbücher der Bauelementehersteller weiteren Aufschluss.

Bild 7: Aufbau des Steuerwortes

SCO und SCl: Auswahl des zu programmierenden Zählers

Alle drei Zähler müssen einzeln initialisiert werden. Daher enthält jedes Steuerwort die Information darüber, für welchen Zähler es bestimmt ist. Die Auswahl des zu programmierenden Zählers geschieht nach Bild 8 mit den Datenbits D6 (SCO) und D7 (SCl) des Steuerwortes.

| SC1 | SC0 | Steuerwort |

|---|---|---|

| 0 | 0 | Zähler 0 |

| 0 | 1 | Zähler 1 |

| 1 | 0 | Zähler 2 |

| 1 | 1 | nicht zulässig |

Bild 8: Wirkung der Steuerwort-Bits SCO und SCl

Weil nur drei Zähler vorhanden sind, ist die Bitkombination, bei der SC0 und SC1 1-Signal haben, nicht zulässig.

RL0 und RL1: Definition des Lese- und Ladevorgangs

Die Definition des Lese- und Ladevorgangs der Zähler erfolgt mit den Datenbits D4 (RLO} und D5 (RLl) des Steuerwortes. Bild 9 zeigt die Wirkung dieser Bits.

| Bitkombination | RL1 | RL0 | Wirkung auf das Lesen und Laden des durch SCO und SCl ausgewählten Zählers |

|---|---|---|---|

| 1 | 0 | 0 | Zählerstand zum Lesen eines Zählers zwischenspeichern |

| 2 | 0 | 1 | Lesen/Laden nur des niederwertigen Bytes eines 16-Bit-Zählers |

| 3 | 1 | 0 | Lesen/Laden nur des höherwertigen Bytes eines 16-Bit-Zählers |

| 4 | 1 | 4 | Lesen/Laden beider, zuerst des niederwertigen, danach des höherwertigen Bytes eines 16-Bit-Zählers |

Bild 9: Wirkung der Steuerwort-Bits RL0 und RL1

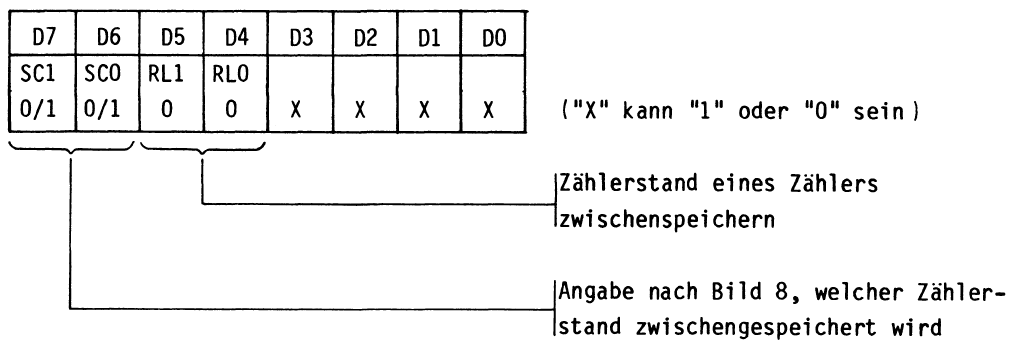

zur Bitkombination 1:

Diese Kombination von RLO und RU nimmt eine besondere Stellung ein, weil durch sie der aktuelle Zählerstand eines Zählers unabhängig von der programmierten Betriebsart in den 16-Bit-Zwi sehen spei eher (Bild 6} eingeschrieben wird. Hierbei legen die Datenbits D6 (SCO} und D7 (SCl) fest, welcher Zählerstand gespeichert wird. Nach dem Speichern kann der Prozessor den Zählerstand verfälschungssicher lesen, was ohne vorherige Zwischenspeicherung nicht gewährleistet ist. Das Steuerwort zum Zwischenspeichern eines Zählerstandes hat das in Bild 10 gezeigte Format.

Bild 10: Steuerwort zum Zwischenspeichern eines aktuellen Zählerstandes

In Verbindung mit den Informationen aus Bild 8 ergeben sich aus Bild 10 je nach gewähltem Zähler drei verschiedene Statusworte bzw. Programmteile zum Programmieren der Funktion „Zählerstand zum Lesen eines Zählers zwischenspeichern“:

Zähler 0:

MVI A,00

OUT B3H

Zähler 1:

MVI A,40H

OUT B3H

Zähler 2:

MVI A,80H

OUT B3H

In allen drei Fällen wird das Steuerwort-Register angesprochen. Dies geht aus der Hex-Adresse „83“ hervor. Zu beachten ist, dass immer nur ein Zähl erstand zwischengespeichert werden kann, da nur ein Zwischenspeicher vorhanden ist.

zur Bitkombination 2:

Diese Bitkombination von RL0 und RL1 legt fest, dass beim Lesen oder Laden des durch SC0 und SC1 bestimmten Zählers (Bild 8) nur das niederwertige Byte benutzt wird. Das höherwertige Byte dagegen erhält automatisch den Wert 00 zugewiesen. Somit arbeitet bei dieser Lade- und Lese-Definition der ausgewählte 16-Bit-Zähler nur als 8-Bit-Zähler, da die höchsten acht Bit zu Null gesetzt sind. Dies ist in Bild 11 dargestellt.

Bild 11: Lesen/Laden des niederwertigen Bytes

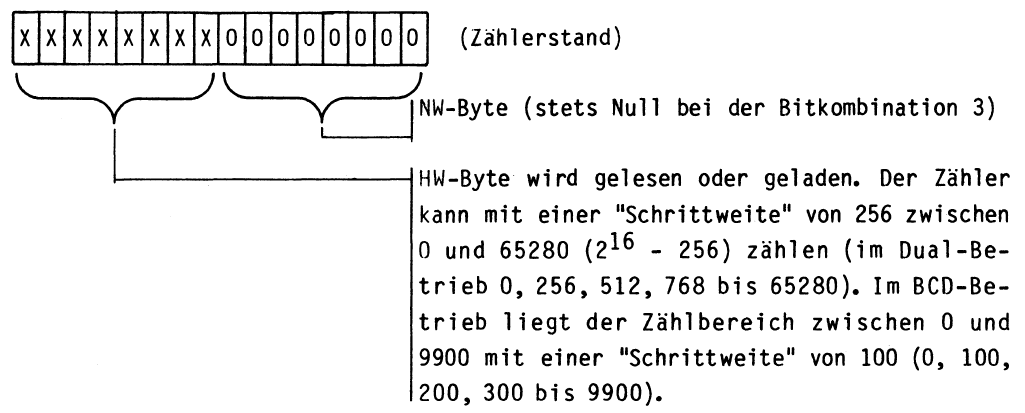

zur Bitkombination 3:

Diese Bitkombination von RL0 und RL1 legt fest, dass beim Lesen oder Laden des durch SC0 und SC1 bestimmten Zählers (Bild 8) nur das höherwertige Byte benutzt wird. Das niederwertige Byte erhält automatisch den Wert 00 zugewiesen. Bei dieser Lese- und Lade-Definition arbeitet der ausgewählte 16-Bit-Zähler zwar als 16-Bit-Zähler. jedoch sind die unteren acht Bits stets zu Null gesetzt. Dies ist in Bild 12 dargestellt.

Bild 12: Lesen/Laden des höherwertigen Bytes

zur Bitkombination 4:

Bei dieser Bitkombination von RL0 und RL1 wird der durch SC0 und SC1 ausgewählte Zähler in zwei unmittelbar aufeinanderfolgenden Schritten geladen oder gelesen. Dabei wird stets zuerst das niederwertige und dann das höherwertige Byte benutzt. Diese Lade- und Leseart wird am häufigsten verwendet.

M0, M1 und M2: Festlegung der Betriebsarten

Mit dem Zähler- und Zeitgeber-Baustein 8253 sind sechs verschiedene Betriebsarten möglich, die nach Bild 13 mit den Bits D1 (MO), 02 (Ml) und 03 (M2) des Steuerwortes festgelegt werden. Die Erklärung dieser Betriebsarten erfolgt im Kapitel 5.

| M2 | M1 | M0 | Nummer und Bezeichnung der Betriebsart |

|---|---|---|---|

| 0 | 0 | 0 | 0 Unterbrechen beim Zählerstand Null |

| 0 | 0 | 1 | 1 Monostabile Kippstufe, retriggerbar |

| X | 1 | 0 | 2 Programmierbarer Frequenzteiler |

| X | 1 | 1 | 3 Programmierbarer symmetrischer Rechteckgenerator |

| 1 | 0 | 0 | 4 Verzögerter Impuls, Programmtriggerung |

| 1 | 0 | 1 | 5 Verzögerter Impuls, externe Triggerung |

Bild 13: Festlegung der Betriebsarten

BCD: Bestimmung der Zählweise BCD/binär

Das mit „BCD“ bezeichnete Datenbit DO des Steuerwortes bestimmt, ob der von den Bits SC0 und SC1 ausgewählte Zähler binär oder dezimal (im BCD-Code} zählen soll.

Bei 0-Signal des BCD-Bits im Steuerwort wird binär gezählt. Weil jeder Zähler 16 Binärstellen besitzt, kann maximal von 65535 bis auf Null heruntergezählt werden.

Hat D0 beim Initialisieren den Wert 11111 , wird die dezimale Zählweise programmiert. Das Zählen im BCD-Code erfordert pro Dezimalstelle 4 Bit, so dass von den insgesamt 16 Bit vier Dezimalstellen gebildet werden, deren Zählbereich von maximal 9999 bis Null reicht.

Weitere Hinweise zur Initialisierung

Dieses Kapitel behandelt einige häufig aufgeworfene Fragen und Probleme zur Programmierung des Zähler- und Zeitgeber-Bausteins 8253.

In welcher Reihenfolge sind die Zähler zu initialisieren?

Dies ist beliebig. Es kann ohne weiteres zuerst Zähler Nr. 1, danach Nr. 0 und zum Schluss Nr. 2 initialisiert werden.

Müssen auch nicht benötigte Zähler initialisiert werden?

Nein, alle Zähler arbeiten völlig unabhängig voneinander. Der Signalzustand am Ausgang eines nicht initialisierten Zählers ist allerdings undefiniert, daher sollten diese Ausgänge frei bleiben.

Wann muss der Zähleranfangsswert geladen werden?

Erst nach der Initialisierung der Betriebsart, aber nicht unmittelbar danach. So können beispielsweise erst die Betriebsarten der Zähler in beliebiger Reihenfolge initialisiert und danach die Anfangswerte der Zähler (auch in beliebiger Reihenfolge) geladen werden.

Was ist beim Laden des Zähleranfangswertes zu beachten?

Das Laden des Zähleranfangswertes muss genau in der Reihenfolge erfolgen, die im Steuerwort mit RL0 und R11 festgelegt wurde. Absolut notwendig ist es auch, die damit festgelegte Anzahl von Bytes (1 oder 2) einzuhalten.

Muss vor einem neuen Zähleranfangswert auch die Betriebsart definiert werden?

Nein, denn die Betriebsart und der Zähleranfangswert werden in getrennten Registern gespeichert.

Was ist beim Lesen der Zählerstände zu beachten?

Beim Lesen ohne vorheriges Zwischenspeichern darf der Zähler keine Taktimpulse erhalten, damit er während des Lesens seinen Wert nicht verändert. Beim Lesen eines zwischengespeicherten Wertes muss der Lesevorgang unbedingt vor dem Einschreiben neuer Zähleranfangswerte abgeschlossen werden.

Beispiel zur Initialisierung

Nachdem die Bedeutung aller Bits des Statuswortes erklärt ist, soll die Initialisierung des Zähler- und Zeitgeber-Bausteins durch folgendes Beispiel verdeutlicht werden: Zähler Nr.1 soll binär in Betriebsart 3 mit einem Zähleranfangswert von 3F84 zählen.

Zunächst ist das Steuerwort mit allen darin enthaltenen Informationen festzulegen. Den Aufbau des Steuerwortes zeigt Bild 14.

Bild 14: Steuerwort für das Beispiel zur Initialisierung

Der Zähler 1 des Bausteins 8253 wird nun durch folgende Programmschritte initialisiert:

MVI A,076 ;Akku mit dem Wert des Steuerwortes (76h) laden

OUT 083 ;Akkuwert in das Steuerwort-Register schreibenDie Adresse 83 ergibt sich nach Bild 5, weil bei der Initialisierung das Steuerwort-Register geladen wird.

Anschließend, jedoch nicht unbedingt direkt danach, wird der Zähleranfangswert in den Zähler geschrieben. Hierbei muss die im Steuerwort mit D4 und D5 festgelegte Anzahl von Bytes ausgegeben werden, bevor der Zähler arbeiten kann. In diesem Fall sind dies nach Bild 9 zwei Bytes nacheinander, wobei zuerst das niederwertige und danach das höherwertige Byte zu laden ist. Das Einschreiben des Zähleranfangswertes geschieht mit Hilfe des folgenden Programms:

MVI A,084 ;Zuerst NW-Byte des Zählers in das

OUT 0B1 ;Zwischenregister des Zählers 1 schreiben

MVI A,03F ;Danach HW-Byte des Zählers

OUT 0B1 ;einschreibenWeil der Zähler Nr.1 geladen wird, beträgt die Adresse in diesem Programm „B1“. Unmittelbar nach dem Einschreiben des zweiten Bytes beginnt in dieser Betriebsart der Zähler zu arbeiten.

Betriebsartenbeschreibung

In diesem Abschnitt werden nur die häufig verwendeten Betriebsarten des Zähler- und Zeitgeber-Bausteins ausführlich beschrieben, während auf die weniger benutzten Betriebsarten lediglich hingewiesen wird. Nähere Einzelheiten hierzu sind den Datenbüchern der Bauelemente-Hersteller zu entnehmen.

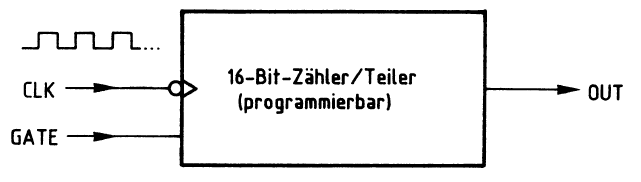

Bild 15 zeigt das Blockschaltbild und die Anschlüsse eines Zählers.

Bild 15: Blockschaltbild und Anschlüsse eines Zählers

Der Takteingang CLK ist negativ-flankengetriggert und wird mit dem zu zählenden Taktsignal verbunden.

Über den GATE-Anschluss kann die Arbeit der Stufe beeinflusst werden. Beispiele hierfür sind der Start oder die Unterbrechung einer Zählung.

Der Ausgang OUT nimmt abhängig vom Zählerstand und den verschiedenen Betriebsarten H- oder L-Pegel an. Generell gilt aber, daß der Ausgang des Zählers beim Zählerstand Null reagiert.

Betriebsart 0: Unterbrechen beim Zählerstand Null

In dieser Betriebsart arbeitet der Zähler nach der Initialisierung und der Zählervoreinstellung nicht zyklisch, sondern nur einmal. Beim Erreichen des Zählerstandes Null unterbricht der Zähler seine Arbeit und kann nur vom Prozessor neu dazu veranlasst werden.

Die Betriebsart 0 besitzt folgende wesentliche Merkmale:

- Nach der Initialisierung führt „0UT“ L-Pegel, der Zähler arbeitet jedoch noch nicht. Erst nach dem Laden des Zähleranfangswertes beginnt das Zählen, wobei zunächst aber weiterhin L-Pegel am Ausgang anliegt.

- Beim Erreichen des Zählerstandes Null nimmt „0UT“ H-Signal an, und der Zähler unterbricht seine Arbeit.

- Dieser Zustand bleibt erhalten, bis der Vorgang durch erneutes Laden des Zähleranfangswertes wieder gestartet wird.

- L-Signal an „GATE“ stoppt den Zählvorgang, H-Signal gibt ihn wieder frei.

- Wird während des Zählens ein neuer Anfangswert in den Zähler geschrieben, so unterbricht der Zähler seine Arbeit. Nach dem Laden des neuen Wertes beginnt er, mit diesem neuen Wert zu zählen.

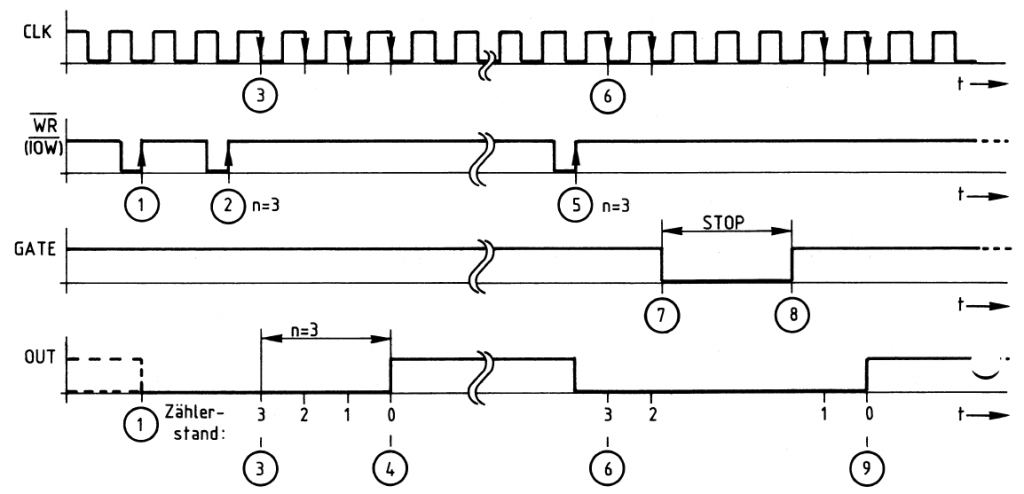

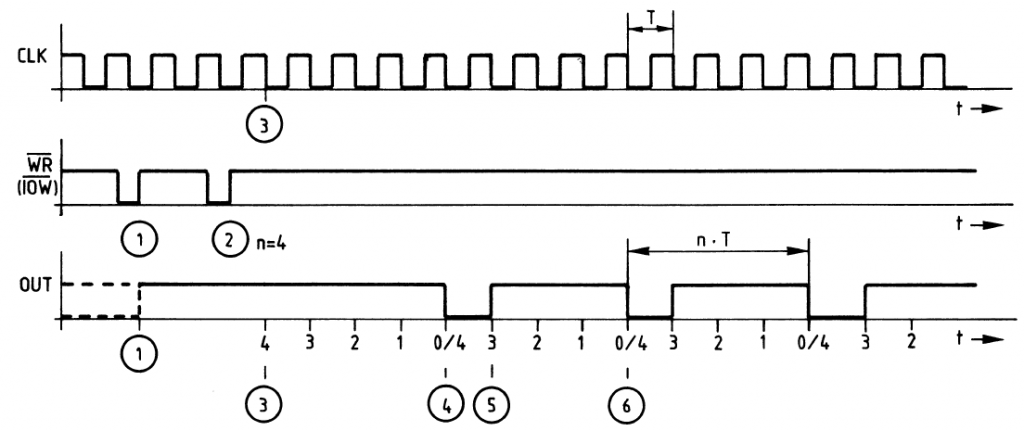

Bild 16 zeigt die wichtigsten zusammenhänge der Betriebsart O im Impulsdiagramm.

Bild 16: Impulsdiagramm zur Betriebsart 0

Erläuterungen zu Bild 16:

(1) Mit der positiven Flanke des WRITE-Signals vom Prozessor („IOW“) wird das Steuerwort für die Betriebsart 0 in das Status-Register des Bausteins geschrieben. „OUT“ führt nun L-Signal. Der Zähler arbeitet noch nicht.

(2) Nun wird der Zähleranfangswert mit einem oder mit zwei Schreibzyklen (je nach Definition lt. Bild 9) in das Zwischenregister des Zählers (Bild 6) geladen. In Bild 16 wird der Wert „311 mit einem Zyklus geladen.

(3) Durch den nächsten H-L-Sprung des Taktes CLK erfolgt die Obernahme des Zähleranfangswertes vom Zwischenregister in das Zählregister (Bild 6). Die Zählung beginnt. Mit jedem weiteren Takt verringert sieh der Zähl erstand um den Wert „1“.

(4) Drei Takte nach dem Start der Zählung ist der Zähl erstand „0 11 erreicht und „OUT“ nimmt H-Pegel an. Hierdurch meldet der Zähler, dass er seine Arbeit beendet hat. „OUT“ führt nun solange H-Pegel, bis der Vorgang neu eingeleitet wird.

(5) Nach einer beliebigen Zeit wird zum Zeitpunkt (5) wieder ein Zähleranfangswert (z.B. der alte Wert) in das Zwischenregister geladen. Sofort nimmt „0UT“ L-Pegel an.

(6) Durch Obernahme ins Zählregister beginnt der Zählvorgang neu.

(7) Der Anschluss „GATE“ erhält L-Pegel, wodurch die gerade 1 auf ende Zählung unterbrochen wird.

(8) Durch H-Signal an 11GATE 11 wird die Zählung wieder freigegeben.

(9) Der Zähler hat wieder den Stand 11011 erreicht und nimmt an „OUT“ H-Signal an. Der Zählvorgang wurde durch L-Si gnal an „GATE“ um den Zeitabschnitt von (7) bis (8) verlängert.

Die Betriebsart 0 wird vor allem zur Interrupt-Steuerung eines Mikrocomputers verwendet. Unter „Interrupt“ versteht man in diesem Zusammenhang die vorübergehende Unterbrechung eines gerade laufenden Programmes beim Auftreten eines wichtigen Ereignisses, das durch die Bearbeitung eines Sonderprogramms vorrangig behandelt wird.

Betriebsart 1: Monostabile Kippstufe, retriggerbar

Durch diese Betriebsart wird die Funktion einer Monostabilen Kippstufe nachgebildet, deren Schaltzeit durch die Zählervoreinstellung in weiten Grenzen wählbar ist. Das Auslösen dieser Funktion geschieht dabei nicht durch den Mikroprozessor, sondern durch einen Impuls am GATE-Eingang des Zählers, der damit als Triggereingang fLlr die Monostabile Kippstufe wirkt.

Tritt während der Zählphase bzw. der aktiven Zeit der Monostabilen Kippstufe am GATE-Eingang ein weiterer Impuls auf, so wird die Kippstufe nachgetriggert, d.h., der Zählvorgang beginnt ohne Unterbrechung wieder mit dem Zähleranfangswert. Diese Eigenschaft wird mit dem Begriff „retriggerbar“ bezeichnet und ist auch bei Monostabilen Kippstufen in TTL- und CMOS-Technik verbreitet.

Die Betriebsart 1 besitzt folgende Merkmale:

- Nach der Initialisierung führt „OUT“ H-Pegel. Dies bleibt auch nach der anschließenden Registervoreinstellung so: Die Stufe arbeitet noch nicht.

- Eine positive Signalflanke am GATE-Eingang startet den Zähler, wodurch „OUT“ L-Signal annimmt.

- Beim Erreichen des Zählerstandes Null nimmt „OUT“ H-Signal an, und der Zähler unterbricht seine Arbeit.

- Dieser Zustand bleibt erhalten, bis der Zähler durch einen neuen Triggerimpuls wieder gestartet wird.

- Positive Taktflanken, die während der Zählarbeit am GATE-Eingang eintreffen, triggern den Zähler neu. Er zählt ohne Reaktion am Ausgang von Beginn an neu.

- Das Einschreiben eines neuen Zähleranfangswertes während der aktiven Phase hat keinen Einfluss auf den gerade laufenden Zählvorgang. Der neue Wert wird erst nach erneutem Triggern übernommen.

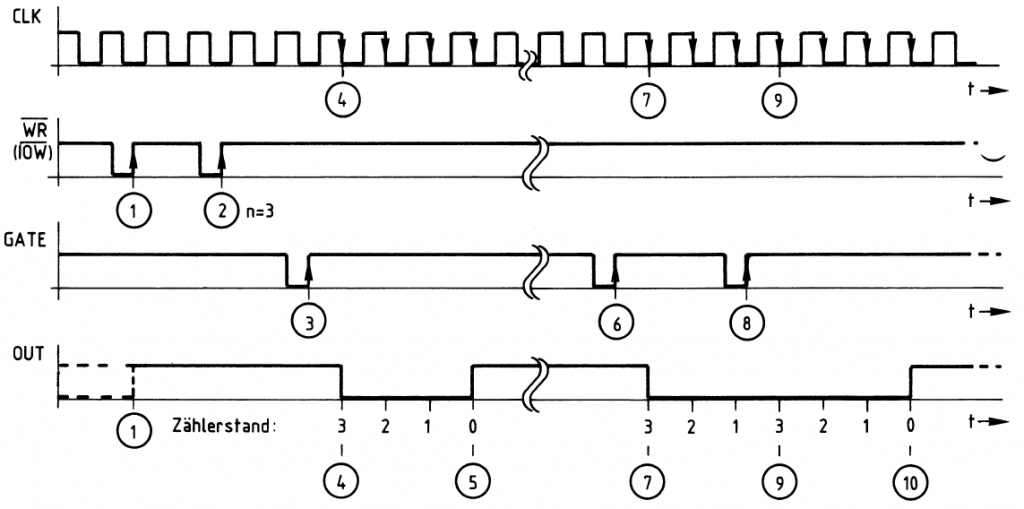

Bild 17 zeigt die wichtigsten Zusammenhänge der Betriebsart 1 im Impulsdiagramm.

Bild 17: Impulsdiagramm zur Betriebsart 1

Erläuterungen zu Bild 17:

(1) Mit der positiven Flanke des WRITE-Signals („IOW“) wird das Steuerwort für die Betriebsart 1 in das Steuerwort-Register des Bausteins geschrieben. Der Ausgang „0UT“ führt nun H-Signal, der Zähler arbeitet jedoch noch nicht.

(2) Nun wird der Zähleranfangswert mit einem oder mit zwei Schreibzyklen (je nach Definition lt. Bild 9} in das Zwischenregister geladen. In Bild 17 wird der Wert „3“ mit einem Zyklus geladen. Die Zählung beginnt jedoch noch nicht.

(3) Erst eine positive Signalflanke am GATE-Anschluss triggert die Schaltung bzw. löst das Zählen aus.

(4) Durch den nächsten Takt erfolgt die Obernahme des Zähleranfangswertes vom Zwischenregister in das Zählregister. Die Zählung beginnt. Mit jedem weiteren Takt verringert sich der Zählerstand um den Wert „1“

(5) Drei Takte nach der Zählerübernahme ist der Zählerstand „0“ erreicht, und „0UT“ nimmt H-Pegel an. Hierdurch meldet der Zähler, daß er seine Arbeit beendet hat. „0UT“ führt nun solange H-Pegel, bis die Monostabile Kippstufe erneut getriggert wird.

(6) Nach einer beliebigen Zeit trifft wieder eine neue positive Signalflanke am GATE-Anschluss ein.

(7) Durch Obernahme des Zähleranfangswertes in den Zähler beginnt der Zählvorgang erneut.

(8) Während des Zählens wird die Stufe nachgetriggert.

(9) Der Zähler wird durch das Nachtriggern wieder mit seinem Anfangswert geladen und beginnt von vorn zu zählen.

(10) Nach weiteren drei Takten hat der Zähler den Stand „0“ erreicht und nimmt an „0UT“ H-Signal an. Der Zählvorgang wurde durch die Nachtriggerung um den Zeitabschnitt von (7) bis (9) verlängert.

Betriebsart 2: Programmierbarer Frequenzteiler

Diese Betriebsart kann dazu verwendet werden, die Frequenz eines Taktsignals zu teilen, wobei frei wählbare Teilfaktoren zwischen 2 und 65535 möglich sind. Nach der Initialisierung des Bausteins und dem Laden des Zähleranfangswertes beginnt die Frequenzteilung und wird zyklisch fortgesetzt. Die Betriebsart 2 besitzt folgende Merkmale:

Nach der Initialisierung führt „0UT“ H-Pegel, ohne dass der Zähler arbeitet.

Die Frequenzteilung beginnt nach dem Laden des Zähleranfangswertes als gewünschtem Teilfaktor. Am Ausgang liegt zunächst weiterhin H-Pegel.

Beim Erreichen des Zählerstandes Null geht „0UT“ für eine Taktperiode auf L-Pegel. Gleichzeitig wird der Zähler automatisch aus dem Zwischenregister mit dem Zähleranfangswert nachgeladen und gestartet.

Bei L-Signal am GATE-Anschluss stoppt der Zähler, sein Ausgang bleibt auf H-Pegel. Geht der GATE-Eingang wieder auf H-Pegel, startet der Zähler von vorn. Mit dem GATE-Eingang kann so ein gezielter Beginn der Frequenzteilung zu einem gewünschten Zeitpunkt („Synchronisation“) bewirkt werden.

Das Einschreiben eines neuen Teilfaktors wirkt sich erst zu Beginn einer neuen Zählphase aus. Die gerade laufende Periode wird hierdurch nicht beeinflusst. Bild 18 zeigt das Wesentliche der Betriebsart 2 im Impulsdiagramm.

Bild 18: Impulsdiagramm zur Betriebsart 2

Erläuterungen zu Bild 18:

(1) Mit der positiven Flanke des WRITE-Signals („IOW“) wird das Steuerwort für die Betriebsart 2 in das Steuerwort-Register des Zählers geschrieben. Der Ausgang „OUT“ führt nun H-Signal, der Zähler arbeitet noch nicht.

(2) Nun wird der Zähleranfangswert bzw. der gewünschte Teilfaktor mit einem oder mit zwei Schreibzyklen in das Zwischenregister geladen. In Bild 18 ist dies der Wert „4“ mit einem Zyklus.

(3) Durch den nächsten Takt erfolgt die Obernahme des Zähleranfangswertes vom Zwischenregister in den Zähler, die Zählung beginnt. Mit jedem weiteren Takt verringert sich der Zählerstand um den Wert „1“.

(4) Vier Takte nach der Zählerübernahme ist der Zählerstand „0“ erreicht, und „OUT“ nimmt für eine Taktperiode L-Pegel an. Gleichzeitig wird der Zähleranfangswert wieder aus dem Zwischenregister in den Zähler geladen.

(6) Vier Takte nach der letzten Nullstellung des Zählers zum Zeitpunkt (4) ist wieder Null erreicht. Alle folgenden Perioden der Ausgangsspannung sind n-mal so lang wie die Taktperiode. Somit ist die Taktfrequenz durch n geteilt.

Im Impulsdiagramm von Bild 18 sind der Einfluss des GATE-Anschlusses und die Ladung eines neuen Zähleranfangswertes nicht berücksichtigt, weil dies nicht übersichtlich dargestellt werden kann. Entsprechende Hinweise finden Sie bei der Beschreibung der Merkmale dieser Betriebsart.

Betriebsart 3: Programmierbarer symmetrischer Rechteckgenerator

In der Betriebsart 3 wird ebenso wie in der Betriebsart 2 die Frequenz des Taktsignals geteilt. Im Gegensatz zur Betriebsart 2 tritt hier jedoch die Ausgangsspannung mit gleich langen H- und L-Anteilen auf (symmetrisch).

Dies gilt jedoch nur bei geradzahligen Zähleranfangswerten. Bei ungeradzahligen Zähleranfangswerten ist die H-Zeit am Ausgang etwas größer als die L-Zeit. Die genaue Berechnung erfolgt nach den folgenden Gleichungen:

Geradzahliger Teilfaktor

th = tL = T * n/2Ungeradzahliger Teilfaktor

tH = T * (n+1) / 2

tL = T * (n-1) / 2tH: Zeit mit H-Pegel am Ausgang

tL: Zeit mit L-Pegel am Ausgang

T: Periodendauer des Taktsignals

n: Teilfaktor, Zähleranfangswert

Bei einem angenommenen Teilfaktor von 9 (n = 9) tritt während 5 Eingangstakten H-Pegel und während 4 Eingangstakten L-Pegel am Ausgang auf. Die Summe beider Zeiten ergibt die Periodendauer der Ausgangsspannung. Mit grösser werdenden Teilfaktoren verringert sich der Symmetriefehler immer mehr.

Alle weiteren Merkmale der Betriebsart 3 entsprechen denen der Betriebsart 2. Auf ein Impulsdiagramm wird verzichtet.

Betriebsart 4: Verzögerter Impuls, Programmtriggerung

Nach der Initialisierung des Bausteins und der Registervoreinstellung beginnt der Zähler zu arbeiten. Er gibt beim Erreichen des Zählerstandes Null einen L-Impuls von der Länge eines Taktes an „OUT“ ab und stellt danach seine Arbeit ein.

Durch erneutes Einschreiben eines Zähleranfangswertes kann der Zähler wieder gestartet und somit vom Betriebsprogramm „durch Software“ bzw. durch eine Programmlogik (nicht durch eine Schaltungslogik) getriggert werden.

Werden während der Zählphase weitere „Triggerimpulse“ ausgelöst, womit das Einschreiben neuer Zähleranfangswerte gemeint ist, beginnt der Zähler jedesmal wieder von vorn zu zählen. Hierdurch verzögert sich die Abgabe des Ausgangsimpulses beim Zählerstand Null immer mehr. Dies kann als „Retriggern durch Software“ bezeichnet werden. Es führt dazu, dass erst nach dem Ausbleiben von

Einschreibsignalen ein verzögerter Impuls abgegeben wird, dessen Verzögerung durch das letzte Einschreiben bestimmt ist.

Die Betriebsart 4 besitzt folgende Merkmale:

- Nach der Initialisierung führt „0UT“ H-Pegel, der Zähler arbeitet jedoch noch nicht. Erst nach der Registervoreinstellung mit dem Zähleranfangswert beginnt das Zählen, wobei zunächst weiterhin H-Pegel am Ausgang liegt.

- Beim Erreichen des Zählerstandes Null nimmt „0UT“ für die Dauer eines Taktes L-Signal an und geht anschließend wieder auf H-Pegel. Der Zähler stellt dann seine Arbeit ein.

- Dieser Zustand bleibt erhalten, bis der Vorgang durch erneutes Laden eines Zähleranfangswertes wieder ausgelöst („getriggert“) wird.

- Wird während des Zählens ein neuer Anfangswert in den Zähler geschrieben, so zählt der Zähler sofort mit diesem Wert weiter. Hierdurch verzögert sich die Abgabe des Ausgangsimpulses so lange, bis der zuletzt eingeschriebene Wert abgearbeitet ist.

- L-Signal an „GATE“ stoppt vorübergehend den Zählvorgang, H-Signal gibt ihn wieder frei.

Auf ein Impulsdiagramm zu dieser Betriebsart wird verzichtet. Weitere Einzelheiten hierzu sind den Datenbüchern der Hersteller zu entnehmen.

Betriebsart 5: Verzögerter Impuls, externe Triggerung

Diese Betriebsart ist ähnlich der Betriebsart 4. Nach ihrer Initialisierung und der Registervoreinstellung arbeitet der Zähler aber erst, wenn er durch eine positive Signalflanke am Eingang 11GATE11 getriggert wird.

Beim Erreichen des Zählerstandes Null gibt der Zähler einen Impuls von der Länge eines Taktes ab und stellt anschließend seine Arbeit ein.

Durch eine neue Signalflanke am GATE-Eingang kann der Zähler jederzeit wieder gestartet und somit von der äußeren Schaltung „getriggert“ werden.

Treten während der Zählphase weitere Triggerimpulse am GATE-Anschluss auf, beginnt der Zähler jedesmal wieder von vorn zu zählen. Hierdurch verzögert sich die Abgabe des Ausgangsimpulses beim Zählerstand Null immer mehr. Dies ist ein typischer Nachtriggervorgang, der dazu führt, dass erst nach dem Ausbleiben der letzten positiven GATE-Flanke ein verzögerter Impuls abgegeben wird.

Die Betriebsart 5 besitzt folgende Merkmale:

- Nach der Initialisierung führt „0UT“ H-Pegel. Auch nach der anschließenden Registervoreinstellung bleibt dies so, denn der Zähler arbeitet noch nicht.

- Eine positive Signalflanke an „GATE“ startet den Zähler, der jedoch weiterhin H-Signal am Ausgang abgibt.

- Beim Erreichen des Zählerstandes Null nimmt „0UT“ für die Dauer eines Taktes L-Signal an und stellt anschließend seine Arbeit ein.

- Dieser Zustand bleibt erhalten, bis der Vorgang durch einen erneuten Triggerimpuls am GATE-Anschluss wieder gestartet wird.

- Positive Taktflanken, die während des Zählens am GATE-Eingang eintreffen, triggern den Zähler neu. Sofort zählt er wieder von Beginn an. Hierdurch verzögert sich die Abgabe des Ausgangsimpulses so lange, bis zwischen zwei GATE-Impulsen genügend Zeit verbleibt, den Zähler ganz auf Null herabzuzählen.

- Das Einschreiben eines neuen Zähleranfangswertes während der aktiven Phase hat keinen Einfluss auf den gerade laufenden Zählvorgang. Der neue Wert wird erst durch den nächsten Triggerimpuls übernommen.

Auf ein Impulsdiagramm zu dieser Betriebsart wird verzichtet. Weitere Einzelheiten hierzu sind den Datenbüchern der Hersteller zu entnehmen.

Schaltungsbeschreibung und Interruptsteuerung

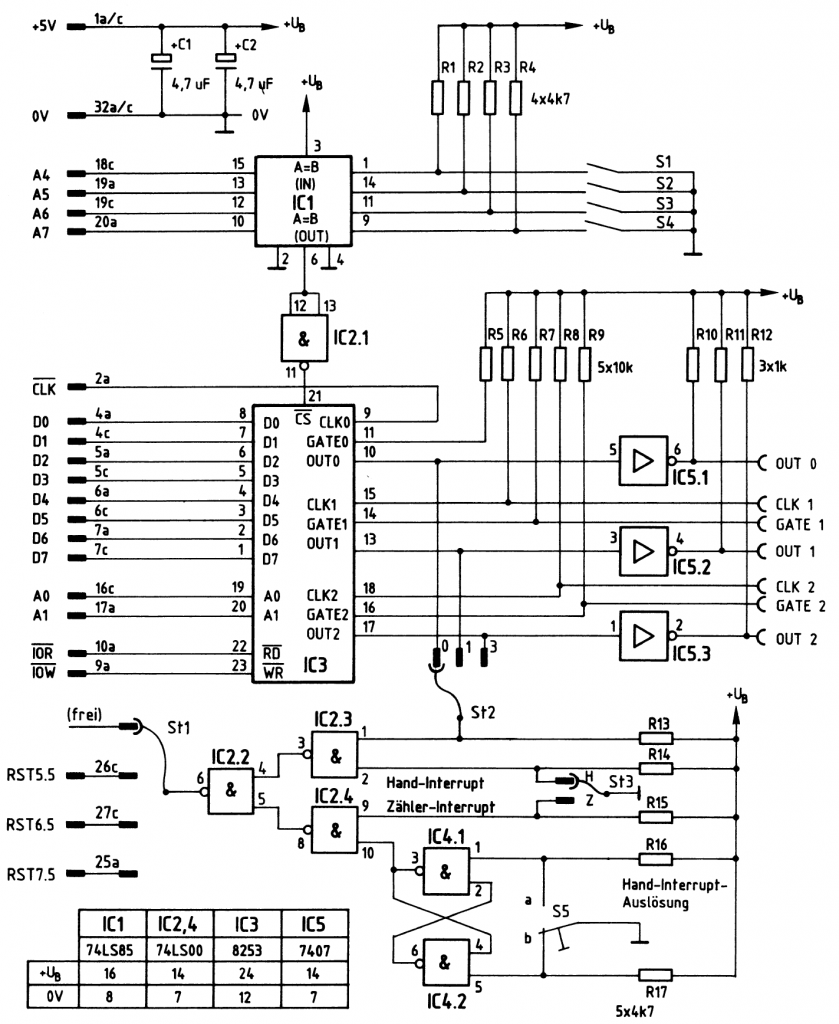

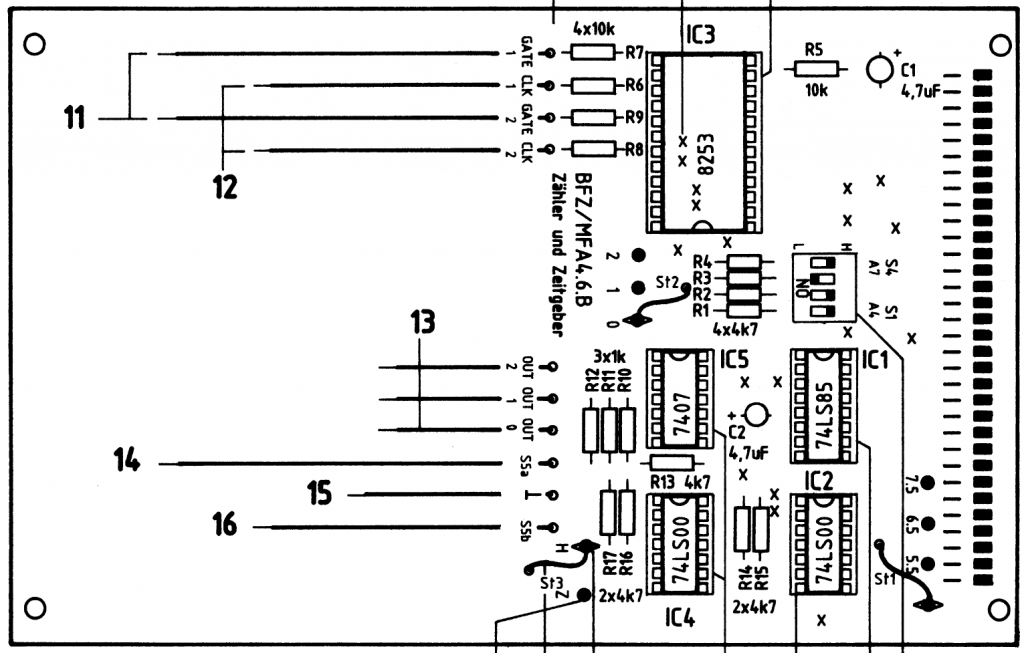

Bild 19 zeigt den Stromlaufplan der Baugruppe „Zähler und Zeitgeber“

Die Betriebsspannung wird über die Federleistenanschlüsse 1a/c (5 V) und 32a/c (0V) zugeführt und durch die Kondensatoren C1 und C2 abgeblockt.

IC1 bildet mit den Leitungen A4 bis A7, den Schaltern Sl bis S4 und den Widerständen R1 bis R4 den Adreßvergleicher.

Durch L-Signal an Pin 21 (CS, Chip-Select) wird der Zähler- und Zeitgeber-Baustein 8253 (IC3) bei Adressengleichheit freigegeben und kann über die Leitungen D0 bis D7 Daten vom Prozessor empfangen oder an ihn abgeben.

Die Adressleitungen A0und A1 dienen zur Auswahl der im Inneren von IC3 vorhandenen Zähler und des Steuerwort-Registers. Die Leitungen IOR und IOW lösen das Lesen bzw. Schreiben der Daten aus.

Bild 19: Stromlaufplan

Der Taktanschluss „CLK0“ des Zählers 0 ist über die Leitung 2a fest mit dem 2-MHz-Systemtakt „CLK“ des Prozessors verbunden. Die Taktanschlüsse der anderen Zähler (CLK1 und CLK2) und die GATE-Anschlüsse „GATE0“ , „GATE1“ und „GATE2“ führen durch die Pull-Up-Widerstände RS bis R9 H-Pegel. Außer „GATE 0“ sind sie mit Buchsen auf der Frontplatte verbunden.

Die drei Zählerausgänge „0UT0“, „0UT1“ und „0UT2“ führen über Open-CollektorTreiberstufen zu entsprechenden Ausgangsbuchsen. Durch den Einsatz dieser Treiber sind die Ausgänge kurzschlußfest. RIO bis R12 wirken als Arbeitswiderstände.

Bisher nicht näher eingegangen wurde auf die „Interrupt-Steuerung“. Sie besteht aus den Schaltkreisen IC2 und IC4, den Widerständen R13 bis R17 und den Steckbrücken St1 bis St3.

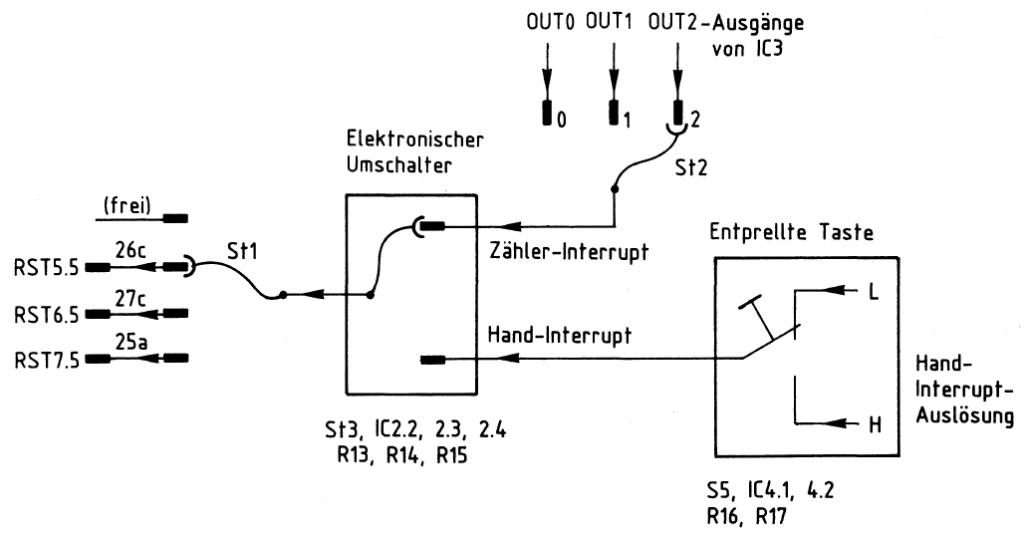

Jeweils ein Zählerausgang des Zähler- und Zeitgeber-Bausteins 8253 kann durch die Steckbrücke St2 mit dem Eingang der Interrupt-Steuerung verbunden werden. Bild 20 zeigt die Wirkungsweise der Interrupt-Steuerung in vereinfachter Form.

Bild 20: Wirkungsweise der Interrupt-Steuerung

In der gezeichneten Stellung des 11Elektronischen Umschalters11 (Bild 20) wird das mit St2 ausgewählte Ausgangssignal von IC3 auf eine der Interruptleitungen RST 5.5 bis RST 7 .5 geführt. In der anderen Stellung des elektronischen Umschalters kann zu Prüfzwecken das Signal der „Entprellten Taste“ auf die Interruptleitungen durchgeschaltet werden. Wird kein Interrupt gewünscht, kommt St1 in die Freiposition.

Das Auftreten eines Signals auf den Interruptleitungen (H-Pegel oder L/H-Übergang, je nach gewähltem Interrupt) löst im Prozessor 8085 einen Interrupt aus, wodurch die momentane Arbeit unterbrochen wird. Dies ist bei der Baugruppe „Zähler und Zeitgeber“ beim Erreichen des Zählerstandes Null oder (nur zu

Prülfzwecken) bei Betätigung der entprellten Taste der Fall. Zur Erzielung von Interrupts ist die Betriebsart 0 des Zähler- und Zeitgeber-Bausteins vorgesehen, worauf schon im Abschnitt 5.1. hingewiesen wurde.

„RST 5.5“ ist die Abkürzung für „Restart Nr. 5.5“ und bedeutet wörtlich übersetzt „Rückstart Nr. 5.5“. Entsprechendes gilt für die anderen Restartmöglichkeiten, hinter denen sich schaltungs- und programmgesteuerte Eigenschaften der CPU verbergen. Diese sind sehr vielfältig und werden nicht näher behandelt.

Prüfen der Zähler des Zeitgeber-Bausteins 8253

Zum Prüfen der in IC3 vorhandenen Zähler ist ein Taktsignal erforderlich, das der Baugruppe „Prozessor 8085“ entnommen wird. Außerdem muss IC3 durch ein kleines Programm initialisiert werden, das die Betriebsart und die Zählerkonstanten festlegt. Dieses Programm wird mit Hilfe des Bus-Signalgebers eingegeben. Baugruppe „Prozessor 8085“ zusätzlich in den Rahmen einstecken.

Im „Zähler und Zeitgeber“ muss mit S1 bis S4 die Baugruppennummer BX (z.B. B0 eingestellt sein.

Verbinden Sie die Buchse „0UT0“ mit der Buchse „CLK1“ und außerdem „0UT1“ mit „CLK2“. Hierdurch werden die drei Zählerstufen innerhalb von IC3 hintereinandergeschaltet.

Geben Sie die folgenden Initialisierungs-Bytes für IC3 mit Hilfe des Bus-Signalgebers von links beginnend ein.

Hierbei wird zunächst der Adress- und dann der Datenwert am Bus-Signalgeber eingestellt. Durch Betätigung der Taste 11 IOW11 erfolgt anschließend die Übergabe der Daten in den Zähler- und Zeitgeber-Baustein.

Wenn Ihnen bei der Programmierung ein Fehler unterläuft, sollten Sie die ganze Tabelle neu eingeben. Hierdurch können Sie sicherstellen, dass IC3 richtig initialisiert wird.

| ADDRESS | B3 | B3 | B3 | B2 | B1 | B0 | B0 |

| DATA | 36 | 55 | A7 | 20 | 10 | 90 | 01 |

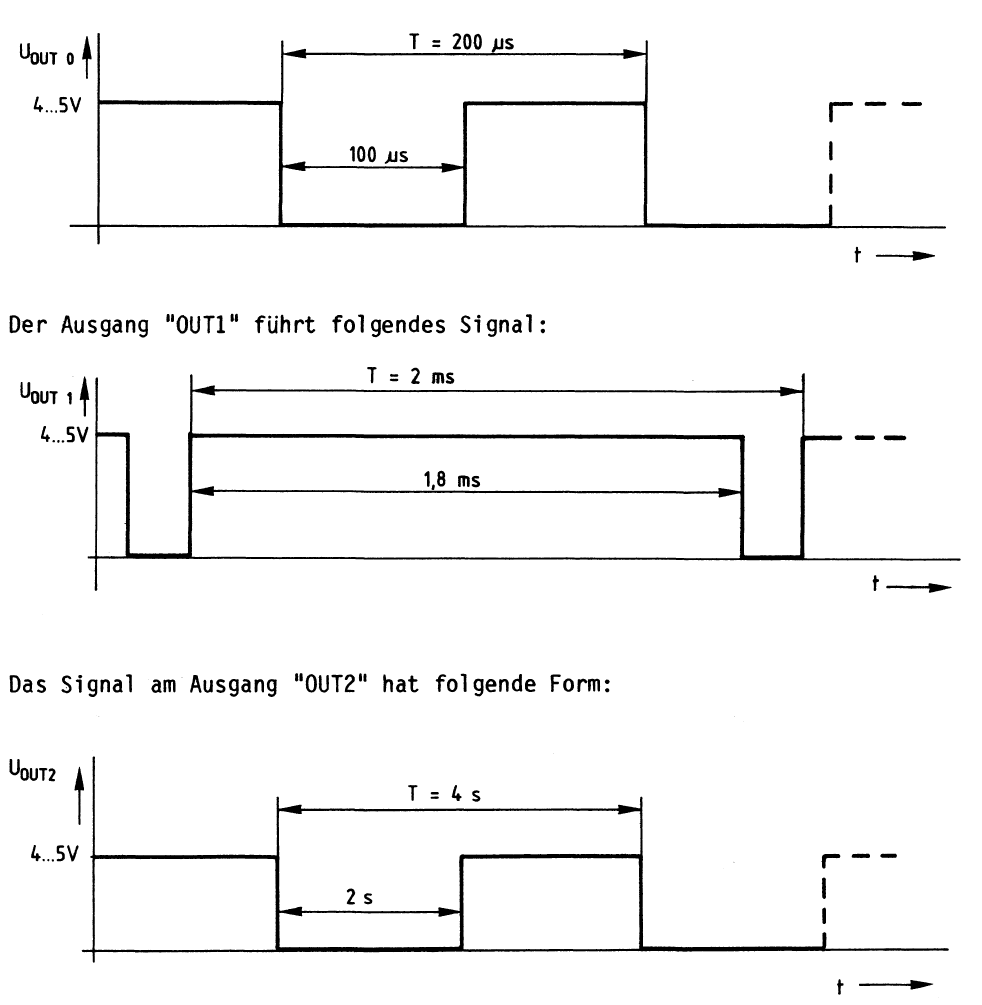

Die richtige Arbeitsweise des Zählers und Zeitgebers kann nun mit

einem Oszi 11 oskop überprüft werden. Am Ausgang 110UT011 muß folgendes

Signal auftreten:

Diese drei Diagramme dienen in einem späteren Arbeitsschritt dazu, die durch die Initialisierung vorgegebenen Teilerverhältnisse des Zähler- und Zeitgeber-ICs zu bestimmen.

Gatesteuerung, Taktflankensteuerung und Teilerverhältnisse

IC3 besitzt drei voneinander unabhängige 16-Bit-Zähl- bzw. Teilerstufen, deren Teilerfaktoren durch die Initialisierung bestimmt wurde. Jede Stufe hat einen Gate- und einen Clock-Eingang sowie einen Signalausgang. Das folgende Bild zeigt die augenblickliche Verbindung der drei Zählstufen miteinander.

Die Arbeit der Zählstufe 0 kann von der Frontplatte her nicht beeinflusst werden, da ihr Gate- und Clock-Anschluss nicht herausgeführt ist, sondern beide Leitungen innerhalb der Baugruppe fest verdrahtet sind.

Wirkung der Gate-Anschlüsse

Die logischen Zustände der Gate-Anschlüsse „GATE2“ , „GATE1“ und „GATE0“ bestimmen, ob die drei innerhalb von IC3 vorhandenen Zählstufen überhaupt zählen können. Durch die Pull-Up-Widerstände RS, R7 und R9 führen alle Gate-Anschlüsse in unbeschaltetem Zustand H-Pegel, wodurch die Zählstufen zum Arbeiten vorbereitet sind.

Wenn der Eingang „GATE2“ durch eine Verbindung mit 0 V L-Pegel erhält, wird die Arbeit des Zählers 2 unterbrochen und „0UT2“ nimmt sofort H-Pegel an. Bitte überprüfen Sie dies.

Bei L-Pegel nur an „GATE1“ nimmt „OUT1“ sogleich H-Pegel an, da jetzt die Arbeit der Zählstufe 1 unterbrochen wird. Der Ausgang „0UT2“ verändert sich hierdurch nicht, weil die Zählstufe 2 lediglich keine Taktimpulse mehr von „0UT1“ erhält und deshalb in ihrem momentanen Zustand (H- oder L-Signal an „OUT2“) bleibt. Kontrollieren Sie auch dies nach.

Die Arbeit der Zählstufe 0 kann von der Frontplatte her nicht beeinflusst werden, da ihr Gate- und Clock-Anschluss nicht herausgeführt ist, sondern beide Leitungen innerhalb der Baugruppe fest verdrahtet sind.

Taktflankensteuerung

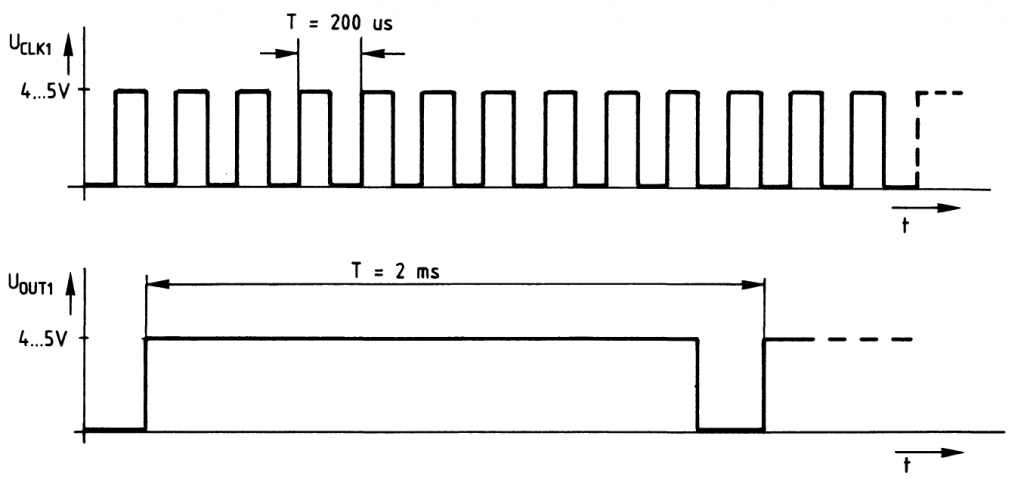

Im folgenden Bild ist das Eingangssignal „CLK1“ der Zählstufe 1 und das dazugehörende Ausgangssignal „OUT1“ zeitrichtig untereinander dargestellt. überprüfen Sie diese Diagramme mit einem Zweikanaloszilloskop.

Es fällt auf, daß das Eingangssignal der Zählstufe 1 („CLK1“) zeitlich symmetrisch, das Ausgangssi nal „0UT1“ jedoch unsymmetrisch ist. Dies liegt an der Initialisierung des Zähler- und Zeitgeber-ICs, mit der die Arbeitsweise jedes Zählers getrennt bestimmt werden kann. Weitere Einzelheiten stehen in der

Funktionsbeschreibung. Beim vorliegenden Prüfaufbau wurden die Stufen 0 und 2 als symmetrische Frequenzteiler programmiert, die Stufe 1 jedoch als unsymmetr1scher Teiler. Bitte überprüfen Sie dies anhand der Diagramme von A7.4.

Übersicht der Initialisierung des 8253

Die folgende Abbildung fasst die Initialisierung des Zähler-und Zeitgeber-Bausteins 8253 zusammen und ist als Arbeitshilfe gedacht.

Platine

Bestückungsplan

Verdrahtungsplan