Einleitung

Jeder Mikrocomputer enthält neben dem Prozessor und dem Speicher Ein- und Ausgabeeinheiten, über die der Datenverkehr mit Geräten außerhalb des Mikrocomputers stattfindet. Häufig bezeichnet man Ein- und Ausgabeeinheiten als „Eingabe- bzw. Ausgabe-Ports“ oder als „Eingabe- bzw. Ausgabeschnittstellen“ und die Geräte außerhalb des Mikrocomputers als „Peripheriegeräte“.

Ein häufig verwendetes Peripheriegerät des Mikrocomputers ist ein Kassetten-Recorder zur externen Datenspeicherung. Zu seinem Anschluss an einen Computer ist ein 11Kassetten-Interface11 erforderlich.

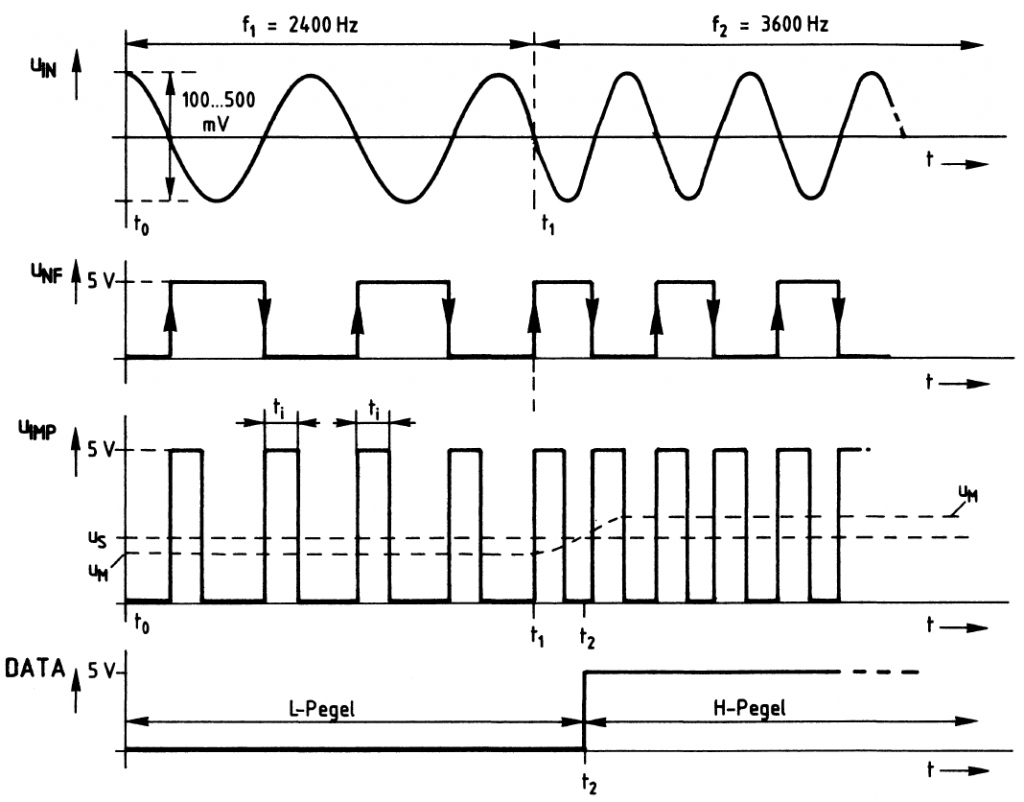

In dieser 0bung wird ein Kassetten-Interface beschrieben, dass nach dem „FSK-Verfahren“ (Frequency-Shift-Keying, Frequenzumtastung) arbeitet. Bild 1 zeigt das Prinzip dieses Verfahrens, das „FSK-Modulation“ genannt wird.

Bild 1: Prinzip der FSK-Modulation

Beim FSK-Verfahren nimmt eine Tonfrequenz in Abhängigkeit des Datenpegels zwei verschiedene Werte an. Im BFZ/MFA-Kassetten-Interface entspricht L-Signal einer Frequenz von 2400 Hz und H-Signal einer Frequenz von 3600 Hz. Diese Tonfrequenzen können von einem Kassetten-Recorder aufgezeichnet und von ihm auch wiedergegeben werden. Vor der Behandlung von Einzelheiten wird zunächst das Prinzip von Datenspeicherung und Datenwiedergabe mit Hilfe eines Kassetten-Recorders erläutert.

Das Prinzip der Datenspeicherung mit Hilfe eines Kassetten-Recorders

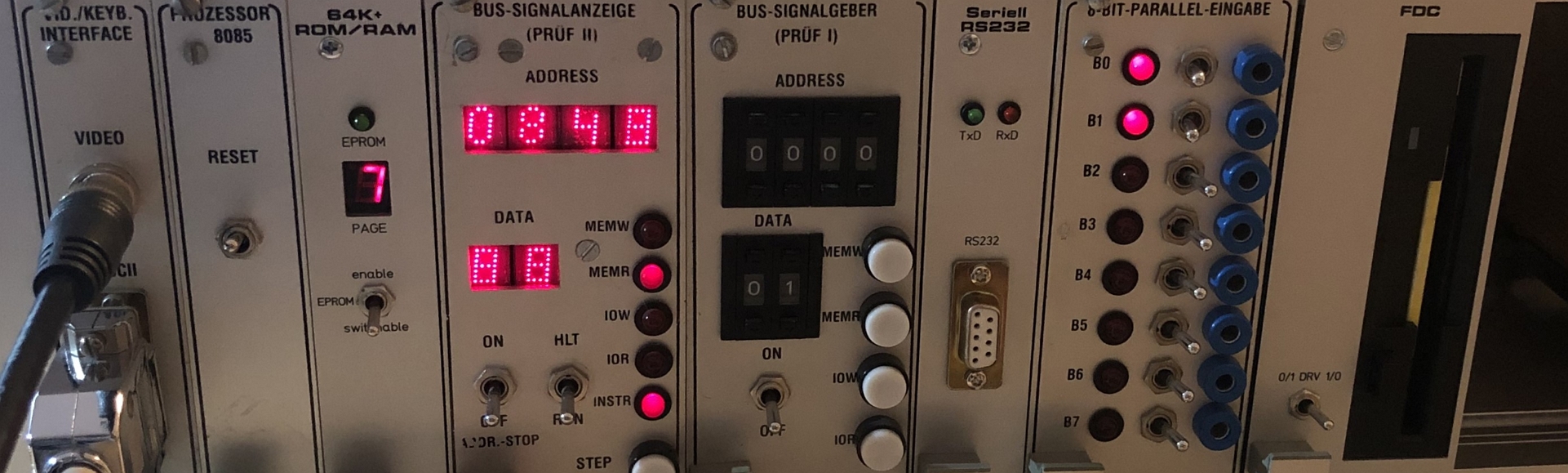

Bei der Datenspeicherung arbeitet der Kassetten-Recorder in der Betriebsart „Aufnahme“. Hierzu ist der in Bild 2 gezeigte Aufbau erforderlich.

Bild 2: Prinzip der Datenspeicherung auf einem Kassetten-Recorder

Die zu speichernden Daten gelangen vom Systembus zu einem Datensender, der die parallelen Daten des Mikrocomputers in einen seriellen Datenstrom umwandelt (Bild 2). Außerdem fügt der Sender die zur seriellen Datenübertragung erforderlichen Start- und Stoppbits in den Datenstrom ein. Dem Sender nachgeschaltet ist ein FSK-Modulator, der einen Tongenerator besitzt, dessen Frequenz -abhängig vom logischen Pegel der gesendeten Bits- auf zwei verschiedene Werte umgeschaltet (umgetastet) wird.

Bild 3 zeigt, welche Stufen beim Einlesen von gespeicherten Daten erforderlich sind. Der Kassetten-Recorder arbeitet hierbei in der Betriebsart „Wiedergabe“.

Bild 3: Prinzip der Datenwiedergabe von einem Kassetten-Recorder

Die vom Kassetten-Recorder gelieferten Tonsignale werden zunächst verstärkt (Bild 3). Der anschließende FSK-Demodulator gibt an seinem Ausgang L-Pegel ab, wenn die empfangene Frequenz geringer als 3000 Hz ist. Oberhalb von 3000 Hz liefert er H-Pegel. Im Empfänger werden die seriellen Daten wieder in die

parallele Form gewandelt und von Start- und Stopp-Bits befreit. Die empfangenen Daten gelangen auf den Systembus des Mikrocomputers.

Blockschaltbild, Aufbau und Wirkungsweise des Kassetten-Interfaces

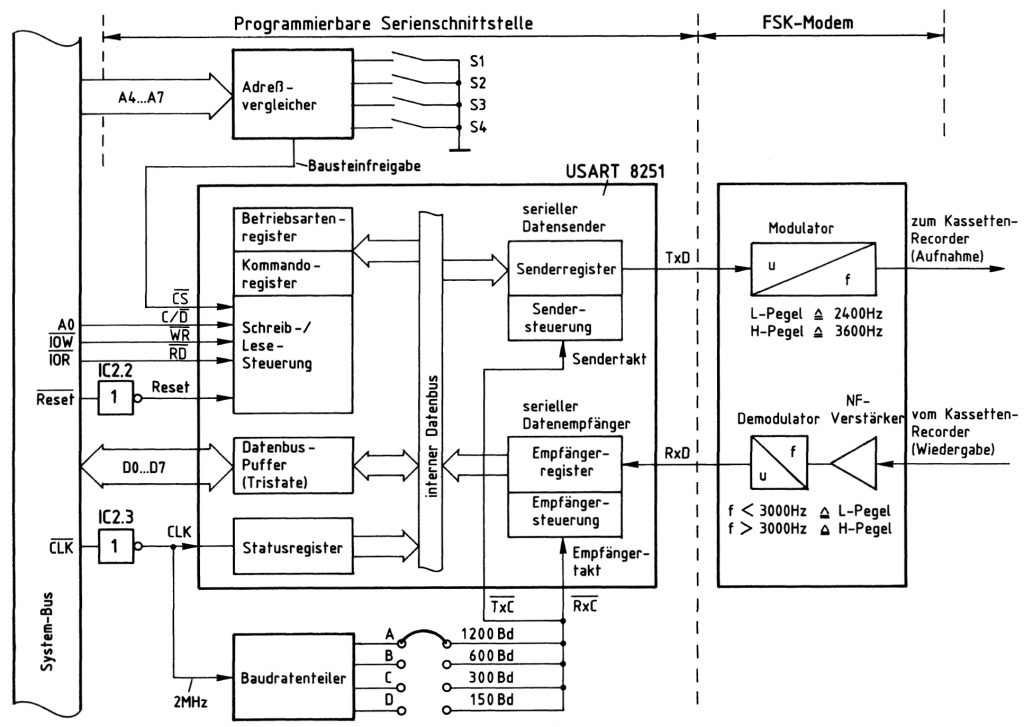

Bild 4 zeigt das Blockschaltbild des Kassetten-Interfaces. Serieller Sender, Empfänger und die erforderliche Steuerlogik befinden sich im Teil „Programmierbare Serienschnittstellen“, deren Erklärung auf die Anwendung im Kassetten-Interface beschränkt wird. Darüber hinausgehende Einzelheiten und Grundlagen der seriellen Datenübertragung sind in der Fachpraktischen Übung BFZ/MFA 4.4. „Programmierbare Serienschnittstellen“ beschrieben.

FSK-Modulator, -Demodulator und NF-Verstärker des Kassetten-Interfaces sind zusammen auf einer Leiterplatte aufgebaut, die häufig als „FSK-Modem“ (FSK-Modulator/Demodulator) bezeichnet wird. Das Modem selbst ist eine Zusatzplatine der programmierbaren Serienschnittstelle. Beide Einheiten zusammen bilden das Kassetten-Interface.

Serieller Datensender und -empfänger werden durch den Schnittstellenbaustein 8251 gebildet (Bild 4). Die Bezeichnung „UART“ ist eine Abkürzung der Begriffe Universal Synchronous/ Asynchronous Receiver/Transmitter“. Dies bedeutet „Universaller synchroner /asynchroner Empfänger und Sender“ (engl. „Receiver“ = Empfänger, „Transmitter“ = Sender).

Darüber hinaus enthält die programmierbare Serienschnittstelle einen Adressvergleicher und einen Baudratenteiler. Vor der Behandlung dieser Schaltungsteile wird zunächst die Wirkungsweise der Serienschnittstelle anhand des Blockschaltbildes kurz erklärt.

Die Datenanschlüsse des 8251 sind mit den Datenleitungen 00 bis 07 des Systembusses verbunden (Bild 4). Sie führen über den Datenbus-Puffer zum internen Datenbus des Bausteins, an den insgesamt fünf Register mit folgenden Funktionen angeschlossen sind:

Das Betriebsarten- und das Kommandoregister bestimmen gemeinsam die Funktion des seriellen Schnittstellenbausteins. Durch 11Programmierung11 , womit das Einschreiben bestimmter Steuerworte in diese Register gemeint ist, wird die Betriebsart festgelegt.

Bild 4: Blockschaltbild der Baugruppe Kassetten-Interface

Diese „Initialisierung“ der seriellen Schnittstelle zum Betrieb als Kassetten-Interface erfolgt durch das Betriebssystem MAT 85 automatisch beim Einschalten des Gerätes. Das Senderregister gehört zum seriellen Datensender und erhält die seriell auszugebenden Daten in paralleler Form über den Datenbus-Puffer und den internen Datenbus. Innerhalb des Datensenders werden Start- und Stopbits in den Datenstrom eingefügt, der am Anschluß „TxD“ (Transmitter-Data) seriell als eine Folge von H/L-Signalen ausgegeben wird. Der Datensender führt die erforderliche Parallel-/Seriell-Wandlung mit Hilfe des vom Baudratenteiler stammenden Sendertaktes „TxC“ (Transmitter-Cl ock) durch. Die Ausgangsspannung des Modulators ist sinusförmig.

Das Empfängerregister kann am Anschluss „RxD“ (Receiver-Data) einen seriellen Datenstrom empfangen. Er stammt vom Demodulator, der aus den Signalen des Kassetten- Recorders in Abhängigkeit der Frequenz H- oder L-Pegel erzeugt. Innerhalb des Datenempfängers findet die Seriell-/Parallel-Wandlung der empfangenen Daten statt, wobei alle zusätzlichen Bits (z.B. Start- und Stoppbits) aus dem empfangenen Signal entfernt werden. Vom Baudratenteiler erhält die Empfängersteuerung den Empfängertakt „RxC“ (Receiver-Clock), der gl ei eh dem Sendertakt ist.

Das Statusregister (Status = Zustand) erhält sowohl vom seriellen Datensender als auch vom seriellen Datenempfänger Informationen über den Zustand dieser Einheiten. Beispiele hierfür sind Meldungen wie „Senderregister leer“ und „Empfängerregister hat Zeichen empfangen“. Der Prozessor kann das Statusregister lesen und erkennt hierdurch, ob er ein neues Zeichen zur seriellen Ausgabe an die Baugruppe ausgeben kann oder ob ein seriell empfangenes Zeichen vorliegt und eingelesen werden muss.

Die Auswahl der einzelnen Register beim Datenverkehr mit der CPU erfolgt mit Hilfe der Bausteinanschlüsse „C/D“, „WR“ und „RD“, auf die später noch eingegangen wird.

Damit der serielle Schnittstellenbaustein Daten vom Prozessor erhalten oder an ihn abgeben kann, muss der Anschluss „CS“ (Chip-Select) über die Leitung „Bausteinfreigabe“ L-Signal erhalten (Bild 4). Es stammt vom „Adressvergleicher“ und wird nur abgegeben, wenn die Baugruppe vom Prozessor „angesprochen“ wird, d.h., wenn die Bitkombination der Adresseitungen A4 bis A7 gleich ist mit der Bitkombination, die mit den Schaltern S1 bis S4 eingestellt wurde (Baugruppennummer).

Zur zeitlichen Steuerung der internen Vorgänge besitzt der Baustein 8251 die drei Taktanschlüsse „RxC“, „TxC“ und „CLK“ (Bild 4). „RxC“ und „TxC“ bestimmen die sender- bzw. empfängerseitige Datenübertragungsrate (Baudrate). Hierzu wird der 2-MHz-Systemtakt einem Baudratenteiler zugeführt, der Baudraten von 1200 Bd, 600 Bd, 300 Bd und 150 Bd ermöglicht.

An „CLK“ ist ein Taktsignal erforderlich, dessen Frequenz wesentlich höher ist als die höchste Ausgangsfrequenz des Baudratenteilers. Hierzu eignet sich der 2-MHz-Systemtakt, der durch IC2.3 invertiert auf den CLK-Anschluss geführt wird. Diese Invertierung soll das CLK-Signal lediglich auffrischen. IC2.2 invertiert das L-aktive Reset-Signal des Systembusses, da der Schnittstellenbaustein 8251 einen H-aktiven Reset-Eingang besitzt. Nach jedem Reset muss der Baustein neu programmiert werden. Dies geschieht selbständig durch das Betriebssystem.

Steuerregister und Datenregister

Vergleicht man die Register des Bausteins 8251 miteinander, so kann zwischen „Steuerregistern“ (engl. „Control-Register“) und „Datenregistern“ unterschieden werden. In einige der Register kann der Prozessor Daten einschreiben, andere dagegen nur lesen. Bild 5 zeigt die Aufteilung der Register in diese Gruppen und die erforderlichen Steuersignale zu ihrer Ansteuerung.

Bild 5: Aufteilung der Register in Gruppen

Zur Unterscheidung der Gruppen „Control-“ und „Datenregister“ dient der Bausteinanschluss C/D: Führt C/D H-Pegel, sind die Control-Register, bei L-Pegel die Datenregister ausgewählt. Aus Bild 5 geht ebenfalls hervor, welche Register vom Prozessor gelesen und welche mit Daten beschrieben werden können: Status- und Empfängerregister können nur gelesen, Betriebsarten-, Kommando und

Senderregister nur beschrieben werden.

Mit Hilfe der L-aktiven Steuerleitung „IOW“ , die mit dem Bausteinanschluss „WR“ verbunden ist, schreibt der Prozessor Datenwerte in den Baustein ein. Zur Unterscheidung, ob bei einem Schreibvorgang das Senderregister (mit den seriell auszugebenden Daten) oder das Betriebsarten- bzw. Kommandoregister (mit Steuerworten) beschrieben wird, dient der Bausteinanschluss C/D (Control/Data), der mit der Adressleitung AO verbunden ist. Bei L-Signal an C/D (entspricht „Data“) gelangen die vom Prozessor ausgegebenen Datenworte in das Senderregister. Liegt bei einem Schreibvorgang am Anschluss C/D jedoch H-Pegel vor (entspricht „Control“), wird entweder das Betriebsarten- oder das Kommandoregister mit einem Steuerwort beschrieben. Diesen Vorgang nennt man „Initialisieren“ des

Schnittstellenbausteins.

Bedingt durch die Vielzahl der Programmiermöglichkeiten besitzt der 8251 nicht nur ein, sondern zwei Register zur Betriebsartenprogrammierung. Die Unterscheidung, ob das ausgegebene Steuerwort in das Betriebsartenregister oder in das Kommandoregister gelangt, erfolgt nicht durch die Schaltung, sondern durch folgende Festlegung: Nach einem Kaltstart des Mikrocomputers (Einschalten oder „Reset“) wird das erste Initialisierungsbyte stets in das Betriebsartenregister geschrieben. Das zweite Steuerbyte gelangt in das Kommandoregister. Beide Register werden dabei unter der gleichen Adresse angesprochen. Die Programmierung des Schnittstellenbausteins für den Betrieb als Kassetten-Interface ist in einem eigenen Kapitel beschrieben.

Mit Hilfe der L-aktiven Steuerleitung „IOR“, die mit dem Bausteinanschluss „RD“ verbunden ist, löst der Prozessor das Lesen von Daten aus dem Schnittstellenbaustein aus (Bild 5). Der Signalzustand des Anschlusses C/Ö bestimmt dabei, welches Register gelesen wird: Bei H-Pegel an C/D (entspricht „Control“) gelangt der Inhalt des Statusregisters auf den Datenbus, bei L-Pegel (entspricht „Data“) der des Empfängerregisters.

Der Adressvergleicher und die Baugruppennummer

Der Mikroprozessor steuert die Baugruppe „Kassetten-Interface“ wie jede andere Ein- und Ausgabe-Einheit an. Da immer nur eine einzige Einheit aktiviert sein darf, müssen a 11 e im System vorhandenen Ein- und Ausgabe-Einheiten unterschiedliche Baugruppennummern besitzen. Aus diesem Grund ist die Baugruppennummer der Baugruppe „Kassetten-Interface“ mit Hilfe von Schaltern einstellbar. Ein Adressvergleicher übernimmt die Aufgabe, die Baugruppe nur dann zu aktivieren, wenn der Prozessor diejenige Adresse aussendet, die der eingestellten Baugruppennummer entspricht. Bild 6 zeigt die Schaltung des Adressvergleichers.

Bild 6: Baugruppenadresse, Bausteinfreigabe

Nur wenn die Bitkombination auf den Adressleitungen A4 bis A7 der mit den Schaltern Sl bis S4 eingestellten Bitkombination entspricht, gibt der 4-BitVergleicher IC1 an seinem Ausgang 11A=B 11 ein H-Signal ab (Bild 6). Da der serielle Schnittstellenbaustein 8251 (IC3) zur Aktivierung jedoch ein L-Signal benötigt, wird das Ausgangssignal von IC1 durch IC2.1 invertiert. Die Baugruppe kann nun Daten empfangen oder an den Prozessor abgeben. Der Prozessor gibt stets eine vollständige 8-Bit-Adresse an A0 bis A7 aus, wenn er eine Ein- oder Ausgabe-Einheit anspricht. Beim hier vorgenommenen Adressvergleich werden jedoch die Adressleitungen A0 bis A3 nicht berücksichtigt. Aus diesem Grund steht nicht der volle Adressbereich von 00H bis FFH mit 256 verschiedenen Adresswerten zur Verfügung, sondern mit den Schaltern S1 bis S4 können lediglich 16 verschiedene Signalzustände (Bausteinadressen) eingestellt werden. Da diese Schalter den vier höherwertigen Adress-Bits A4 bis A7 zugeordnet sind, kann die Baugruppennummer nur die hexadezimalen Werte von 0X bis FX annehmen. „X“ steht hier für die vier niederwertigen Adress-Bits A0 bis A3, die beim Adressvergleich nicht benutzt werden. Die Tabelle in Bild 7 zeigt die Bildung der möglichen Baugruppennummern.

Bild 7 : Bildung der Baugruppennummern der Baugruppe „Kassetten-lnterface“

Im fachpraktischen Teil dieser Übung werden die Adressschalter bei der Inbetriebnahme

der Baugruppe folgendermaßen eingestellt:

| S4 (A7) | S3 (A6) | S2 (A5) | A1 (A4) |

| OFF | OFF | OFF | OFF |

| 1 | 1 | 1 | 1 |

Hierdurch ergibt sich die Baugruppennummer „FX“. Prinzipiell kann jede der 16 möglichen Baugruppennummern verwendet werden. Es ist aber darauf zu achten, dass sämtliche Ein- oder Ausgabe-Baugruppen eines Mikrocomputer-Systems unterschiedliche Adressen besitzen, da es anderenfalls zu Schäden am Gerät kommen kann.

Adressierung und Schreib-/Lesesteuerung

Die folgende Tabelle (Bild 8) zeigt die Zusammenhänge der Adressierung und der Schreib-/Lesesteuerung bei der Baugruppe „Kassetten-Interface“. Dabei wird von der Baugruppennummer „FXH“ ausgegangen.

Bild 8: Adressierung und Schreib-/Lesesteuerung

Die Adressleitungen A4 bis A7 besitzen die in Bild 8 angegebenen Signalzustände, die der Baugruppennummer „FXH“ entsprechen. Der serielle Schnittstellenbaustein 8251 erhält am Anschluss CS L-Pegel und ist freigegeben. Da die Adressleitungen A1 bis A3 nicht angeschlossen sind, kann ihr logischer Pegel 11111 oder 11011 sein. Dies wird in der Tabelle durch die Bezeichnung „X“ ausgedrückt.

Zum Betriebszustand 2 (Bild 8):

Der Prozessor steuert die Schreibleitung „IOW“ auf L-Pegel. In diesem Betriebszustand schreibt er Daten in die Baugruppe. Da die Adressleitung A0 (bzw. der Anschluss C/D) L-Pegel aufweist, werden die Daten in das Senderregister geschrieben (siehe auch Bild 5). Wegen der nicht benutzten Adressleitungen A1 bis A3 kann das Senderregister unter folgenden Adressen angesprochen werden: F0H, F2H, F4H, F6H, F8H, FAH, FCH und FEH. Diese Mehrfachadressierung ist durch die einfache Schaltung bedingt, die nicht alle Adressleitungen zur Adressbildung verwendet. Von den acht Adressmöglichkeiten wird in dieser Übung der Wert „F0H“ verwendet, um Daten an das Senderregister auszugeben.

Zum Betriebszustand 3 (Bild 8):

Die Schreibleitung „IOW“ führt weiterhin L-Pegel, aber die Adressleitung A0 hat H-Pegel. Da bei H-Pegel an A0 eines der Control-Register angesprochen wird, gelangen die Prozessordaten jetzt als Steuerworte in das Betriebsarten- oder das Kommandoregister (Bild 5). Die Initialisierung der seriellen Schnittstelle kann unter folgenden Adressen erfolgen: F1H, F3H, F5H, F7H, F9H, FBH, FDH und FFH. In dieser Übung wird davon der Wert „F1H“ verwendet.

Beachtet werden muss, dass beide Control-Register Steuerworte erhalten müssen, bevor der Baustein betriebsbereit ist. Hierbei ist festgelegt, dass zuerst das Betriebsarten- und danach das Kommandoregister beschrieben wird. Da die erforderliche Initialisierung durch das Betriebssystem MAT 85 erfolgt, braucht hierauf nicht weiter eingegangen zu werden.

Zum Betriebszustand 4 (Bild 8):

„IOW“ liegt wieder auf H-Pegel, aber die Leseleitung „IOR“ führt L-Pegel. Da die Adressleitung A0 ebenfalls L-Pegel besitzt, werden in diesem Fall vom Prozessor die Daten des Empfängerregisters gelesen {siehe auch Bild 5). Das Lesen der Daten ist unter den gleichen Adressen wie im Betriebszustand 2 möglich und erfolgt in dieser Übung unter der Adresse „F0H“

Zum Betriebszustand 5 (Bild 8):

„IOR“ führt weiterhin L-Pegel, aber A0 hat H-Pegel angenommen. In diesem Betriebszustand wird vom Prozessor das Statusregister des Schnittstellenbausteins gelesen. Dies kann wieder unter 8 verschiedenen Adressen erfolgen (wie im Betriebszustand 3). In dieser Übung wird davon der Wert „F1H“ verwendet. „IOW“ und „IOR“ haben nie zusammen L-Pegel. Liegt eine andere Adresse als die gewählte Baugruppennummer vor, ist das 11Kassetten-Interface11 nicht aktiv (wie im Betriebszustand 1).

Der Baudratenteiler

Das an den Anschlüssen RxC und TxC des Schnittstellenbausteins angeschlossene TTL-Rechtecksignal bestimmt durch seine Frequenz die Datenübertragungsrate ( Baudrate ) der seriellen Datenübertragung. Für vier unterschiedliche Baudraten werden die erforderlichen Taktfrequenzen aus dem 2-MHz-Systemtakt gewonnen. Hierzu dienen mehrere Frequenzteilerstufen. Bild 9 zeigt den Aufbau des Baudratenteilers und gibt die möglichen Ausgangsfrequenzen an.

Bild 9: Aufbau des Baudratenteilers

Der Baudratenteiler besteht aus einem 13:1-Frequenzteiler und vier nachgeschalteten 2 :1-Teilerstufen (Bild 9). Angesteuert wird er durch den von IC2.3 11aufgefrischten11 2-MHz-Systemtakt. An den vier Ausgängen A, B, C und D treten die angegebenen Frequenzwerte auf. Jeweils eines dieser Signale wird durch eine Lötbrücke auf die miteinander verbundenen Takteingänge RxC und TxC des seriellen Schnittstellenbausteins geschaltet. Beachtet werden muss, dass immer nur eine einzige Lötbrücke vorhanden sein darf.

Innerhalb des Schnittstellenbausteins befinden sich hinter den Takteingängen RxC und TxC zusätzliche Frequenzteilerstufen (in Bild 4 nicht eingezeichnet), deren Teilungsraten durch die Initialisierung auf die Werte 1:1, 16:1 und 64:1 programmierbar sind. Beim Einsatz als Kassetten-Interface wird durch das Betriebssystem MAT 85 ein Teilerverhältnis von 64:1 programmiert. Hieraus ergeben sich die in Bild 10 aufgeführten möglichen Baudraten des Kassetten-Interfaces.

| Lötbrücke | Frequenz an RxC und TxC | Baudrate Teilerverhältnis 16 : 1 | Teilerverhältnis 64 : 1 |

|---|---|---|---|

| A | ca. 77 kHz | 4800 Bd | 1200 Bd |

| B | ca. 38,5 kHz | 2400 Bd | 600 Bd |

| C | ca. 19,2 kHz | 1200 Bd | 300 Bd |

| D | ca. 9,6 kHz | 600 Bd | 150 Bd |

Bild 10: Mögliche Baudraten des Kassetten-lnterfaces

Der Modulator des Kassetten-Interfaces

Bild 11 zeigt den Blockaufbau des Modulators. Er besteht aus den Funktionseinheiten „Frequenzumtastung“, „Dreickgenerator“ und „Dreieck/ Sinus-Wandler“. Der Modulator arbeitet nach folgendem Prinzip: Die Frequenz des Dreieckgenerators wird durch die seriellen Daten zwischen 2400 Hz und 3600 Hz umgetastet. Hierzu dient der Block „Frequenzumtastung“. Dem Dreieckgenerator nachgeschaltet ist ein Dreieck/Sinus-Wandler, der die Ausgangsspannung des Modulators in eine annähernde Sinusform bringt. Diese kann von einem Kassetten-Recorder gut auf genommen werden.

Bild 11: Blockaufbau des Modulators

Der Dreieckgenerator

Der Dreieckgenerator des Modulators von Bild 11 ist nach einer Grundschaltung aufgebaut, die mit Operationsverstärkern arbeitet und aus einem Integrator mit nachgeschaltetem Komparator besteht. Bild 12 zeigt diese Grundschaltung und Bild 13 die zugehörigen Diagramme.

Bild 12: Dreieckgenerator mit Operationsverstärkern

Bild 13: Diagramme des Dreieckgenerators mit OPV

Die rechteckförmige Ausgangsspannung u2 des Komparators ist gleichzeitig die Eingangsspannung für den Integrator (Bild 12 und Bild 13). Sie beträgt entweder -UB oder +UB. Die Ausgangsspannung des Integrators ist Eingangsspannung für den Komparator. Sie besitzt einen dreieckförmigen Verlauf.

Es wird angenommen, dass der Kondensator C zum Zeitpunkt t0 entladen ist und am Komparatorausgang zunächst -UB ansteht. Der Kondensator C wird dann über R1 mit einem konstanten Strom, der sich aus u2/R1 ergibt, geladen. Als Folge davon steigt u1, vom Zeitpunkt t0 beginnend, linear an. Da u2 momentan negativ ist und der Operationsverstärker Al am invertierenden Eingang angesteuert wird, nimmt u1 zunächst positive Werte an.

Sobald u1 zum Zeitpunkt t1 die positive Schaltschwelle des Komparators erreicht hat, wechselt u2 von -UB auf +UB. Hierdurch wird der Kondensator zunächst entladen und anschließend mit umgekehrter Polarität wieder aufgeladen. Als Folge davon verringert sich u1 linear und nimmt schließlich auch negative

Werte an, bis zum Zeitpunkt t2 die negative Schaltschwelle des Komparators erreicht ist. Nun beginnt der Vorgang von vorn, der Generator schwingt periodisch.

Die Frequenz dieser Schaltung, die je nach verwendetem Ausgang als Rechteck- oder Dreieckgenerator bezeichnet werden kann, ist in erster Linie von R1 und C bestimmt. Auch die Schaltschwellen des Komparators besitzen einen gewissen Einfluss auf die Frequenz.

Anstelle von Operationsverstärkern werden in dieser Übung CMOS-Inverter eingesetzt, die eigentlich für digitale Anwendungen vorgesehen sind. Unter bestimmten Bedingungen können einige CMOS-Schaltkreise jedoch auch linear betrieben und somit für analoge Zwecke eingesetzt werden. Hierdurch ergibt sich gegenüber der Verwendung von Operationsverstärkern der Vorteil, dass nur eine Versorgungsspannung (+5 V) benötigt wird, wodurch das Zusammenwirken mit digitalen Schaltungsteilen ohne Pegelanpassung möglich ist. Bild 14 zeigt den Aufbau des Generators mit Hilfe von CMOS-Invertern.

Bild 14: Dreieckgenerator mit CMOS-Invertern

Der mit CMOS-Invertern aufgebaute Generator gleicht weitgehend der Operationsverstärker-Schaltung von Bild 12. Vergleichen Sie beide Schaltungen miteinander! Da der Integrator invertierendes Verhalten besitzt, ist hierfür der Inverter IC11.3 direkt geeignet. Zur Bildung des Komparators mit nichtinvertierendem Verhalten sind zwei hintereinandergeschaltete Inverter (IC11.2 und IC11.1) erforderlich. Mit R11 kann die Generatorfrequenz eingestellt werden. Der Verlauf der Ausgangsspannungen u1 und u2 des Integrators bzw. Komparators ist in Bild 15 dargestellt. Beide Spannungen nehmen nur Werte zwischen 0V und 5 V an, da die Schaltung ohne negative Betriebsspannung arbeitet.

Bild 15: Diagramme des Dreieckgenerators mit CMOS-Invertern

Die Frequenzumtastung des Dreieckgenerators

Der Dreieckgenerator erhält vom Anschluß „TxD“ der programmierbaren Serienschnittstelle eine Folge von 1/0-Signalen, welche die Frequenz des Generators zwischen 2400 Hz (bei L-Pegel) und 3600 Hz (bei H-Pegel) umschaltet. Zur Frequenzumschaltun g bzw. Frequenzumtastung dienen „Exklusiv-Oder-Verknüpfungen“ (EXOR-Glieder), die auch als „Antivalenzstufen“ bezeichnet werden. Bild 16 zeigt das Schaltsymbol eines EXOR-Gliedes und die dazugehörige Wertetabelle

Bild 16: EXOR-Schaltkreis (Antivalenz)

Ein EXOR-Schaltkreis nach Bild 16 führt am Ausgang A nur dann H-Pegel, wenn einer der beiden Eingänge (E1 oder E2) H-Pegel besitzt. Zur Frequenzumtastung des Dreickgenerators werden zwei EXOR-Stufen mit unterschiedlichen Aufgaben eingesetzt. Bild 17 zeigt die Schaltung hierzu.

Bild 17: Dreieckgenerator mit Frequenzumtastung

Der Modulatoreingang „T“ erhält vom Senderausgang „TxD“ der programmierbaren Serienschnittstelle entweder H- oder L-Signal (Bild 17). R10 dient als Vorwiderstand für die Dioden D10 und D11, die das Datensignal auf TTL-Pegel begrenzen. Obwohl diese Maßnahme im BFZ/MFA-Computer eigentlich nicht erforderlich ist, wurde die Pegelbegrenzung für andere Anwendungsfälle der Modem-Zusatzplatine vorgesehen.

Das Datensignal gelangt zum Eingang E1 der EXOR-Stufe IC10.1 (Bild 17). Der Eingang E2 kann über die Lötbrücken BR1 oder BR2 entweder mit 0V (L-Pegel) oder +5V (H-Pegel) verbunden werden. Hierdurch arbeitet IC10.1 entweder als Inverter (BR1 geschlossen) oder als nichtinvertierende Durchgangsstufe (BR2 geschlossen). Die folgende Funktionstabelle (Bild 18) zeigt diese beiden Fälle.

Bild 18: Wirkung von 1(10.1)

In den beiden oberen Zeilen von Bild 18 führt E2 L-Pegel. Dieser Zustand liegt vor, wenn BR2 geschlossen ist. Das Signal an „T“ bzw. E1 tritt hierbei unverändert am Ausgang A1 auf, also arbeitet die Stufe jetzt nichtinvertierend. Wird die Brücke BR1 geschlossen, führt E2 von IC10.1 H-Pegel. Dieser Zustand entspricht den beiden unteren Zeilen von Bild 18, bei denen IC10.1 das Signal von „T“ bzw. E1 am Ausgang A1 invertiert abgibt.

Ohne die Schaltung zu verändern, kann das Datensignal somit entweder nichtinvertiert oder invertiert auf den Eingang E4 der zweiten EXOR-Stufe gegeben werden. Im BFZ/MFA-Computer ist zur Erzielung der richtigen Frequenzlage (H-Signal entspricht der höheren Frequenz, L-Signal der niedrigeren) die Brücke BR1 geschlossen, wodurch IC10.1 als Inverter arbeitet. Andere Anwendungen des Kassetten-Interfaces erfordern eventuell ein nichtinvertiertes Datensignal.

Die Frequenzumschaltung des Generators erfolgt durch die EXOR-Stufe IC10.2 und die Widerstände R14/R15, die zur Erzielung einer höheren Schwingfrequenz parallel zu R11/R12 geschaltet werden (Bild 17). Hierzu dient IC10.2. Bild 19 zeigt dies im einzelnen.

Bild 19: Frequenzumtastung, Wirkung von 1(10.2)

Der Dateneingang 11T11 von Bild 17 soll H-Pegel führen. Hierdurch besitzt E4 von IC10.2 L-Pegel, weil ICl0.1 als Inverter arbeitet.

Der Eingang E3 von IC10.2 ist an die Rechteckspannung u2 angeschlossen, die abwechselnd L- und H-Signal annimmt. Der Wertetabelle in Bild 19 ist zu entnehmen, dass bei L-Pegel an E4 der Ausgang A2 stets das gleiche Signal wie der Eingang E3 führt. Dies entspricht in seiner Wirkung einer Verbindung zwischen E3 und A2, wodurch R14/R15 und R11l/R12 parallelgeschaltet sind. Hierdurch erhält C1O einen erhöhten Lade- und Entladestrom. Dies führt zu einer schnelleren Kondensatorladung und damit zu einer höheren Frequenz.

Sind die Widerstandszweige nicht parallel geschaltet, wird der Ladestrom für C10 nur durch R11/R12 bestimmt. Hierdurch ergibt sich ein geringerer Lade- und Entladestrom und somit eine niedrigere Schwingfrequenz des Oszillators. Dieser Fall tritt immer dann ein, wenn E4 H-Pegel besitzt, wozu das Eingangssignal an „T“ L-Pegel führen muss. Aus der Wertetabelle von Bild 19 kann entnommen werden, dass bei H-Signal an E4 die Signale E3 und A2 invers zueinander sind, wodurch die Parallelschaltung von R14/R15 und R11/R12 aufgehoben ist.

Der Dreieck/Sinus-Wandler

Normale Kassettenrecorder sind für die Verarbeitung von Sprache und Musik ausgelegt und können daher Sinussignale gut verarbeiten. Die Aufzeichnung von Rechteck- oder Dreiecksignalen ist dagegen nur unvollkommen möglich. Der in Bild 11 dargestellte Dreieck/Sinus-Wandler dient dazu, aus der Dreieckspannung des Generators eine Sinusspannung zu erzeugen. Hierzu wird das nicht ganz lineare 0bertragungsverhalten eines diskret aufgebauten Differenzverstärkers ausgenutzt. Bild 20 zeigt die Schaltung des mit PNP-Transistoren arbeitenden Wandlers.

Bild 20: Dreieck/Sinus-Wandler

Die Dreieckspannung u1 wird über R20 und R22 auf die Basisanschlüsse der Transistoren geführt (Bild 20). R19 ist der gemeinsame Emitterwiderstand des Differenzverstärkers. R20 und C11 bilden einen Tiefpass mit sehr niedriger Grenzfrequenz (etwa 1,6 Hz). Da die Dreieckspannung eine wesentlich höhere Frequenz besitzt, arbeitet der Tiefpass als Integrator und bildet den Mittelwert der Dreieckspannung. T10 wird daher mit einer konstanten Gleichspannung angesteuert. Sie dient zur Arbeitspunkteinstellung beider Transistoren, da auch die Basis von T11 diese Gleichspannung erhält (über R21).

Die Basisspannung von T11 wird über R22 mit der Dreieckspannung u1 überlagert. Bedingt durch die Schaltungsdimensionierung, die Nichtlinearitäten der Transistor-Eingangskennlinien und die Gegenkopplung über R19 wird die Dreieckspannung durch den Differenzverstärker so verändert, dass am Arbeitswiderstand (R23) eine Spannung mit annähernd Sinusform auftritt. C12 wirkt als Koppelkondensator und trennt den Gleichspannungsanteil der Ausgangsspannung ab, so dass am Widerstand R24 eine sinusförmige Wechselspannung auftritt, die von einem Kassetten-Recorder aufgenommen werden kann. Bild 21 zeigt die Ein- und Ausgangsspannung des Dreieck/Sinus-Wandlers.

Bild 21: Ein- und Ausgangsspannung des Dreieck/Sinus-Wandlers

Die Demodulatoreinheit des Kassetten-Interfaces

Zur Demodulatoreinheit des Kassetten-Interfaces gehört eine NF-Signalaufbereitung und ein FSK-Demodulator, der die verschiedenen Tonfrequenzen wieder in H- oder L-Pegel umsetzt. Bild 22 zeigt den Blockaufbau der Demodulatoreinheit.

Bild 22: Blockaufbau der Demodulatoreinheit

Vor der Behandlung von Schaltungseinzelheiten wird zunächst die grundsätzliche Funktion der in Bild 22 dargestellten Demodulatoreinheit erklärt. Hierzu dienen die Diagramme in Bild 23.

Bild 23: Wirkungsprinzip der Demodulatoreinheit

Bei der Widergabe gespeicherter Daten liefert ein Kassetten-Recorder sinusförmige NF-Signale, deren Frequenz entweder 2400 Hz oder 3600 Hz beträgt. Der Spitze-Spitze-Wert dieser im Diagramm Uin von Bild 23 dargestellten Spannung liegt im Bereich von etwa 100 mV bis 500 mV.

Aus den Frequenzen des NF-Signals bildet ein FSK-Demodulator wieder H- und L-Pegel. Hierzu wird das NF-Signal zunächst aufbereitet, womit die Umwandlung der Eingangsspannung Uin in Rechtecksignale mit TTL-Pegel gemeint ist. Dies geschieht im Block „NF-Signalaufbereitung“ von Bild 22. Das Ausgangssignal der NF-Aufbereitung ist im Diagramm Unf von Bild 23 dargestellt. Es nimmt für die Dauer der negativen Halbperiode der Sinus-Eingangsspannung H-Pegel an.

Das aufbereitete NF-Signal Unf gelangt zur Impulsstufe von Bild 22, deren Ausgangssignal im Diagramm Uimp von Bild 23 dargestellt ist. Die Impulsstufe gibt sowohl bei der ansteigenden als auch bei der abfallenden Flanke der Spannung Unf einen Impuls ab, dessen Impulsdauer ti konstant ist und etwa 1/4 der Periodendauer der höchsten vorkommenden Frequenz beträgt.

Der nachgeschaltete Tiefpass bildet durch Integration den Mittelwert Um der auftretenden Impulse. Da vor dem Zeitpunkt t1 eine niedrigere Eingangsfrequenz vorliegt als nachher, treten die Impulse der Impulsstufe vor t1 mit größeren Abständen auf als nach t1. Hierdurch ergibt sich bei einer Eingangsfrequenz von 2400 Hz mit etwa 1,7 V ein geringerer Mittelwert der Impulsspannug als bei 3600 Hz. Bei dieser Frequenz beträgt der Mittelwert der Impulsspannung etwa 2,5 V.

Diese Spannungswerte werden von dem nachgeschalteten Komparator, der eine Schaltschwelle von etwa 2,2 V besitzt, unterschieden und in H- und L-Signale umgesetzt. Die Folge der H- und L-Signale entspricht dem seriellen Datenstrom. Im Diagramm Uimp von Bild 23 ist neben der Impulsspannung auch der Mittelwert der Impulse Um und die Schaltschwelle Us des Komparators eingezeichnet. Das Diagramm DATA zeigt das Umschalten des Komparators zum Zeitpunkt t2, wenn die Schaltschwelle Us des Komparators vom Mittelwert Um der Impulsspannung überschritten wird.

In den nächsten Abschnitten werden die verschiedenen Schaltungsteile der Demodulatoreinheit

erklärt.

Die NF-Signalaufbereitung

Bild 24 zeigt den Schaltungsauszug der NF-Signalaufbereitung, die mit insgesamt vier Operationsverstärkern aufgebaut ist. Zwei davon verarbeiten das NF-Signal, die beiden anderen OPVs übernehmen Hilfsfunktionen.

Die vom Kassetten-Recorder stammende NF-Spannung gelangt über R25 auf den Trimmerwiderstand R26, mit dessen Hilfe die Eingangsempfindlichkeit der Schaltung eingestellt werden kann. Bei voller Empfindlichkeit reichen etwa 30 mV (Spitze-Spitze) zur Ansteuerung der Schaltung aus. Die tatsächliche Eingangsspannung sollte jedoch mehr als 100 mV (Spitze-Spitze) betragen, damit das Kassetten-Interface auch bei geringen Pegelschwankungen ohne Aussetzer arbeitet. Zu große Eingangsspannungspegel werden durch die Dioden D12 und D13 begrenzt.

Bild 24: Schaltung der NF-Signalaufbereitung

IC12.1 arbeitet als nichtinvertierender NF-Verstärker mit Bandpaßverhalten. Die Kondensatoren C13, C14 und C16 legen den Arbeitsbereich des Verstärkers für den Frequenzbereich von etwa 1,5 kHz bis 6 kHz fest.

Da nur eine Betriebsspannung von 5 V zur Verfügung steht, IC12.1 jedoch eine Wechselspannung verstärken muss, wird der Arbeitspunkt dieses OPV etwa in die Mitte des Aussteuerungsbereiches zwischen 0V und 5V verschoben. Hierzu erhält der nichtinvertierende Eingang von IC12.1 über R27 eine Spannung in Höhe von +2 V zugeführt. Sie wird durch den Spannungsteiler R29 bis R31 erzeugt und von dem als Impedanzwandler geschalteten OPV IC12.2 niederohmig abgegeben. Da diese Spannung auch als Vergleichsspannung für den Schmitt-Trigger IC13.1 dient, wird sie mit „Uv1“ bezeichnet.

Das von IC12.1 verstärkte NF-Signal gelangt über R33 auf den invertierenden Eingang von IC13.1. Über R34 erhält der andere Eingang dieses ICs die Spannung Uv1, welche die Schaltschwelle des Schmitt-Triggers bildet.

Überschreitet die verstärkte NF-Spannung die Vergleichsspannung Uv1, so schaltet der Ausgang von IC13.1 auf L-Pegel. Unterhalb der Schaltschwelle führt IC13.1 H-Pegel am Ausgang. Der Mitkoppelwiderstand R36 bewirkt eine Schalthysterese. Das Ausgangssignal des Schmitt-Triggers besitzt einen rechteckförmigen Verlauf. Es ist im Diagramm Unf von Bild 23 dargestellt.

IC12.1 von Bild 24 dient zu Erkennung eines ausreichenden NF-Pegels, daher wird dieser Schaltungsteil als „NF-Pegeldetektor“ bezeichnet. Der nichtinvertierende Eingang von IC12.1 erhält die verstärkte NF-Spannung und der invertierende Eingang die Vergleichsspannung Uv2. Sie wird ebenfalls vom Spannungsteiler R29 bis R31 gebildet. Die Höhe dieser Vergleichsspannung ist so gewählt, dass IC12.3 ab einer Eingangsspannung von etwa 100 mV (Spitze-Spitze) durch das NF-Signal periodisch durchgeschaltet wird, wodurch die grüne Leuchtdiode „LEVEL“ aufleuchtet. Hierdurch wird ein ausreichender NF-Eingangspegel signalisiert.

Die Impulsstufe

Nach der NF-Signalaufbereitung folgt im Blockschaltbild der Demodulatoreinheit eine Impulsstufe (Bild 22). Ihre Aufgabe ist es, bei der ansteigenden und der abfallenden Flanke des Signals Unf einen Impuls konstanter Länge abzugeben. Dies wurde bereits im Bild 23 dargestellt. Zur Impulserzeugung dient der in Bild 25 gezeigte Aufbau. Er besteht aus einer Impuls-Verzögerungsstufe und einem EX0R-Schaltkreis zur Signalverknüpfung.

Bild 25: Prinzipaufbau der Impulsstufe

Das aufbereitete NF-Signal Unf durchläuft eine Impuls-Verzögerungsstufe und wird um etwa 100 μs zeitverzögert auf den oberen Eingang der EX0R-Stufe IC10.4 gegeben (Bild 25). Der zweite Eingang der EXOR-Stufe erhält Unf direkt zugeführt. Als Folge der Signalverknüpfung tritt am Ausgang von ICl0.4 die Impulsspannung Uimp auf. Bild 26 zeigt die Diagramme der Impulsstufe für die beiden NF-Frequenzen von 2400 Hz und 3600 Hz.

Bild 26: Wirkungsweise der Impulsstufe

Zum Zeitpunkt tl wechselt das Signal Unf von L- auf H-Pegel und geht zum Zeitpunkt t3 wieder auf L-Pegel zurück (Bild 26). Die Spannung Uv nimmt, da sie gegenüber Unf um die Zeit tv verzögert ist, zum Zeitpunkt t2 H-Pegel und zum Zeitpunkt t4 wieder L-Pegel an. Die Signale Unf und Uv werden miteinander EXOR-verknüpft. Das Ergebnis dieser Verknüpfung ist im Diagramm Uimp dargestellt.

In den Zeitabschnitten von t1 bis t2 und t3 bis t4 sind die logischen Pegel von Unf und Uv ungleich, zwischen t2 und t3 sowie t4 und t5 jedoch gleich. Bei ungleichen Eingangssignalen führt eine EX0R-Stufe am Ausgang H-Pegel, bei gleichen Signalen dagegen L-Pegel (siehe auch Bild 16). Hierdurch ergibt sich der Ausgangsspannungsverl auf Uimp von Bi 1 d 26: Am Ausgang der Impulsstufe tritt während der Zeitabschnitte, bei denen Unf und Uv ungleich sind, H-Pegel auf. Die Ausgangsimpulse besitzen die Dauer ti, die der Verzögerungszeit tv entspricht.

Für die Funktion der Impulsstufe ist nicht die Dauer der Ausgangsimpulse von Bedeutung, sondern ihre zeitlichen Abstände zueinander, da diese durch die Höhe der Frequenz der Eingangsspannung uNF bestimmt werden. Bild 26 stellt dies für die beiden vorkommenden Frequenzen von 2400 Hz (zwischen t1 und t6) und 3600 Hz (ab t7) dar: Bei 2400 Hz treten die Ausgangsimpulse uIMP mit größeren Abständen auf als bei 3600 Hz.

Hierdurch ergibt sich folgender wichtige Zusammenhang: Bei 2400 Hz ist der Mittelwert der Impulsspannung U imp geringer als bei 3600 Hz (uM2). Beide Mittelwerte sind im Diagramm Uimp eingezeichnet. Auf ihre Bedeutung wurde bereits in Bild 23 eingegangen.

Zur Erzielung der erforderlichen Impulsverzögerung innerhalb der Impulsstufe dient die in Bild 27 wiedergegebene Schaltung. Sie besitzt ein RC-Glied und einen EXOR-Schaltkreis. Da die Funktion dieser etwas ungewöhnlichen Schaltung sicherlich nicht überall bekannt ist, wird sie mit Hilfe der Impulsdiagramme von Bild 28 erklärt.

Bild 27: Schaltung der lmpuls-Verzögerungsstufe

Bild 28: Impulsdiagramme der lmpuls-Verzögerungsstufe

E2 der EXOR-Stufe IC10.3 erhält ständig L-Pegel (Bild 27). Daher arbeitet der Schaltkreis nicht als Signal-Verknüpfungsstufe, sondern lediglich als nichtinvertierender Treiber.

Vor dem Zeitpunkt t1 führt der Eingang El und damit auch der Ausgang A L-Pegel (Bild 28). Der Kondensator C ist entladen und mit seinem rechten Anschluss z.Zt. über den Ausgang mit 0V verbunden.

Zum Zeitpunkt tl wechselt die Spannung Unf auf H-Pegel. Hierdurch wird der Kondensator C über den Widerstand R geladen. Als Folge davon steigt die Spannung am Eingang E1 nach einer e-Funktion an. Dies ist unter (1) im Diagramm Uei dargestellt.

Nach einer gewissen Zeit ist zum Zeitpunkt t2 die Spannung Uei soweit angestiegen, dass sie von ICl0.3 als H-Pegel aufgefasst wird. Hierzu sind bei einer Betriebsspannung von 5 V etwa 2,5 V erforderlich, da IC10.3 ein CMOS-Schaltkreis ist, dessen Schaltschwelle etwa 1/2 UBatt beträgt. Beim Erreichen der Schaltschwelle Us nimmt der Ausgang A zum Zeitpunkt t2 H-Pegel an. Dies ist bei (2) im Diagramm uA dargestellt. Der Ausgangsspannungssprung von 0V auf 5V wird vom Kondensator C auf den Eingang E1 übertragen. Als Folge davon nimmt die Spannung UE1 plötzlich etwa den Wert 7 V an. Dies ist bei (3) im Diagramm UE1 zu beobachten. Der plötzliche Spannungsanstieg am Eingang EI wirkt als Mitkopplung, wodurch es zu dem eindeutig rechteckförmigen Schaltverhalten der Stufe kommt.

Da der linke Kondensatoranschluss zum Zeitpunkt t2 eine Spannung von 7 V besitzt, am Anschluss Unf aber nur 5 V anstehen, beginnt zwischen t2 und t3 ein Entladevorgang des Kondensators auf einen Spannungswert von 5 V. Diese Entladung wird zum Zeitpunkt t3, wenn die Spannung Unf wieder auf L-Pegel wechselt, verstärkt und strebt nunmehr 0V an. Dies kann bei ( 4) im Diagramm UE1 beobachtet werden.

Zum Zeitpunkt t4 wird die Schaltschwelle von IC10.3 wieder unterschritten. Als Folge davon nimmt der Ausgang Ades Schaltkreises L-Pegel an. Dies ist bei (5) im Diagramm Ua dargestellt.

Der H/L-Spannungssprung am Ausgang A überträgt sich durch den Kondensator auf den Eingang EI, der aus diesem Grund zum Zeitpunkt t4 einen Spannungswert von etwa -2 V annimmt (siehe bei (6) im Diagramm UE1)· Diese Spannung baut sich wieder auf 0V ab, bevor bei t5 ein neuer Zyklus beginnt.

Zwischen dem Auftreten des Eingangssignals Unf und dem Ausgangssignal Ua liegt die Verzögerungszeit tv· Sie wird durch das RC-Glied bestimmt und beträgt etwa eine Zeitkonstante. Hierbei können z.B. durch unterschiedliche Schaltschwellen geringe Abweichungen auftreten. Die Länge des Ausgangssignals zwischen t2 und t4) entspricht fast genau der Länge des Eingangssignals (zwischen t1 und t3). Auch hierbei sind gewisse Abweichungen nicht störend.

Bild 29 zeigt die vollständige Schaltung der Impulsstufe. Der zeitbestimmende Widerstand besteht aus dem Festwiderstand R39 und dem Trimmerwiderstand R38 zur Einstellung der genauen Impuls-Verzögerungszeit. Der Abgleich dieser Stufe ist im fachpraktischen Teil dieser Übung beschrieben.

Bild 29: Schaltung der Impulsstufe

Die Mittelwertbildung der Impulse

Zur Mittelwertbildung einer Impulsspannung ist eine Schaltung mit integrierendem Verhalten erforderlich. Hierzu eignet sich ein Tiefpass, der oberhalb seiner Grenzfrequenz, also im Sperrbereich, betrieben wird. Ein derartiger Tiefpass ist der Impulsstufe nachgeschaltet (Bild 22).

RC-Glieder, wie sie z.B. als „Siebglieder“ in einfachen Netzgeräten zur Glättung der Ausgangsspannung verwendet werden, besitzen integrierendes Verhalten und bilden den Mittel wert der angeschlossenen Spannung. Zur Erzielung einer geringen Restwelligkeit bei möglichst kurzem Einschwingverhalten sind jedoch mit Operationsverstärkern aufgebaute aktive Tiefpassfilter wesentlich besser geeignet. Bild 30 zeigt die verwendete Schaltung.

Bild 30: Schaltung des Tiefpasses zur Mittelwertbildung

In der Schaltung des aktiven Tiefpasse {Bild 30} sind zunächst zwei „normale“ RC-Glieder erkennbar. Die Rückführung der Ausgangsspannung über C20 auf die Widerstände R42 und R43 bewirkt einen besonders steilen Dämpfungsanstieg im Sperrbereich des Tiefpasses und damit ein gutes Integratorverhalten. Dies liegt an den bei verschiedenen Eingangsfrequenzen unterschiedlichen Phasenverschiebungen der Signale, wodurch teilweise Phasenauslöschungen entstehen. Auf weitere Einzelheiten des aktiven Tiefpasses soll hier nicht eingegangen werden, da hierzu umfangreiche mathematische Betrachtungen nötig sind. Die optimale Dimensionierung des Tiefpasses wurde auch nicht durch eine exakte Berechnung der Schaltung, sondern experimentell gefunden, weil dies einfacher und

schneller zum Ziel führte.

Durch den Tiefpass ergibt sich ein bestimmter Zusammenhang zwischen der Frequenz der Eingangsspannung und der Ausgangsspannung des Tiefpasses. Dieser Zusammenhang ist in Bild 31 als „Kennlinie der Frequenz/Spannungs-Wandlung“ wiedergegeben.

Bild 31: Kennlinie der Frequenz/Spannungs-Wandlung

Die Ausgangsspannung Um des Tiefpasses besitzt bei verschiedenen Eingangsfrequenzen unterschiedliche Werte, wobei nur der Bereich zwischen 2,4 kHz und 3,6 kHz interessiert (Bild 31). Diese beiden Frequenzwerte entsprechen L- und H-Signal der seriellen Daten. Die Mittenfrequenz beträgt 3 kHz und die dazugehörige Gleichspannung etwa 2,2 V. Auf diesen Wert ist die Sehwellspannung des dem Tiefpass nachgeschalteten Komparators eingestellt (Bild 22}. Der Komparator unterscheidet zwischen Frequenzen unterhalb und oberhalb von 3 kHz bzw. den sich daraus ergebenden Spannungswerten.

Die Komparatorstufe

Neben der Unterscheidung zwischen H- und L-Pegel, die bei einer Frequenz von 3 kHz erfolgt, wird in der Komparatorstufe geprüft, ob sich die Frequenz des empfangenen Signals innerhalb bestimmter Grenzen bewegt. Frequenzwerte unterhalb von 1,6 kHz oder oberhalb von 4,3 kHz liegen deutlich außerhalb der Sollfrequenzen von 2,4 kHz und 3,6 kHz und werden daher als Fehler bewertet. Hierdurch können z.B. Sprach- und Musikanteile innerhalb einer Datenaufzeichnung erkannt und als Datensignale verworfen werden.

Insgesamt besitzt die Komparatorstufe drei Komparatoren mit Sehwellspannungen, die den Frequenzwerten 1,6 kHz, 3 kHz und 4,3 kHz entsprechen. Die Ausgangssignale der drei Komparatoren werden miteinander logisch verknüpft. Bild 32 zeigt das Blockschaltbild des Komparatorteils.

Bild 32: Blockschaltbild des Komparatorteils

Alle Komparatoren werden von der Spannung Um angesteuert, deren Höhe von der Eingangsfrequenz abhängig ist. Dieser Zusammenhang geht aus dem Diagramm Um von Bild 33 hervor. Beachten Sie bei den folgenden Erklärungen sowohl Bild 32 als auch Bild 33.

Bild 33: Wirkungsweise der drei Komparatoren und der internen Freigabe

IC13.4 erhält am invertierenden Eingang eine Vergleichsspannung von 1,1 V. Wenn uM diesen Wert überschreitet, führt IC13.4 H-Pegel am Ausgang. Hierzu muss die Frequenz größer als 1,6 kHz sein.

Der Komparator IC13.3 erhält am nichtinvertierenden Eingang eine Vergleichsspannung von 2,2 V, wodurch er bei einer Frequenz von 3 kHz umschaltet. Unterhalb von 3 kHz überwiegt die Vergleichsspannung. IC13.3 führt in diesem Fall H-Pegel am Ausgang. Oberhalb von 3 kHz ist Um größer als die Vergleichsspannung, so dass IC13.3 dann L-Pegel abgibt.

Es fällt auf, dass die Eingangsfrequenz und das Datensignal zueinander invers sind: Bei hoher Eingangsfrequenz tritt L-Pegel auf und umgekehrt. Zur Erzielung der richtigen Frequenzlage (L-Signal entspricht 2400 Hz, H-Signal 3600 Hz) braucht das durch IC13.3 gewonnene Datensignal lediglich invertiert zu werden.

Mit 3,3 V erhält IC13.2 die Vergleichsspannung für eine Frequenz von 4,3 kHz. Solange die empfangene Frequenz geringer ist, überwiegt die Vergleichsspannung. IC13.2 führt dann H-Pegel am Ausgang. Erst bei Frequenzen oberhalb von 4,3 kHz schaltet IC13.2 auf L-Pegel durch.

Die Ausgänge der Komparatoren für 1,6 kHz und 4,3 kHz sind miteinander UND verknüpft (Bild 32). Als Ergebnis dieser Verknüpfung ergibt sich im Diagramm „interne Freigabe“ von Bild 33 zwischen 1,6 kHz und 4,3 kHz H-Pegel. Innerhalb dieses Bereichs liegen die Nennfrequenzen des Kassetten-Interfaces. Im Block „Freigabeverzögerung“ wird geprüft, ob es sich bei den empfangenen Frequenzen um einen konti nui erl i chen Datenstrom oder nur um kurzzeitige und damit unbrauchbare Signale handelt. Dies geschieht auf folgende Weise: Der Ausgang „out“ der Freigabeverzögerung gibt erst dann H-Signal ab, wenn ohne Unterbrechung etwa 0,5 s lang eine Frequenz zwischen 1,6 kHz und 4,3 kHz erkannt wurde. Erst nach Ablauf dieser „tv“ genannten Verzögerungszeit erhält IC15.3 am oberen Eingang H-Pegel (Bild 32). Nun werden die von IC13.3 stammenden Daten weitergeleitet und dabei invertiert. Hierdurch entsteht die richtige Frequenzlage. Bei einer eventuellen Unterbrechung des Datenstroms nimmt „out“ sofort L-Pegel an und blockiert IC15.3. Anschließend muss der Datenstrom erst wieder 0,5 s lang vorliegen, bevor er durch die „verzögerte interne Freigabe“ weitergeleitet wird. Durch diese Maßnahme erkennt das Kassetten-Interface den Anfang und das Ende einer Datenübertragung und blendet selbständig eventuell vorhandene Sprach- und Musiksignale aus.

Der Ausgang von IC15.3 ist durch IC15.2 mit dem verzögerten Freigabesignal verknüpft. Die rote LED „DATA“ leuchtet bei freigegebenem Datenweg im Rhythmus der H/L-Datensignal e auf.

Neben der internen Freigabe bzw. der verzögerten internen Freigabe besitzt die Schaltung mit dem Anschluss „E“ eine zusätzliche Freigabeleitung zur „externen Freigabe“ des Datenweges. Führt der Anschluss „E“ H-Pegel, werden die empfangenen Daten über „RxD“ an die programmierbare Serienschnittstelle abgegeben. Im BFZ/MFA-Computer wird diese Steuerungsmöglichkeit jedoch nicht benutzt. Der Anschluss „E“ führt hier durch einen Pull-Up-Widerstand ständig H-Pegel.

Hierdurch ist die UND-Stufe am Ausgang „RxD“ unwirksam und lässt die Datensignale ständig passieren.

Bild 34 zeigt die Schaltung des Komparatorteils. Im Anschluss daran werden die bisher noch nicht behandelten Einzelheiten erklärt.

Bild 34: Schaltbild des Komparatorteils

R45 bis R48 bilden den Spannungsteil er für die Vergleichsspannungen der drei Komparatoren in Höhe von 1,1 V, 2 ,2 V und 3 ,3 V. R49 sorgt für eine Mitkopplung des Datenkomparators IC13.3, wodurch ein exaktes Schaltverhalten dieser Stufe gewährleistet ist.

Die in Bild 32 dargestellte UND-Stufe zur Verknüpfung der Ausgangssignale von IC13.2 und IC13.4 wird nicht durch einen Schaltkreis gebildet, sondern durch eine „Wired-AND-Schaltung“. Dies ist möglich, weil die Komparatoren von IC13 Open-Collektor-Ausgänge besitzen, die miteinander verbunden werden dürfen. Hierdurch ergibt sich die Funktion einer UND-Stufe.

R52 ist der für IC13.3 erforderliche Arbeitswiderstand. R50/R51 wirken als Arbeitswiderstand für die Wired-AND-Schaltung von IC13.2 und IC13.4. Die Freigabeverzögerung wird durch R50, C22, IC14 und IC15.1gebildet und arbeitet auf folgende Weise:

Besitzt Um einen Wert zwischen 1,1 V und 3,3 V, sind die Ausgangstransistoren von IC13.2 und IC13.4 gesperrt. C22 wird über R50 geladen, wodurch die Spannung am Eingang des Timer-Bausteins nach einer e-Funktion ansteigt. Der innerhalb von IC14 vorhandene Komparator besitzt eine festliegende Schaltschwelle von 2/3 der Betriebsspannung (etwa 3,4 V). Bis C22 auf diesen Wert aufgeladen ist, vergeht etwa eine Zeit von 0,5 s. Nach Ablauf dieser Zeit schaltet der Ausgang des Timers auf L-Pegel. Da für die „verzögerte Freigabe“ jedoch ein H-Signal benötigt wird, ist IC15.1 als Inverterstufe nachgeschaltet.

Sobald Um einen Wert außerhalb der festgelegten Grenzen zwischen 1,1 V und 3,3 V annimmt, wird C22 über R51 rasch entladen, wodurch IC14 auf H-Pegel zurückschaltet. Hierdurch nimmt die verzögerte Freigabe“ L-Pegel an und sperrt IC15.2 und IC15.3. Die Zeit hierzu ist äußerst kurz und wird durch C22 und R51 sowie die inneren Widerstände der Komparatoren IC13.2 bzw.IC13.4 bestimmt. R51 begrenzt den Entladestrom des Kondensators auf einen zulässigen Wert. C23 hat keinen Einfluss auf die Zeitverzögerung, sondern dient lediglich zur Unterdrückung eventuell auftretender Störimpulse.

Die in Bild 32 dargestellte UND-Stufe am Ausgang „RxD“ des Komparatorteils wird durch die NAND-Stufe IC15.4 und den nachgeschalteten Inverter IC2.5 gebildet (Bild 34). IC2.5 befindet sich nicht innerhalb des Kassetten-Interfaces, sondern ist Teil der „Programmierbaren Serienschnittstelle. Neben dem Anschluss „E“ , über den durch H-Pegel die „externe Freigabe“ der empfangenen Datensignale erfolgt, kann mit Hilfe des Eingangs „E“ auch eine Freigabe durch L-Pegel erzielt werden. T12 dient hierbei als Inverter. R54 begrenzt den Basisstrom für T12, und D16 schützt den Transistor vor negativen Eingangsspannungen. Bei der Anwendung des Kassetten-Interfaces im BFZ/MFA-Computer werden weder „E“ noch „/E“ angeschlossen. Da R53 ständig H-Pegel an den unteren Eingang von IC15.4 führt, ist der Datenweg trotzdem freigegeben.

Stromlaufpläne

Bild 35 zeigt den Stromlaufplan der programmierbaren Serienschnittstelle und

Bild 36 den des Modems. Beide zusammen bilden das Kassetten-Interface.

Zwischen beiden Leiterplatten bestehen folgende Verbindungen:

- Betriebsspannungsanschlüsse 5 V und 0 V

- Verbindung „T“ (Daten von „TxD“ der Serienschnittstelle zum Modem)

- Verbindung „R“ (Daten vom Modem zum Anschluss „RxD“ der Serienschnittstelle)

Die folgenden Hinweise fassen die wichtigsten Gesichtspunkte des Kassetten-Interfaces zusammen und beschreiben in knapper Form die Aufgabe jeder Stufe.

Hinweise zu Bild 35:

- C1 ist ein Stützkondensator für die Betriebsspannung von 5 V.

- IC1 und IC2.1 erzeugen das L-aktive Freigabesignal „Chip-Select“ für den seriellen

Schnittstellenbaustein IC3. - Mit S1 bis S4 kann die Baugruppennummer eingestellt werden.

- IC2.2 invertiert das L-aktive Reset-Signal des Systembusses, da IC3 einen H-aktiven

Reset-Eingang besitzt. - IC2.3 frischt den Systemtakt (2 MHz) auf.

- IC4, IC5.1, IC5.2 und IC6 bilden den Baudratenteiler. Die Brücken A bis D

legen die Baudrate fest, wobei immer nur eine Brücke geschlossen sein darf. - IC2.5 bringt das vom Modem empfangene Datensignal in die richtige Frequenzlage

(2400 Hz entspricht L-Pegel, 3600 Hz entspricht H-Pegel).

Hinweise zu Bild 36:

- C24 und C25 sind Stützkondensatoren für die Betriebsspannung von 5 V.

- IC10.1 ist zur Erzielung der richtigen Frequenzlage beim Senden als Inverter

geschaltet. - IC11.3 bildet den Integrator, IC11.1 und IC11.2 zusammen den Komparator des

Dreieckgenerators. - Am Meßpunkt MP1 kann die Dreieckspannung mit Hilfe eines Oszilloskopen kontrolliert

werden. - Durch R16 bzw. R17 können eventuelle Unsymmetrien der Dreieckspannung korrigiert

werden. Die Werte für diese Widerstände müssen experimentell ermittelt werden, sie liegen im Bereich von etwa 680 kOhm bis 1 MOhm. - Mit Hilfe von IC10.2 erfolgt die Frequenzumtastung des Dreieckgenerators.

- R11 dient zur Einstellung der Generatorfrequenz.

- Die Transistoren T10 und T11 formen aus der Dreieck- eine Sinusspannung.

- Mit R26 kann die NF-Eingangsempfindlichkeit des Modems eingestellt werden

(Bei ausreichendem NF-Pegel leuchtet die LED D14 auf). - IC12.1 bis IC12.3 und IC13.1 gehören zur NF-Signalaufbereitung.

- IC10.3 und IC10.4 bilden die Impulsstufe. Ihr Arbeitsverhalten wird mit R38

eingestellt. - IC12.4 bildet den Mittelwert der Impulsspannung.

- IC13.2 ist der Komparator zur Überwachung der Maximalfrequenz von 4,3 kHz.

- IC13.3 ist der Datenkomparator und schaltet bei einer Frequenz von 3 kHz.

- IC13.4 ist der Komparator zur Überwachung der Minimalfrequenz von 1,6 kHz.

- IC14 und IC15.1 geben die empfangenen Datensignale erst dann frei, wenn für

mindestens 0,5sec sein ununterbrochenes NF-Signal im zulässigen Frequenzbereich erkannt wurde. In diesem Fall leuchtet bei H-Pegel der Daten die von IC15.2 angesteuerte LED „DATA“ auf. - Am Anschluss „R“ werden die empfangenen Daten abgegeben, wenn der Eingang „E“

H-Pegel führt (oder nicht beschaltet ist). - Zur Abgabe der Daten muss der Eingang „E“ unbeschaltet sein oder L-Pegel führen.

Bild 35: Stromlaufplan der programmierbaren Serienschnittstelle

Bild 36: Stromlaufplan des Kassetten-Interfaces

Platinenlayout

Bestückungsplan

Verdrahtungsplan