Einleitung

Jeder Mikrocomputer enthält neben Prozessor und Speicher auch Eingabe- und Ausgabe-

Einheiten, über die der Datenverkehr mit Geräten außerhalb des Mikrocomputers stattfindet. Häufig bezeichnet man die Eingabe- und Ausgabe-Einheiten auch als Eingabe- bzw. Ausgabe-Ports oder als Eingabe- bzw. Ausgabe-Schnittstellen, und die Geräte außerhalb des Mikrocomputers nennt man Peripheriegeräte.

Die zu übertragenden Daten können entweder seriell oder parallel übermittelt werden. Bei der seriellen Übertragung werden die einzelnen Bits eines Datenbytes nacheinander über eine einzige Leitung gesendet oder empfangen, während dies bei der parallelen Datenübertragung gleichzeitig über entsprechend viele Leitungen geschieht. Innerhalb einer bestimmten Zeit kann mit der parallelen Datenübertragung eine größere Datenmenge übermittelt werden als mit der seriellen.

Bei großen Entfernungen zwischen Peripheriegerät und Mikrocomputer bevorzugt man die serielle Übertragung. Sollen große Datenmengen in kurzer Zeit übermittelt werden, so wählt man die parallele Übertragung.

In den Kapiteln 4.1 und 4.2 wurden Eingabe- und Ausgabe-Einheiten für einen parallelen Datenaustausch beschrieben. Die Anzahl ihrer Ein- bzw. Ausgänge ist auf acht beschränkt und damit an die Datenbus-Breite des Mikrocomputers angepasst. Derartige einfache Ein- und Ausgabebaugruppen werden meist dort eingesetzt, wo man einzelne Signale (z.B. für Relais, Schütze, Anzeigelampen und Motoren) benötigt oder wo nur wenige Rückmeldesignale von Schaltern und Endlage-Meldern aus einer Maschine oder Anlage zu verarbeiten sind.

Zur Steuerung umfangreicher Maschinen oder Peripheriegeräte reicht die Anzahl der Ein- und Ausgänge der genannten Ports oft nicht aus. In diesen Fällen muss man entweder mehrere Ein- und Ausgabeports verwenden oder aber Ein/Ausgabe-Baugruppen mit Bausteinen speziell für solche Anwendungsfälle. In ihnen sind mehrere 8-Bit-Ports zusammengefasst, wobei die Funktion der einzelnen Ports vom Anwender durch Programmierung bestimmt werden kann. Diese Programmierbarkeit führte zu Bezeichnungen wie programmierbarer Schnittstellen-Baustein oder programmierbarer Input/Output-Baustein.

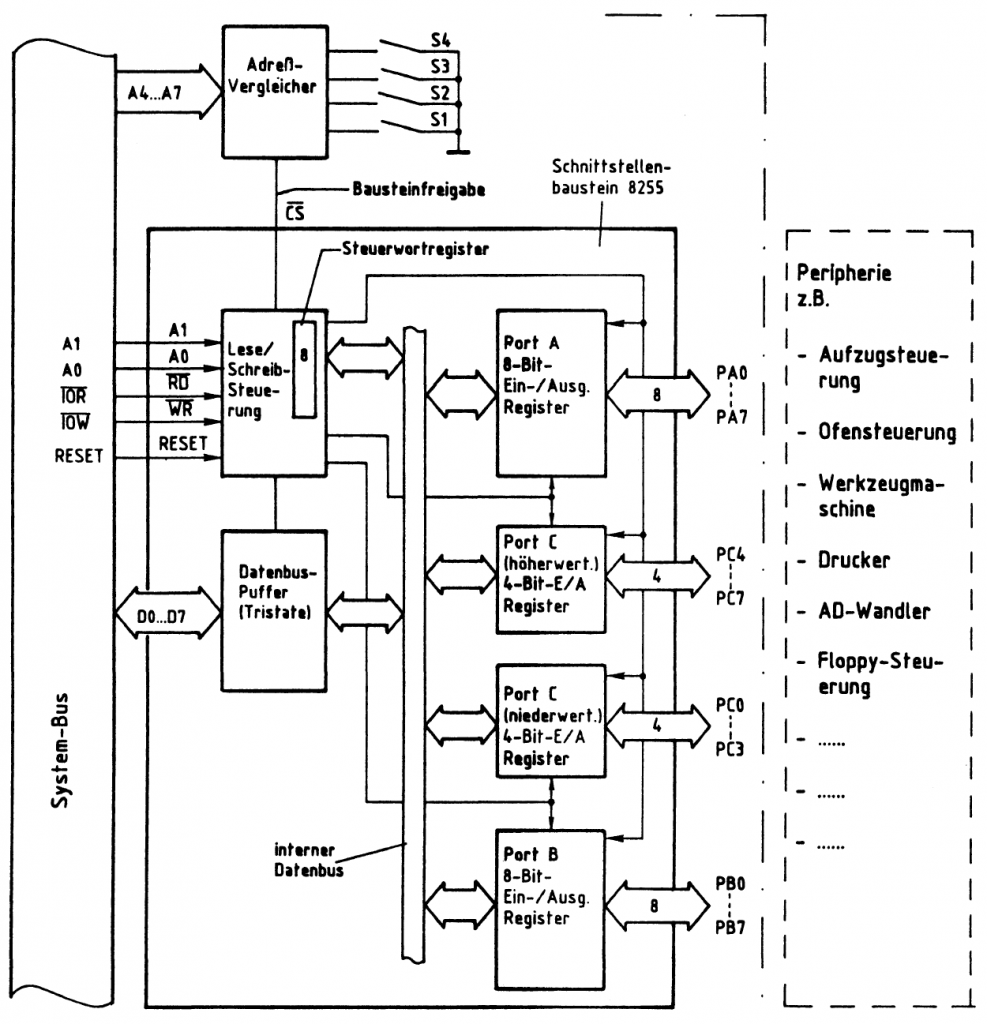

Blockschaltbild und Arbeitsweise der Parallel-Baugruppe

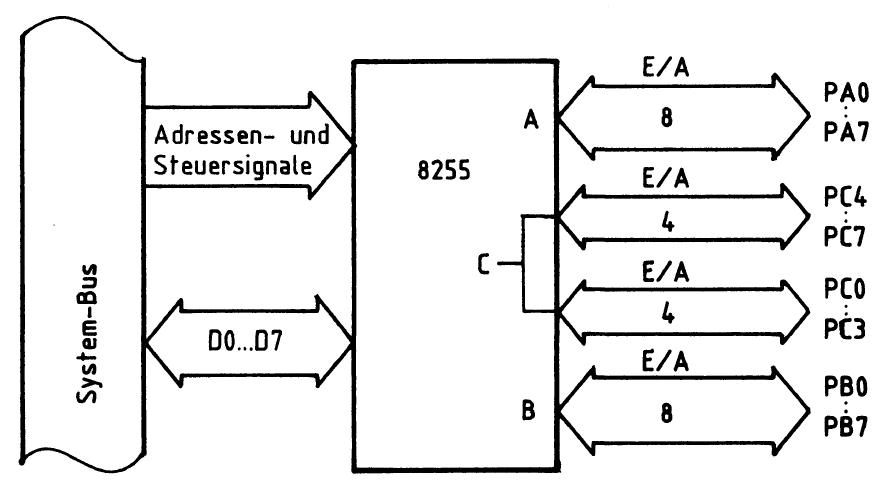

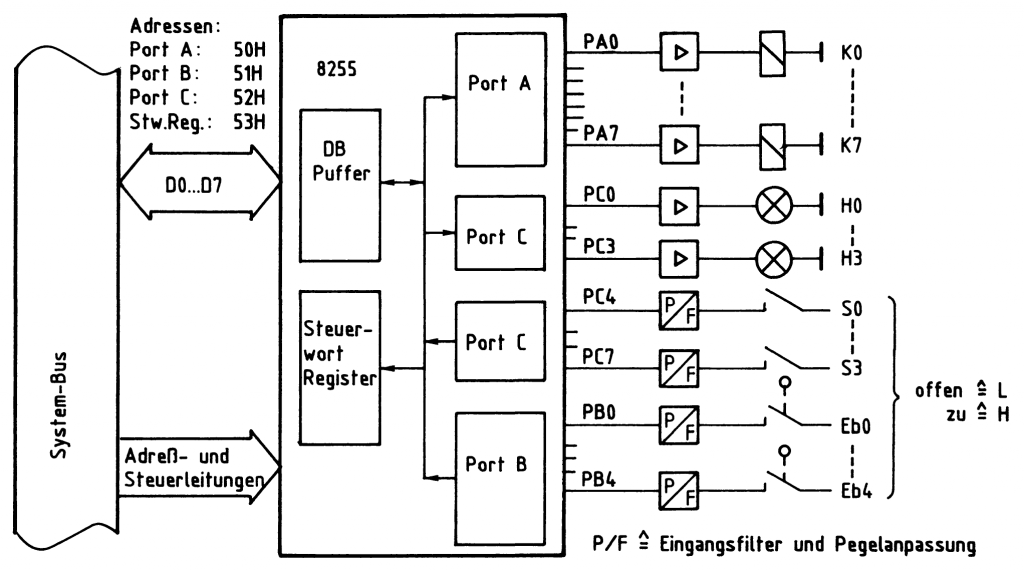

Bild 1 zeigt das Blockschaltbild der programmierbaren Parallel-Schnittstelle, die aus den Schaltungsteilen Adressvergleicher und programmierbarer Schnittstellenbaustein (8255) besteht. Zunächst wird die grundsätzliche Wirkungsweise der Baugruppe anhand dieses Blockschaltbildes erklärt

Bild 1 : Das Blockschaltbild der programmierbaren Parallelschnittstelle

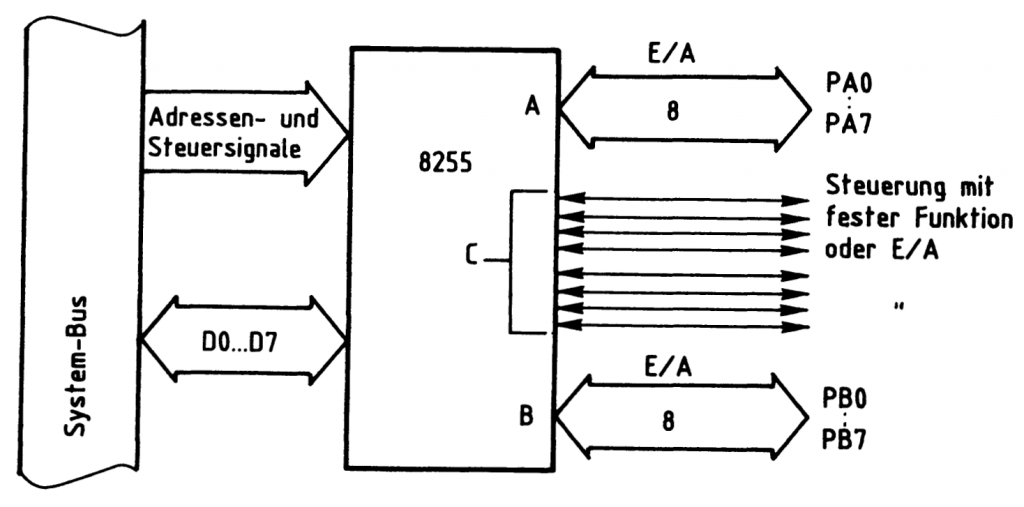

Der programmierbare Schnittstellenbaustein mit der Bezeichnung 8255 enthält drei voneinander unabhängige Datenkanäle (Ports), die durch Laden eines Steuerwortes in das interne Steuerwort-Register als Eingabe- oder Ausgabe-Ports programmiert werden können.

Alle Daten, die vom Mikroprozessor über Ausgabeports zur Peripherie oder von der Peripherie über Eingabe-Ports zum Mikroprozessor gelangen, werden über den internen Datenbus und den Datenbus-Puffer transportiert. Die Adressierung der Ports und des Steuerwort-Registers erfolgt über die Adressleitungen A0 und A1. Mit Hilfe der Steuerleitung IOR bzw. IOW wird der Datentransport in die jeweilige Richtung ausgelöst. Ein Datentransport ist jedoch nur möglich, wenn der Baustein durch den Adressvergleicher über die Bausteinfreigabe-Leitung freigegeben ist. Andernfalls ist der Datenbus-Puffer hochohmig.

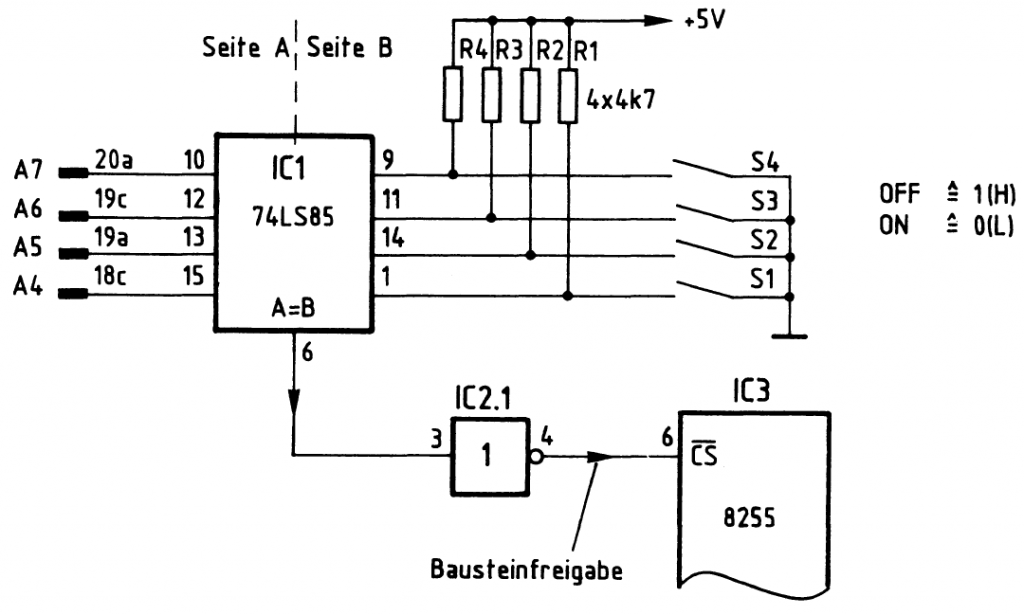

Der Adreßvergleicher und die Baugruppennummer

Der Mikroprozessor steuert die parallele Schnittstelle wie jede andere Eingabe- und Ausgabe-Einheit an. Da in einem Mikrocomputer-System nur jeweils eine einzige Einheit aktiviert sein darf, müssen alle im System vorhandenen Eingabe- und Ausgabe- Einheiten unterschiedliche Baugruppennummern besitzen. Aus diesem Grund ist die Baugruppennummer mit Hilfe von Schaltern einstellbar. Ein Adressvergleicher

übernimmt die Aufgabe, die Baugruppe nur dann zu aktivieren, wenn der Prozessor diejenige Adresse aussendet, die der eingestellten Baugruppennummer entspricht: Bild 2.

Bild 2: Der Adressvergleicher

Nur wenn die Bitkombination auf den Adressleitungen A4 bis A7 gleich der mit den Schaltern Sl bis S4 eingestellten Bitkombination ist, gibt der 4-Bit-Vergleicher IC1 an seinem Ausgang »A=B« ein H-Signal ab (Bild 2). Da zur Aktivierung des 8255 jedoch ein L-Signal am CS-Eingang notwendig ist, wird das Ausgangssignal von IC1 durch IC2.1 invertiert.

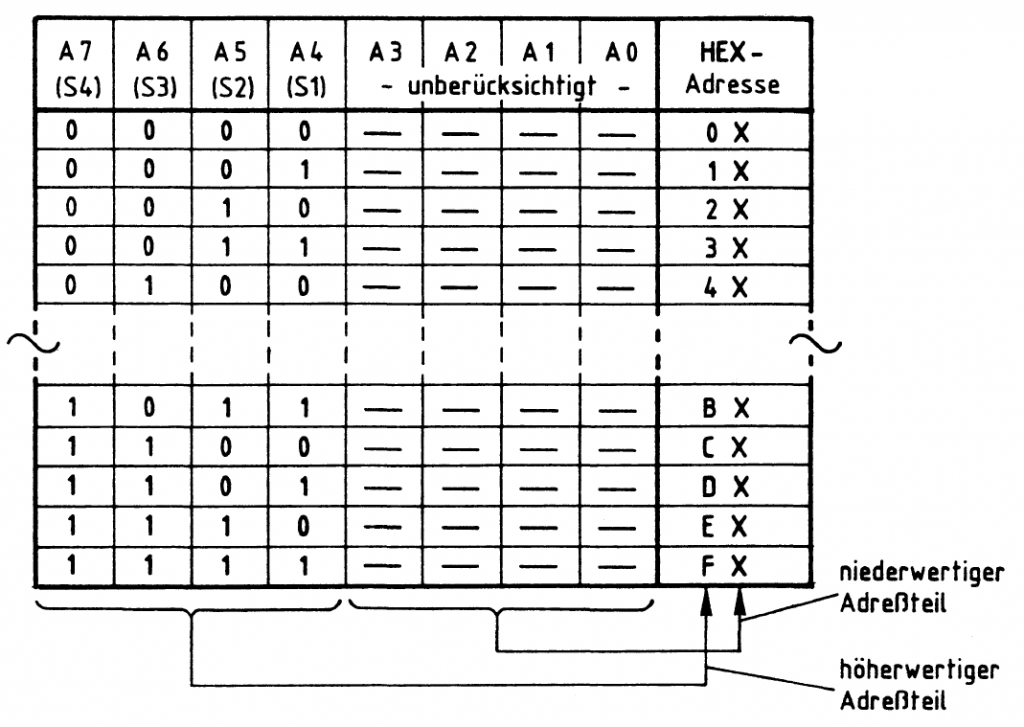

Der Prozessor gibt beim Ansprechen einer Eingabe- oder Ausgabe-Baugruppe stets eine vollständige 8-Bit-Adresse an den Adressleitungen A0 bis A7 aus. Bei dem hier realisierten Adressvergleich werden jedoch die Adressleitungen A0 bis A3 nicht berücksichtigt. Daher steht nicht der volle Adressbereich von 00H bis FFH mit 256 verschiedenen Adresswerten zur Verfügung. Mit den Schaltern S1 bis S4 lassen sich lediglich 16 verschiedene Signalzustände (Baugruppennummern) einstellen. Da diese Schalter den vier höherwertigen Adressbits A4 bis A7 zugeordnet sind, kann die Baugruppennummer nur Werte von 0XH bis FXH annehmen. Das »X« steht hier für die vier niederwertigen Adressbits A0 bis A3, die beim Adressvergleich nicht benutzt werden: Bild 3.

Bild 3: Die Bildung der Baugruppen-Nummern auf der programmierbaren Parallelschnittstelle

Im folgenden werden diese Schalterstellungen zugrundegelegt

| S4 (A7) | S3 (A6) | S2 (A5) | S1 (A4) |

| ON | OFF | ON | OFF |

| 0 | 1 | 0 | 1 |

Hierdurch ergibt sich die Baugruppennummer 5XH. Grundsätzlich kann jede der 16 möglichen Baugruppennummern verwendet werden. Es ist aber darauf zu achten, dass alle Eingabe- oder Ausgabe-Baugruppen eines Mikrocomputer-Systems unterschiedliche Adressen besitzen, da es andernfalls zu Schäden am Gerät kommen kann.

Die Adressierung der drei Ports und des Steuerwort-Registers

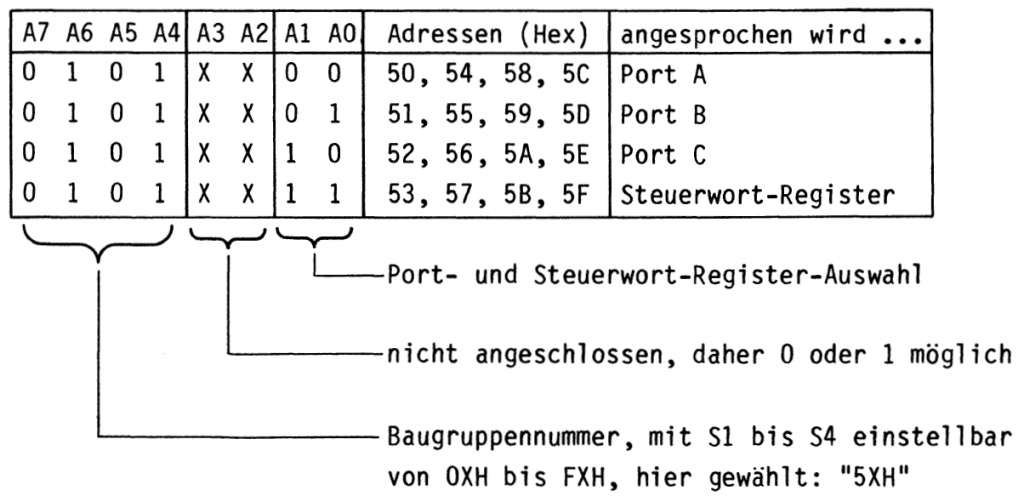

Beim Lesen der einzelnen Eingabeports, beim Ausgeben von Daten über die Ausgabeports und beim Einschreiben von Steuerworten in das Steuerwort-Register muss dem Baustein 8255 über die Adressanschlüsse A0 und Al mitgeteilt werden, welcher der vier internen Blöcke (drei Ports und ein Steuerwort-Register, siehe Bild 1) am gewünschten Datenverkehr beteiligt sein soll. Bild 4 zeigt die Adressierung der Blöcke durch die Adressleitungen A0 und A1.

| A1 | A0 | Port/Register |

| 0 | 0 | Port A |

| 0 | 1 | Port B |

| 1 | 0 | Port C |

| 1 | 1 | Steuerwort / Register |

Bild 4: Die Adressierung der Ports und des Steuerwort-Registers

Bild 5: Die Adreßbildung mit den Adreßleitungen AO bis A7

Die Bitkombination an A4 bis A7 (siehe Bild 5) entspricht der mit den Adressschaltern S1 bis S4 eingestellten Baugruppennummer. Die Bitkombination an A0 und A1 bestimmt, ob eines der drei Ports oder das Steuerwort-Register des Schnittstellenbausteins 8255 angewählt wird.

Die Adreßleitungen A2 und A3 sind nicht angeschlossen; daher kann ihr Signalzustand 1 oder 0 sein. Hieraus ergeben sich vier mögliche Adressen für jedes Port und das Steuerwort-Register. Port A kann beispielsweise unter den Adressen 50H, 54H, 58H und 5CH angesprochen werden. Diese Mehrfach-Adressierung ist durch die einfache Schaltung bedingt. Alle Adressen beginnen aber stets mit der durch S1 bis S4 gebildeten Hex-Zahl (hier 5). Um Verwirrungen zu vermeiden, sollten die Ports und das Steuerwort-Register fortlaufend, z.B. unter den Adressen 50H, 51H, 52H und 53H, angesprochen werden. (Es wäre natürlich auch möglich, sie z. B. unter den Adressen 58H, 55H, 5EH und 57H zu erreichen.)

Die Steuerung der Datenübertragungs-Richtung

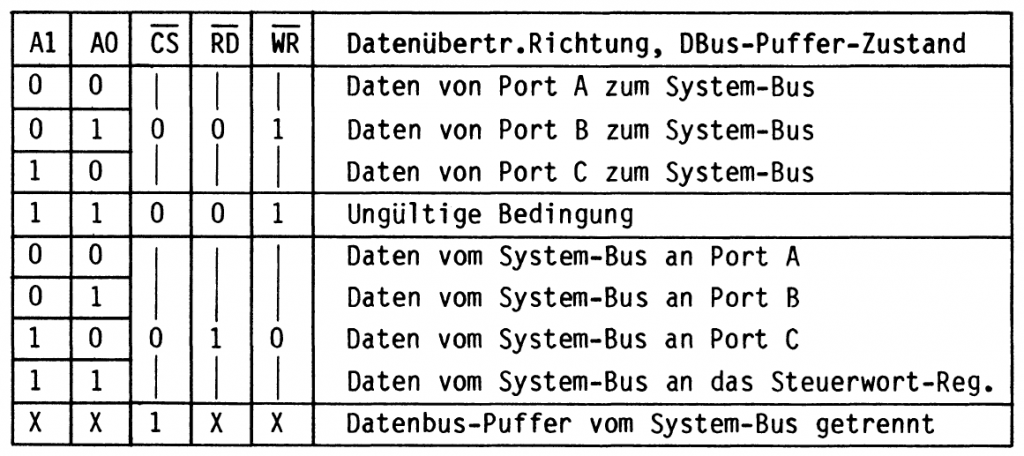

Nachdem der Mikroprozessor die Adresse eines der drei Ports oder des SteuerwortRegisters ausgegeben hat, steuert er durch L-Pegel auf einer der beiden Steuerleitungen IOR oder IOW, ob er Daten aus dem Baustein lesen oder zum Baustein senden will. Die beiden Steuerleitungen sind mit den Bausteinanschlüssen RD und WR verbunden (Bild 1). Mit den Pegeln an diesen Eingängen wird innerhalb des Bausteins über die Lese/Schreib-Steuerung die Datenübertragungs-Richtung gesteuert.

In Zusammenwirken mit den Pegeln auf den Bausteineingängen A0, Al und CS erfolgt der Zugriff zu den einzelnen Ports und dem Steuerwort-Register wie in Bild 6 dargestellt

Bild 6: Die Steuerung der Datenübertragungs-Richtung und des Datenbus-Puffers

In das Steuerwort-Register kann nur geschrieben werden. Bei H-Pegel am CS-Eingang wird der Datenbus-Puffer in den hochohmigen Zustand geschaltet und dadurch vom System-Bus getrennt. Die Pegel auf den Eingängen A0, A1, RD und WR sind dann für die Funktion des Bausteins bedeutungslos

Die Betriebsarten des Schnittstellen-Bausteins 8255

Zur Anpassung an die vielfältigen Erfordernisse der Peripherie kann man den Schnittstellenbaustein

in den Betriebsarten 0, 1 und 2 benutzen. Zunächst werden die wesentlichen Merkmale dieser drei Betriebsarten dargestellt.

Betriebsart 0 (einfache Ein/Ausgabe; vgl. Bild 7):

- Die Ports A, B und C werden wahlweise als Eingabe- oder als Ausgabe-Ports

betrieben; - Port C ist in zwei 4-Bit-Kanäle aufteilbar;

- je ein 4-Bit-Kanal von Port C kann in Verbindung mit den Ports A und B verwendet

werden (siehe auch Bild 1); - die Port-Ausgänge haben Zwischenspeicher;

- die Port-Eingänge arbeiten ohne Zwischenspeicher.

Bild 7: Die Betriebsart 0 des Bausteins 8255

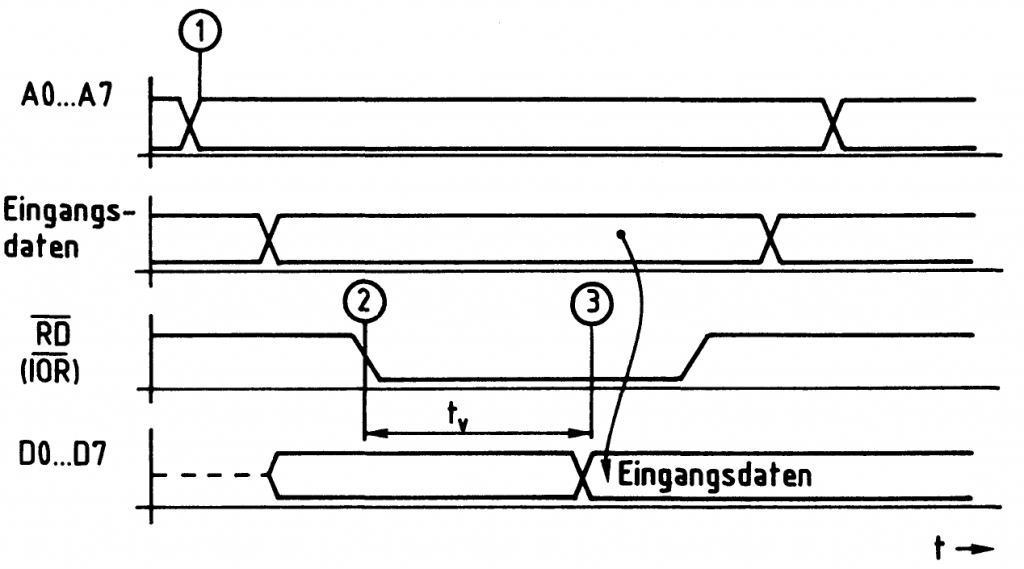

In der Betriebsart 0 werden die drei Ports wie Ein- oder Ausgabebaugruppen behandelt, d. h. Daten werden an das ausgewählte Port ausgegeben oder aus ihm gelesen. Bild 8 zeigt den Signalverlauf für das Lesen von Daten aus einem Eingabe-Port.

Bild 8: Das Lesen eines Eingabe-Ports

(1) Der Prozessor gibt auf den Leitungen A0 bis A7 die Portadresse aus.

(2) Der Prozessor schaltet das Steuersignal IOR auf L-Pegel.

(3) Nach einer Verzögerungszeit tv wird der zu diesem Zeitpunkt an den Eingängen vorhandene Signalzustand auf den Datenbus durchgeschaltet (und in den Akku der CPU übernommen).

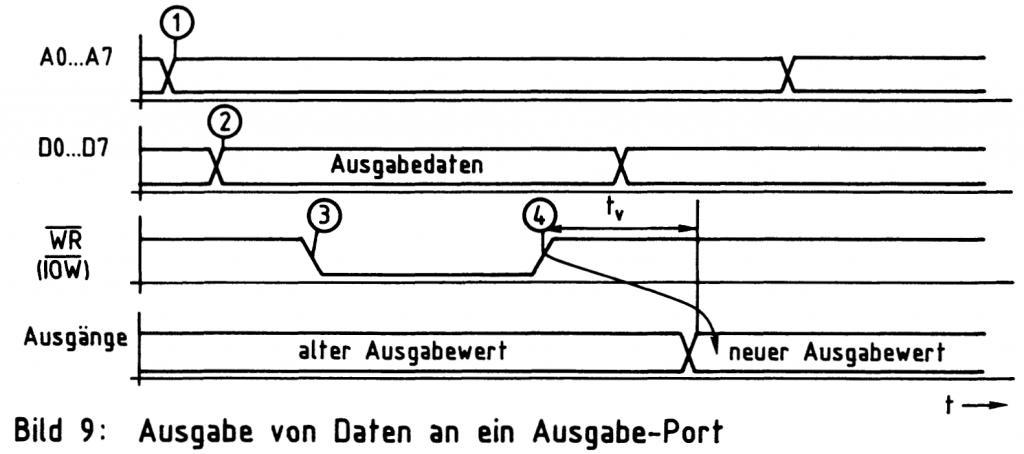

Bild 9: Die Ausgabe von Daten an ein Ausgabe-Port

(1) Der Prozessor gibt auf den Leitungen A0 bis A7 die Adresse des Ausgabe-Ports aus.

(2) Der Prozessor stellt das auszugebende Datenwort bereit.

(3) Mit dem L-Pegel auf der Steuerleitung IOW zeigt der Prozessor an, dass er Daten in das adressierte Ausgabe-Port schreiben will.

(4) Mit der L-H-Flanke des Steuersignals wird das Datenwort in den Ausgabe-Zwischenspeicher übernommen und erscheint nach einer Verzögerungszeit tv (ca. 70 ns) am Ausgang des Ports.

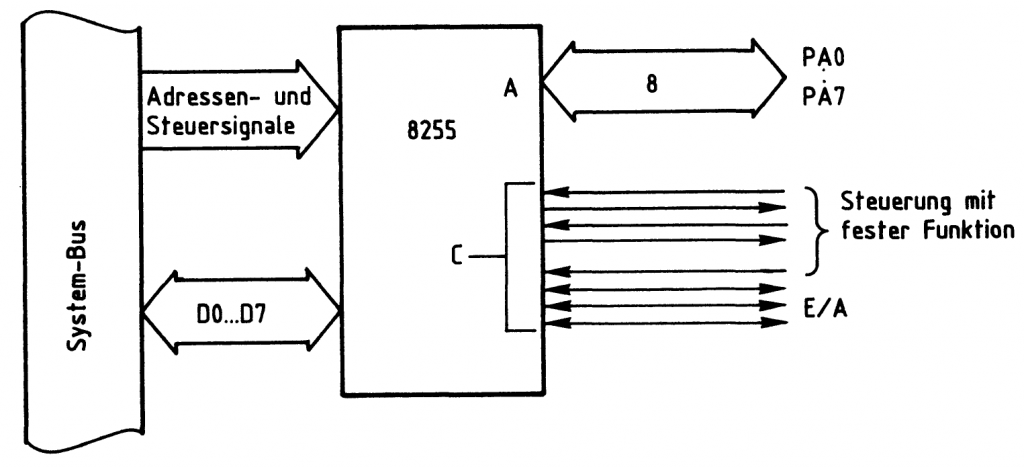

Betriebsart 1 (Ein-/Ausgabe mit zusätzlichen Steuerleitungen; vgl. Bild 10):

Diese Betriebsart dient zum Austausch von Ein-Ausgabe-Daten zu oder von einem Port in Verbindung mit zusätzlichen Steuersignalen bzw. »Quittungs-Signalen«. Hierzu werden die drei Ports wie folgt verwendet:

- Die Ports A und/oder B werden als Eingabe- oder als Ausgabe-Port betrieben.

- Jedem dieser beiden Ports sind vier Leitungen des Ports C mit teilweise fester

Funktion zugewiesen.

Bild 10: Die Betriebsart 1 des Bausteins 8255

Die Betriebsart 1 wird z.B. dazu verwendet, über die Parallelschnittstelle einen Matrix-Drucker anzusteuern. Hierbei dient Port A als Datenkanal und eine Hälfte von Port C zur Übertragung der notwendigen Steuersignale; siehe Seite 367ff.

Betriebsart 2 (Getastete Zweiweg-Bus-Ein-/Ausgabe; vgl. Bild 11):

Diese Betriebsart, die nur mit Port A möglich ist, gestattet einen 8-Bit-Datenaustausch mit der Peripherie, wobei Daten gesendet und empfangen werden können. Hierbei sind dem Port A fünf Leitungen des Ports C mit fest vorgegebener Funktion zugeordnet, womit der Datenfluss von Port A gesteuert werden kann. Diese Betriebsart wird in diesem Buch nicht weiter behandelt.

Bild 11 : Die Betriebsart 2 des Bausteins 8255

Die Initialisierung des Schnittstellenbausteins

Die gewünschte Betriebsweise muss vor dem Betrieb der einzelnen Ports programmiert werden. Dies geschieht grundsätzlich durch Senden eines sogen. Steuerwortes an das Steuerwort-Register, das sich innerhalb der Lese/Schreib-Steuerung befindet (Bild 1). Die Lese/Schreib-Steuerung gibt daraufhin entsprechende Steuersignale an die Ports aus. Das Einschreiben des Steuerwortes in das Steuerwort-Register nennt man Initialisieren des Bausteins (Setzen von Anfangsbedingungen).

Hierzu sind folgende Schritte erforderlich:

- Der Akkumulator des Prozessors muß mit dem Wert des erforderlichen Steuerwortes

geladen werden. Hierzu eignet sich der Befehl »MVI A,konst« des Prozessors

8085 . - Zu dem Akku muß das Steuerwort nun an das Steuerwort-Register ausgegeben

werden. Hierzu dient der Befehl »OUT adr« des Prozessors 8085. Die Adresse für

das Steuerwort-Register ist 53H, da hier von der Baugruppennummer 5X ausgegangen

wird; siehe Seite 355ff.

Bei der Initialisierung ist folgendes zu beachten:

- Durch kurzzeitigen H-Pegel am Reset-Eingang des Bausteins wird das Steuerwort-Register gelöscht, und alle Ports werden in den Eingabezustand gebracht. Nach jeder Betätigung der Reset-Taste oder nach einem Kaltstart des Mikrocomputers muss der Baustein daher neu initialisiert werden.

- Die Betriebsarten der Ports A und B können unabhängig voneinander definiert werden. Port A kann z.B. in Betriebsart 1 arbeiten und Port B in Betriebsart 0. Port C wird entsprechend den Erfordernissen der Ports A und B in zwei Teile aufgeteilt.

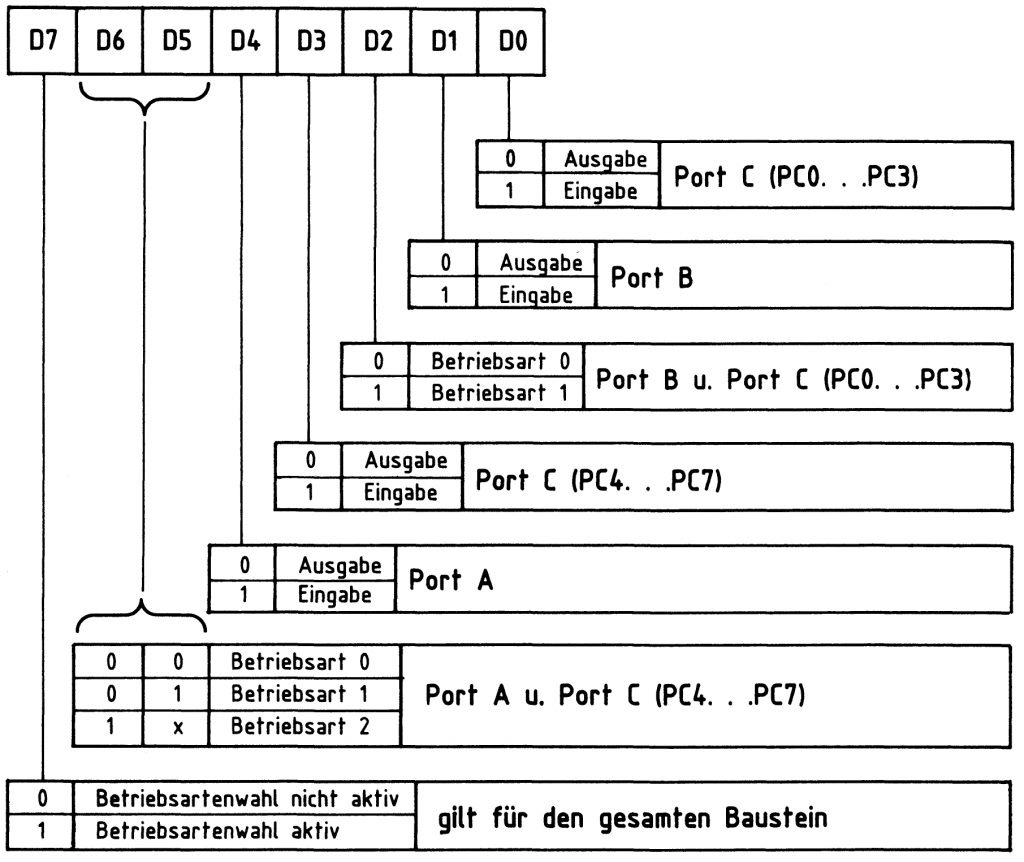

Jedes Steuerwort zur Initialisierung besitzt acht Bits (D0 bis D7), wobei jedes einzelne Bit eine bestimmte Funktion des Bausteins steuert. Bild 12 stellt den Aufbau des Steuerwortes dar. Die Bezeichnungen der einzelnen Bits sind dem Datenbuch des Baustein-Herstellers entnommen.

Bild 12: Der Aufbau des Steuerwortes für den 8255 und die Bedeutung der einzelnen Bits.

Das folgende Beispiel zeigt, wie ein Steuerwort mit Hilfe dieser Tabelle gebildet wird.

Dabei soll der programmierbare Schnittstellenbaustein wie folgt arbeiten:

- Betriebsart 0

- PortA: Eingabeport

- PortB: Ausgabeport

- Port C, PC0 bis PC3: 1/2 Ausgabeport ( 4 Ausgabeleitungen)

- Port C, PC4 bis PC7: 1/2 Eingabeport ( 4 Eingabeleitungen)

Mit Hilfe von Bild 12 wird das Steuerwort gebildet, das sich aus den gewünschten Betriebsbedingungen wie folgt ergibt:

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | |

| 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | = 98 im Hexadezimal-Code |

Bevor die Ports A, B und C entsprechend den genannten Anforderungen als Eingabe- und Ausgabe-Ports betrieben werden können, muß das Steuerwort an das Steuerwort-Register ausgegeben werden. Hierzu dienen folgende Befehle

| … | |

| MVI A, 98 | Steuerwort in den Akku laden |

| OUT 53 | und an Steuerwort-Reg. ausgeben |

| … |

Die Adresse des Steuerwort-Registers (53H) ergibt sich aus Bild 5.

Ein Anwendungsbeispiel für die Betriebsart 0

Das folgende Beispiel zeigt, wie mit Hilfe eines einzigen Schnittstellenbausteins eine recht umfangreiche Steuerung aufgebaut werden kann.

Bild 13: Die Verbindung von einer externen Anlage zum Schnittstellenbaustein 8255.

Aus der Schaltung von Bild 13 ergeben sich für den Schnittstellenbaustein die

folgenden Betriebsbedingungen:

- Betriebsart 0

- PortA: Ausgabeport

- PortB: Eingabeport

- Port C, PCO bis PC3: Ausgabeport

- Port C, PC4 bis PC7: Eingabeport

Mit Hilfe der Tabelle in Bild 12 ergibt sich für das Steuerwort der hexadezimale Wert SA. Zur Initialisierung des Schnittstellenbausteins wird dieses Steuerwort in das Steuerwort-Register (Adresse 53H) geschrieben.

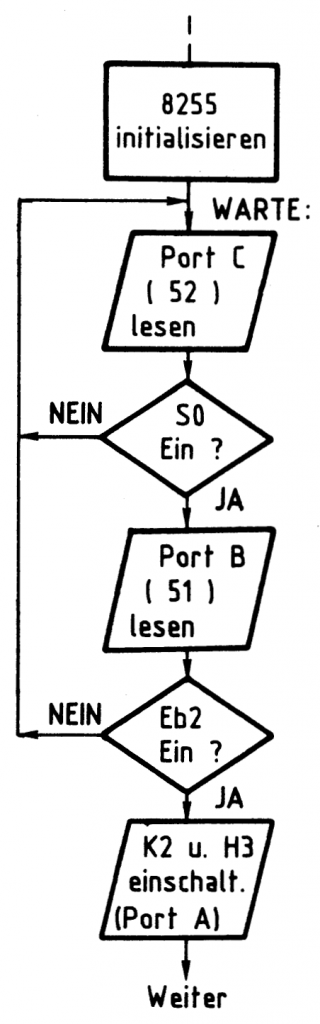

Der daran anschließende Programmausschnitt (Bild 14) bewirkt in der Anlage, dass Relais K2 und Signallampe H3 nur dann eingeschaltet werden, wenn Schalter S0 und Endschalter Eb2 geschlossen sind.

Bild 14: Befehlsfolge und Flußdiagramm zur Lösung der im Text genannten Aufgabenstellung; vgl. Bild 13.

| Label | Befehl | Kommentar |

|---|---|---|

| … | ||

| MVI A,08A | Steuerwort in den Akku laden | |

| OUT 053 | und an das Steuerwort-Register mit der Adresse 53H übergeben (Initialisierung des 8255) | |

| WARTE: | IN 052 | Port C lesen |

| ANI 010 | Maske zur Abfrage, ob SO geschl. | |

| JZ WARTE | Nein: Weiter abfragen | |

| IN 051 | Ja: Port B lesen | |

| ANI 04 | Maske zur Abfrage, ob Eb2 geschlossen ist | |

| JZ WARTE | Nein: Wieder Zustand S0 abfragen | |

| MVI A,04 | Ja: Ausgabewert zum Einsch. von K2 | |

| OUT 050 | in den Akku und an Port A ausgeben | |

| MVI A,08 | Ausgabewert zum Einsch. von H3 in | |

| OUT 052 | den Akku und an Port C ausgeben | |

| … |

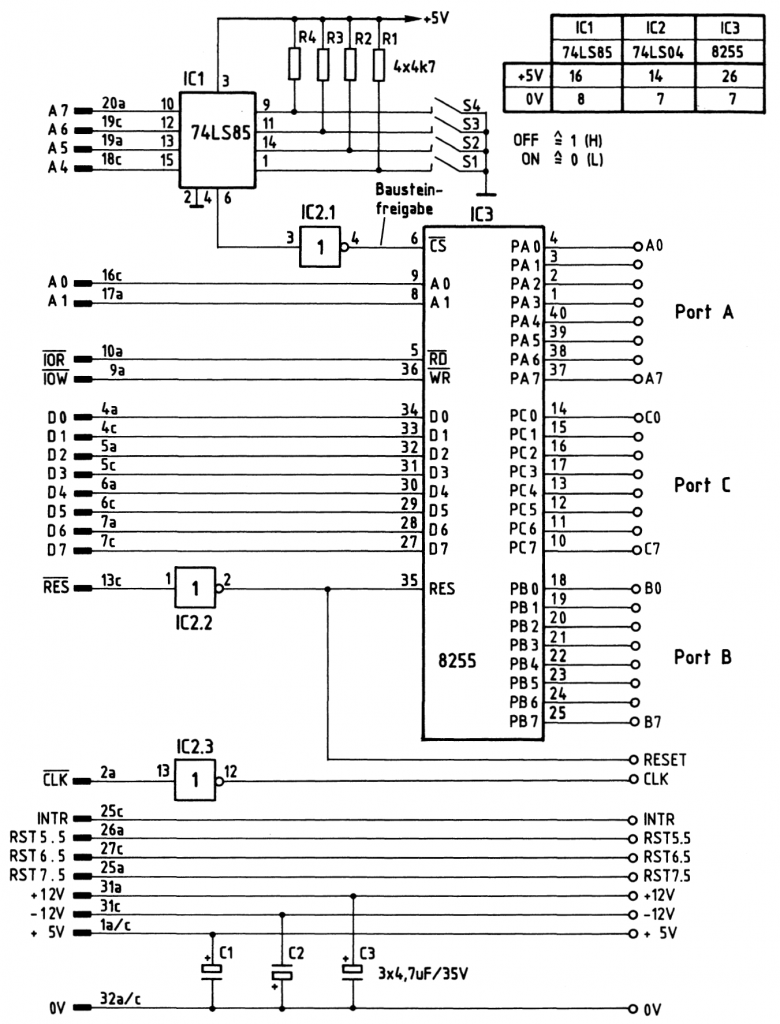

Die Schaltung der universell programmierbaren Parallel-Schnittstelle

Bild 15 zeigt den Stromlaufplan. Der Adressvergleicher wird gebildet durch IC1, die Widerstände R1 und R4 und die Schalter S1 bis S4. Durch L-Signal an Pin 6 wird der Schnittstellenbaustein 8255 bei Adressengleichheit freigegeben und kann über die Datenleitungen DO bis D7 Daten vom Prozessor empfangen oder an ihn ausgeben.

Die Adreßleitungen A0 und Al dienen zur Auswahl der im Inneren von IC3 vorhandenen Ports A bis C und des Steuerwort-Registers. Die Leitungen IOR und IOW lösen das Lesen bzw. Schreiben der Daten aus.

Das vom Prozessor gelieferte Reset-Signal (L-aktiv) wird durch IC2.2 invertiert, da IC3 zum Zurücksetzen ein H-Signal benötigt. Hierdurch werden beim Einschalten des Mikrocomputers alle Ports auf Eingabe geschaltet.

Jeder Ausgang des Schnittstellenbausteins 8255 (Port Abis Port C) kann mit einem Strom von etwa 1 mA belastet werden. Weitere Hinweise müssen den Datenbüchern der Bausteinhersteller entnommen werden.

In den nächsten Abschnitten werden drei Anwendungen der universell programmierbaren Parallel-Schnittstelle behandelt:

Drucker-Interface (ab Seite 367),

4fach-Zeitwerk (ab Seite 382),

EPROM-Programmierer (ab Seite 391).

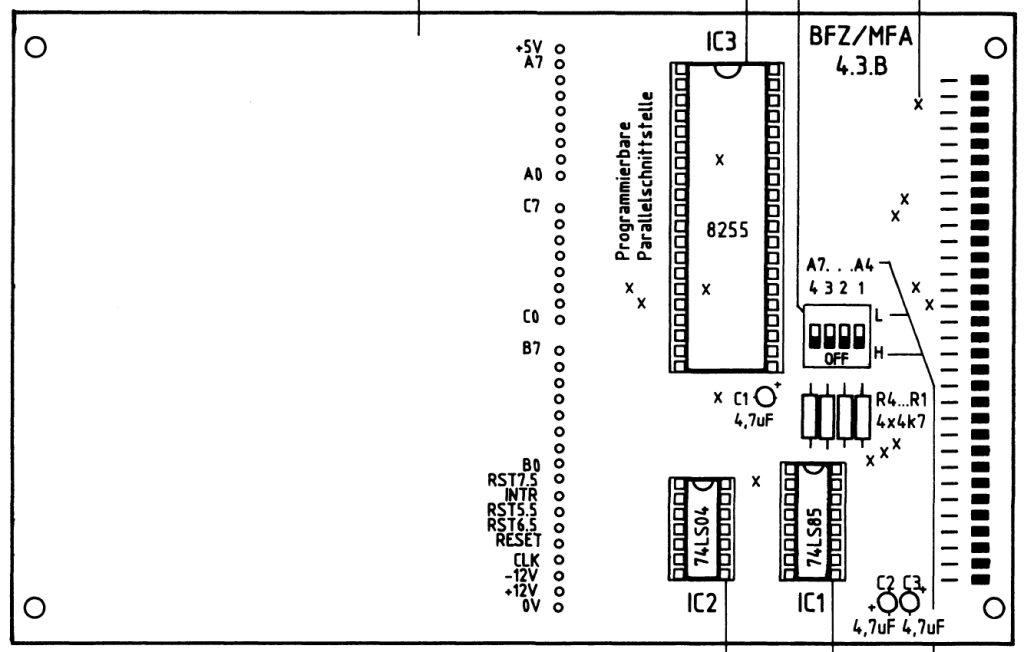

Stromlaufplan

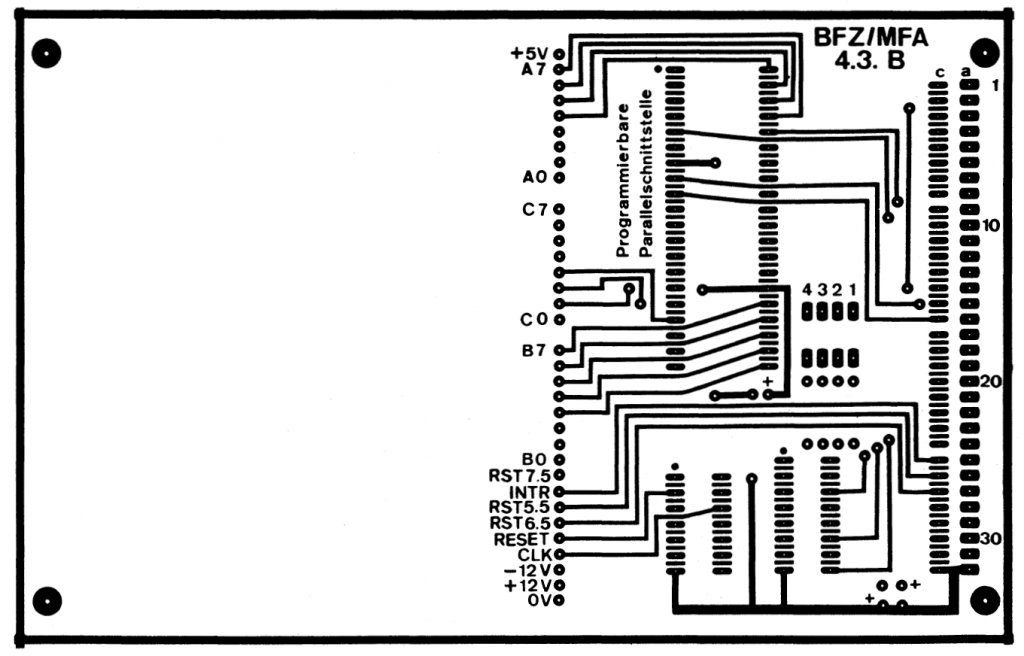

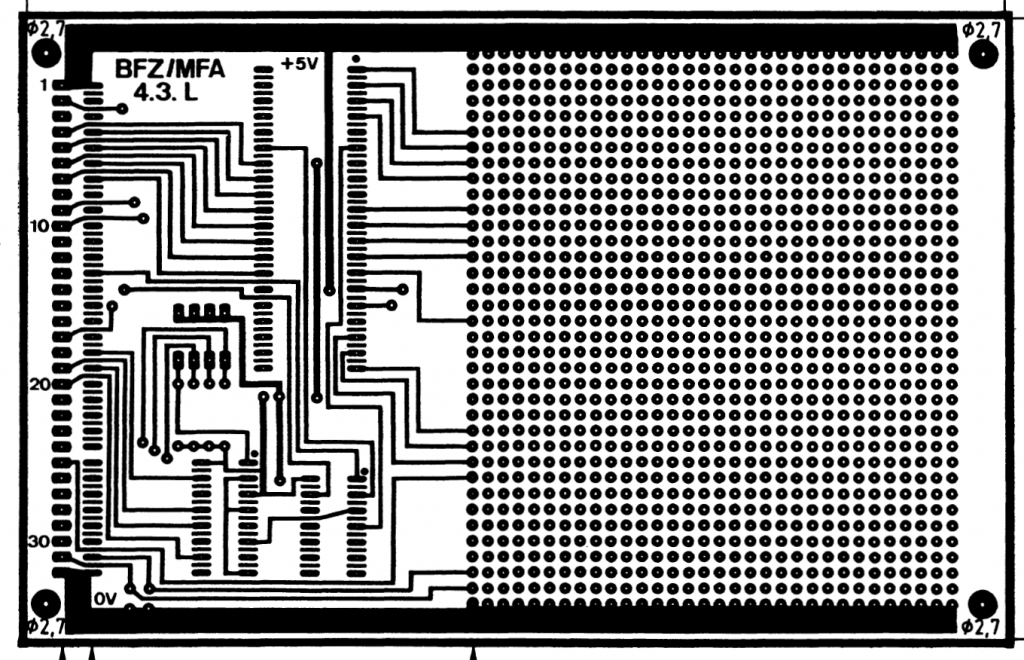

Layout

Bestückungsplan