Einleitung

Konzept der Ein/Ausgabekarte

Diese Zusatzkarte ist als Erweiterung zum Einplatinencomputer entwickelt worden. Der Einplatinencomputer wird in der Übung EPC ausführlich beschrieben. Im folgenden wird die Ein/Ausgabekarte beschrieben. Die Karte ist über eine 64polige Federleiste direkt an den Einplatinencomputer adaptierbar. Beide Systeme werden dabei von einer Betriebsspannung (5V) versorgt. Dadurch steht dem Anwender ein vollkommen autonomes Computersystem zur Verfügung, mit dem sich fast alle in der Praxis vorkommenden Problemstellungen lösen lassen.

Alle Ein – und Ausgänge der Karte können über Lötstecker und entsprechende Verbinder direkt belegt werden.

Es sind folgende Ein- bzw. Ausgänge vorhanden:

- TTL-kompatible Ein/Ausgabe

- Ein/Ausgabe über Optokoppler

- Analog-Eingabe und -Ausgabe

- über A/D- bzw. D/A-Wandler

Für die TTL-kompatible Ein/Ausgabe werden konventionelle Bausteine in LS-Technologie benutzt. Beide Kanäle sind für parallele 8Bit-Datenverarbeitung ausgelegt.

Die Ein/Ausgabe über Optokoppler erfolgt jeweils mit 4-fach Optokopplern. Auch hier erfolgt eine parallele Datenverarbeitung mit 8 Bit. Um eine vollkommene galvanische Trennung zu erreichen, wurden Anschlüsse für externe Betriebsspannungen vorgesehen. Dadurch können auch Systeme bedient werden, die mit Netzwechselspannung arbeiten.

Die Analog-Eingabe und -Ausgabe wurde mit 8 Bit-A/D- bzw. D/A-Wandlern realisiert. Der A/D-Wandler arbeitet nach dem Annäherungsverfahren und benötigt für eine Wandlung eine Zeit von 20 µs. Die Laufzeit des D/A-Wandlers für eine Wandlung beträgt zirka 800ns.

Die Bilder 1 stellt die kompletten Stromlaufpläne der Ein/Ausgabekarte dar. Sie müssen für die Funktionsbeschreibung und die Inbetriebnahme der Karte benutzt werden.

Stromlaufplan

Bild 1 – Stromlaufplan der Eingabekanäle

Adressierung der Ein- und Ausgabekanäle

In jedem Mikroprozessorsystem müssen den Eingabe- und Ausgabebaugruppen definierte Adressen zugeordnet werden können. damit sie gezielt ansprechbar sind. Den Ein- und Ausgabekanälen dieser Karte wurden je nach Typ gleiche Adressen zugeordnet. Die Adressierung ist fest „verdrahtet“ und kann nicht geändert werden. Zur Unterscheidung zwischen Eingabe und Ausgabe dienen die bei den SteuerIeitungen lOR und IOW.

Tabelle 1 stellt alle Adressen für Ein- und Ausgabekanäle dar.

| Adresse | IOR = L | IOW = L |

|---|---|---|

| Kanal | Adresse | |

| 00 | TTL-Eingabe | TTL-Ausgabe |

| 01 | OPTO-Eingabe | OPTO-Ausgabe |

| 02 | A/D-Wandler | D/A-Wandler |

TTL-kompatible Eingabe (IC14)

Der Baustein 74LS373 ist ein taktzustandsgesteuertes 8Bit-D-FIip-Flop. Der Takteingang ist H-aktiv, d. h, die internen D-Flip-Flops übernehmen immer dann die Eingangsdaten, wenn der Takteingang H-Pegel führt. Da es sich um einen Eingabebaustein handelt, sind die Ausgänge in Tristatetechnik ausgeführt. Die Ausgänge werden immer dann aktiv, wenn der Enable-Eingang L-Pegel führt. Tabelle 2 stellt die Wahrheitstabelle dieses Bausteins dar

| CLK | /EN | D | Q |

|---|---|---|---|

| L | L | H | t n-1 |

| L | H | H | hochohmig |

| H | L | H | H |

| H | H | H | hochomig |

Funktionsweise des D-FIip-Flops

Bild 2 zeigt den internen Aufbau des Bausteins 74LS373. Zur übersichtlicheren Darstellung wurde nur ein D-FIip-Flop gezeichnet.

Bild 2: Beschaltung des D-FI ip-Flops

Bei der folgenden Beschreibung wird davon ausgegangen, dass auf dem Adressbus die Adresse 00 anliegt!

Aus dem Stromlaufplan geht hervor, dass die beiden Steuereingänge parallelgeschaltet sind. Dadurch wird folgendes bewirkt: Führt die SteuerIeitung IOR H-Pegel , so Iiegt dieser Pegel eben falls an den beiden Steuereingängen des D-FIip-Flops an. Der Ausgang 1Q befindet sich dann im hochohmigen Zustand. Das D-FIip-Flop ist über den CLK-Eingang aktiviert und übernimmt ständig die Eingangsinformation, welche dann am internen Q-Ausgang anliegt. Führt die Steuerleitung IOR L-Pegel, so wird der gerade anliegende Eingangspegel gespeichert und zum Ausgang 1Q durchgeschaltet. Weitere Wechsel des Eingangspegels haben keinen Einfluss auf die Information am Ausgang, da das D-FIip-Flop gesperrt ist.

Dies ist wichtig, da der Mikroprozessor zu dem zuletzt beschriebenen Zeitpunkt die Information am Q-Ausgang des D-FIip-Flops1 ist. Würde das D-Flip-FIop nicht gesperrt, so könnte während

des Lesezyklus noch ein Signalwechsel stattfinden, was keinen eindeutigen Pegel auf dem Datenbus zur Folge hätte. Tabelle 3 zeigt die Wahrheitstabelle des Bausteins im Zusammenhang mit dem Adressbus und der Steuerleitung IOR.

| Adresse | IOR | CLK/EN | Wirkung |

|---|---|---|---|

| 00 | H | H | D-FF aktiv, Ausgang 1G hochohmig |

| 00 | L | L | D-FF gesperrt, Ausgang 1Q niederohmig |

| 01 | X | H | Baustein inaktiv |

| 02 | X | H | Baustein inaktiv |

Optokoppler-Eingabe (IC15 und IC16)

Optokoppler bieten den Vorteil, dass zwischen Ein- und Ausgängen eine galvanische Trennung herrscht. Als Sender dient eine Leuchtdiode, deren abgestrahItes Licht den Empfänger, einen Fototransistor, ansteuert. Beide Bauelemente sind zum Schutz vor Fremdlicht in einem Iichtdichten Gehäuse untergebracht. Bei der hier vorliegenden Karte werden aus Platzgründen zwei Vierfach-Optokoppler ILQ30 verwendet. Die Leuchtdioden (Sender) werden durch Konstantstromquellen mit einem Nennwert von 5,5 mA gespeist. Das hat den Vorteil, dass die Eingangspegel zwischen 5V und 30 V Iiegen können, ohne das sich die Leuchtstärke der Dioden ändert. Die Eingangsspannung muss zwischen dem jeweiligen Eingang und dem Anschluss EXT.GND2 angelegt werden. Ein offener Eingang erzeugt bei diesen Bausteinen einen L-Pegel am Ausgang, da die Signale am Emitter der Fototransistoren (Empfänger) abgegriffen werden.

Bild 3 zeigt die Beschaltung eines Optokopplers.

Bild 3: Beschaltung der Optokoppler für die Eingabe

Da die Optokoppler keine Tristate-Ausgänge besitzen, wurde ihnen ein achtfach-D-FIip-Flop 74LS373 nachgeschaltet, dessen Funktionsweise auf den Seiten 5 und 6 beschrieben wurde. Für diesen Optokoppler wurde ein Typ gewählt, dessen Stromübertragungsverhältnis lc/IF > 100 ist. Die relativ hohe Kollektor-Emitter- Sättigungsspannung von 0,8 V wirkt sich bei der Beschaltung des Optokopplers nicht aus, da die Eingangsspannung für den nachgeschalteten Baustein 74LS373 am Emitterwiderstand abgegriffen wird.

A/D-Wandler (IC12)

Der A/D-Wandler setzt einen analogen Eingangsspannungswert, der zwischen den Anschlüssen „Analog IN“ und „GND“ anliegt, in ein 8Bit-Datenwort um. Für die Umwandlung benötigt der Baustein ein Taktsignal, das aus dem Mikroprozessortakt (2 MHz) des EinpIatinencomputers erzeugt wird und eine Frequenz von 500 kHz hat. Die Frequenzteilung erfolgt durch IC11. Für eine Umwandlung eines Eingangsspannungswertes in ein entsprechendes Datenwort benötigt der A/D-Wandler zehn Taktzyklen, was einer Wandlungszeit von 18 µs entspricht. Außerdem wird neben der positiven Betriebsspannung eine negative Spannung benötigt. Um den Anschluss einer externen Betriebsspannung zu sparen, ist auf der Karte ein Spannungswandler eingesetzt.

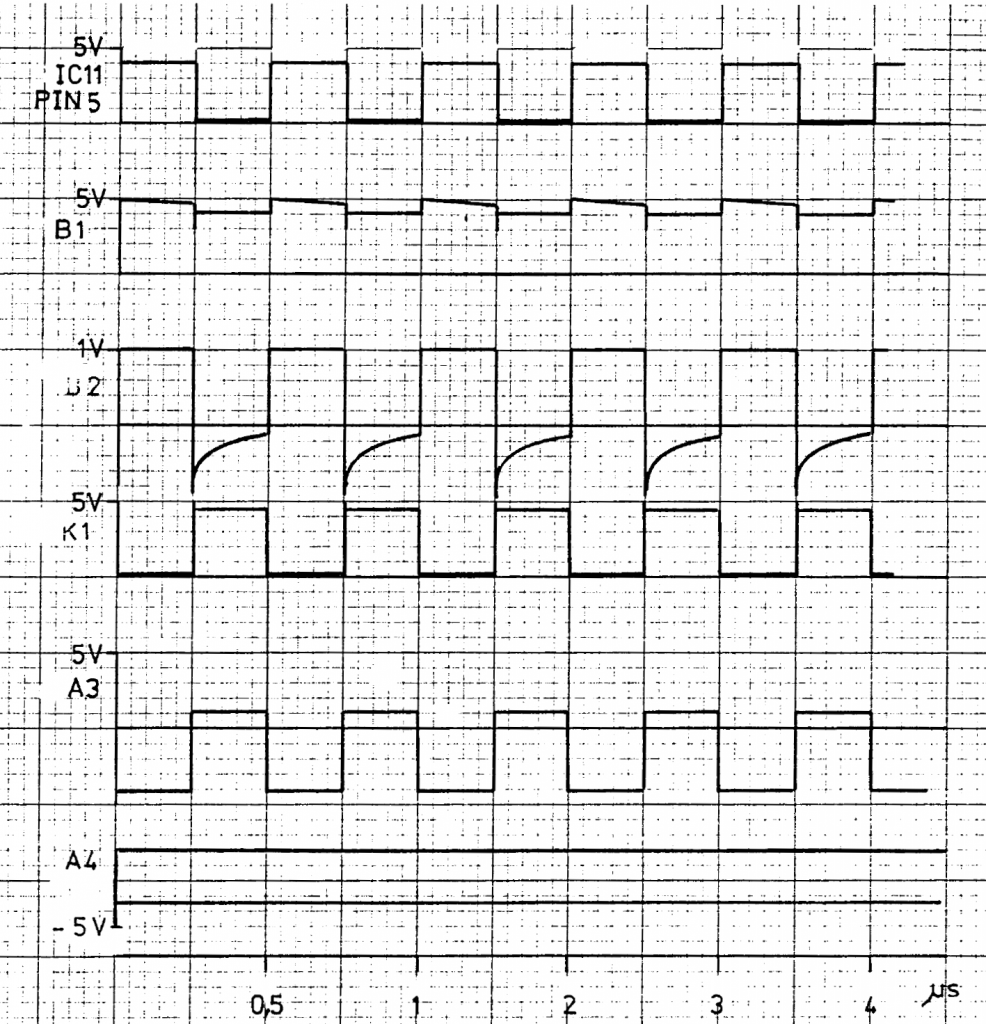

Spannungs-Zeit-Diagramm für die A/D-Wandlung

Für den Beginn der Umwandlung benötigt der A/D-Wandler einen Startimpuls am PIN 4 (SC= Start Conversion). Mit der darauf folgenden negativen Taktflanke beginnt die Umwandlung, welche nach neun Taktzyklen beendet ist. Das so erzeugte 8 Bit-Datenwort wird intern gespeichert und kann nur dann gelesen werden, wenn der EN-Anschluss H-Pegel führt, da die Ausgänge ansonsten hochohmig

bleiben. Der Startimpuls wird durch das IOW-Signal des Mikroprozessors erzeugt (OUT-Befehl). Nach einer Wartezeit von 18 µsec nimmt der BUSY-AnschIuss des Bausteins H-PegeI an , wodurch angezeigt wird , dass die UmwandIung beendet ist . Mit HiIfe des IOR-Signals (IN-Befehl) wird der EN-Anschluss mit H-Pegel beschaltet, wodurch dass 8-Bit-Datenwort gelesen wird. Bi I d 4 zeigt den beschriebenen Vorgang im Spannungs-Zeit-Diagramm.

Bi Id 4: Spannungs-Zeit-Diagramm für die A/D-Wandlung

Erzeugung der negativen Betriebsspannung

Die negative Betriebsspannung wird durch die Transistoren V1 und V2 erzeugt. Führt das Taktsignal des A/D-Wandlers L-Pegel, dann ist V1 leitend und lädt den Kondensator C2 auf einen Spannungswert auf, der sich nach der FormeI Uc = Ub – Ufv3 – Uce1 berechnet. Führt das Taktsignal H-Pegel, so ist V2 leitend. Die Diode V3 verhindert eine Entladung des Kondensators über den leitenden Transistor. Gleichzeitig ist V4 leitend und der Kondensator C3 wird auf eine Spannung von Uc3= – (Uc2 – Ufv4 – Uce2) aufgeladen. Die so erzeugte Spannung hat einen Wert von ca. – 3,5 Volt.

TTL-kompatible Ausgabe (IC8)

Die TTL-Ausgabe erfolgt ebenfalls über D-FIip-Flops. Hier sind aber gegenüber der Eingabe keine Tri-State-Ausgänge erforderlich. Die Flip-Flops können allerdings über den Eingang R zurückgesetzt werden. Außerdem sind sie im Gegensatz zur TTL-Eingabe nicht zustandsgesteuert, sondern die Eingangsinformation (vom Datenbus) wird mit der positiven Taktflanke in die D-Flip-Flops übernommen. Tabelle 4 stellt die Wahrheitstafel dieses Bausteins dar.

| CLK | R | D | Q |

|---|---|---|---|

| L | L | X | L |

| L | H | X | t n-1 |

| H | H | H | H |

| H | H | L | L |

Ausgabe über Optokoppler (IC4 und IC5)

Für die Ausgabe werden ebenfalls vierfach-Optokoppler verwendet. Es handelt sich dabei um Bausteine, deren Fototransistoren eine möglichst geringe Kollektor-Emitter-Sättigungsspannung aufweisen. Die Betriebsspannung für die Transistoren wird über die Anschlüsse EXT.Vcc und EXT.GND1 zugeführt. Die Fotodioden werden bei L-PegeI am Ausgang von IC7 (74LS273) leitend, wodurch die Fototransistoren ebenfalls leitend werden, was an den Optokoppler-Ausgängen L-Pegel zur Folge hat. Bild 5 zeigt die Beschaltung eines Optokopplers. Für diese Optokoppler wurde ein Typ mit einem Stromübertragungsverhältnis von )25 gewählt

Bild 5: Optokoppler-Ausgabe

D/A-Wandler (IC6)

Der DIA-Wandler setzt ein 8Bit-Datenwort an seinen Eingängen in einen anlogen Spanungswert am Ausgang um. Das Datenwort wird in internen D-FIip-Flops gespeichert. Die Übernahme in die D-FIip-Flops erfolgt bei L-Pegel am EN-Eingang. Ein Rücksetzen der FIip-Flops ist nur möglich, wenn das Datenwort 00000000 angelegt wird und der EN-Eingang L-Pegel annimmt.

Um einen möglichst geringen Ausgangswiderstand der Analogausgabe zu erhalten, wurde dem D/A-Wandler ein Operationsverstärker nachgeschaltet, der im nicht invertierenden Betrieb arbeitet.

Dadurch wird der relativ hohe Ausgangswiderstand des D/A-Wandlers in den geringen Ausgangswiderstand des Operationsverstärkers umgewandelt. Außerdem kann durch die Beschaltung des Operationsverstärkers eine Spannungsverstärkung > 1 eingestellt werden, wodurch die Ausgangsspannung des D/A-Wandlers verstärkt wird.

Bei der D/A-Wandlung muss beachtet werden, daß der Baustein ZN 428 für die Umwandlung eine Zeit von zirka 800 ns benötigt.

Außerdem benötigt der Operationsverstärker eine bestimmte Zeit für die Umsetzung seines Eingangsspannungswertes. Die Bilder auf der nächsten Seite zeigen die Spannungs-Zeit-Diagramme für zwei D/A-Wandlungen. Im Bild 6 ändert sich die Ausgangsspannung des D/A-Wandlers (D/A-OUT=IC6 PIN 5) und die Ausgangsspannung des Operationsverstärkers (ANALOG-OUT= IC3 PIN 6) vom kleinsten zum größten Wert, im BiId 6 ändern sich die Ausgangsspannungen in umgekehrter Richtung. Aus den Diagrammen ist ersichtlich, dass der Operationsverstärker bei einer Spannungsänderung vom kleinsten zum größten Wert eine zusätzliche Zeitverzögerung erzeugt.

Bild 006 – A/D-Wandlung

Flußdiagramm für den Arbeitsablauf

Hinweis: Auf den folgenden Seiten wird die EPC-Ein/Ausgabe kurz als I/O-EPC bezeichnet. Die zur Inbetriebnahme erforderliche Adapterkarte als I/O-Adapter!

Inbetriebnahme

In dieser Übung werden Sie die Ein/Ausgabekarte zum Einplatinencomputer aufbauen und in Betrieb nehmen. Falls Sie bereits eine fertig aufgebaute Karte erhalten haben, besteht Ihre Aufgabe darin, sie zu prüfen und in Betrieb zu nehmen.

In dieser Übung werden Sie die I/O-Adapaterkarte zur Ein/Ausgabekarte aufbauen und überprüfen. Falls Sie bereits eine fertig auf gebaute Karte erhaIten haben, besteht Ihre Aufgabe darin, sie zu überprüfen.

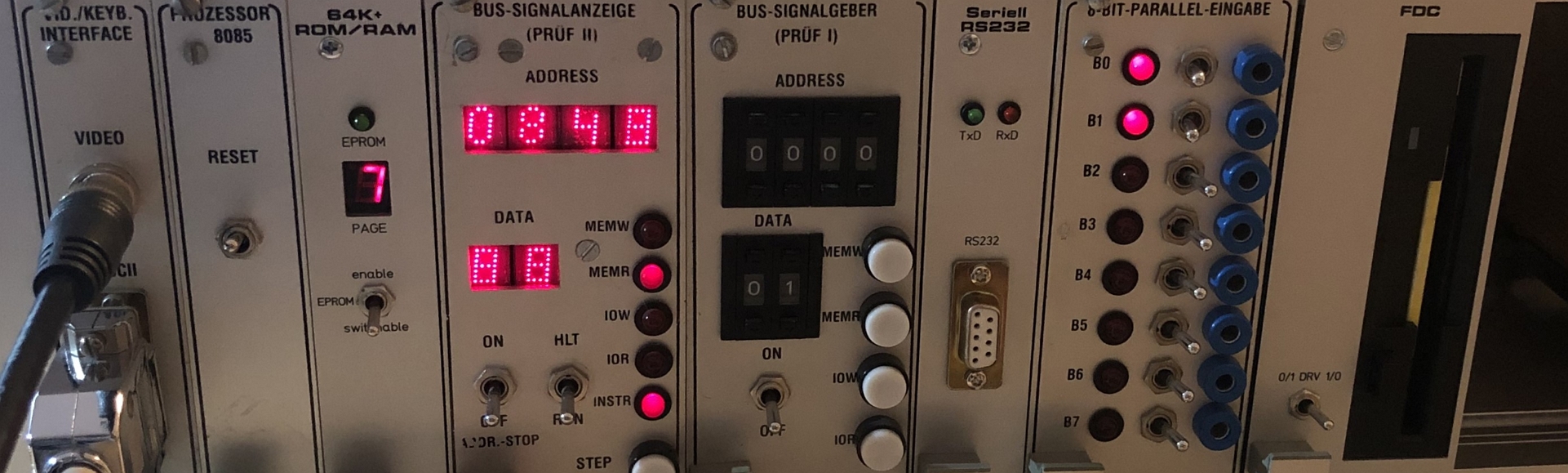

Mit Hilfe der folgenden Seiten werden Sie die Baugruppe I/O-EPC Betrieb nehmen. Die Karte wird mit HiIfe des MFA-Systems statisch und dynamisch in Betrieb genommen.

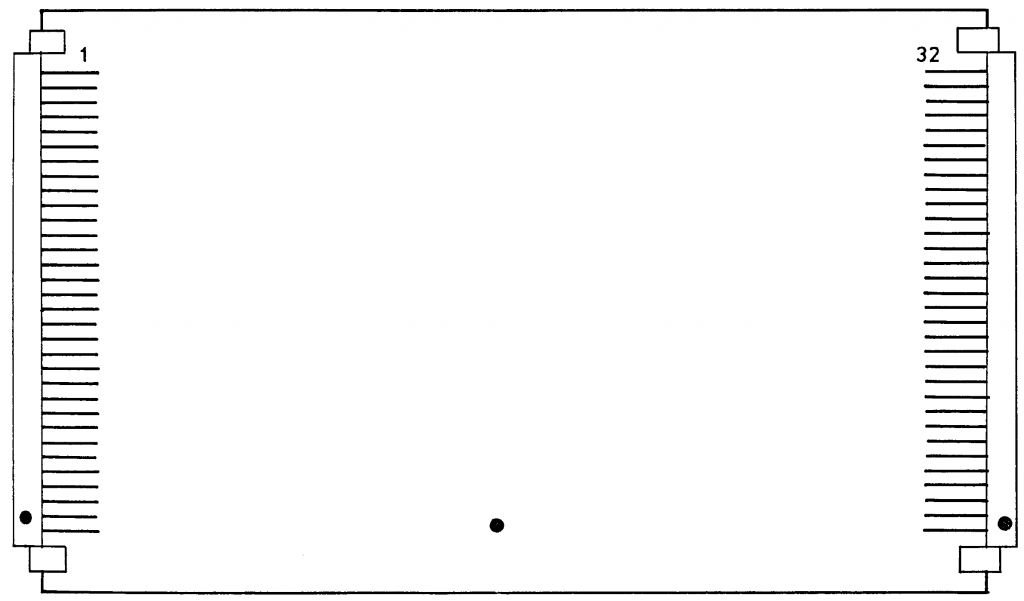

Für die Ein/Ausgabekarte zum Einplatinencomputer benötigen Sie eine zweiseitig kupferkaschierte und durchkontaktierte Leiterplatte mit der Bezeichnung I/O-EPC.

EPC-Ein/Ausgabe-Platine

Lötseite

Bestückungsseite

Die folgende Abbildung zeigt das Layout der Bestückungsseite

Bestückungsplan

Bestückungsplan der Ein/Ausgabekarte

Bestücken Sie die Leiterplatte mit Hilfe des Bestückungsplans, der Stückliste und der Bauteillliste.

Vorher sollten Sie die Leiterplatte mit HiIfe einer Lupe auf Risse und Kurzschlüsse untersuchen und Fehler beseitigen.

I/O-Adapterplatine

Für die I/O-Adapterkarte benötigen Sie eine zweiseitig kupferkaschierte und durchkontaktierte Leiterplatte mit der Bezeichnung I/O-Adapter.

I/O-Platine – Lötseite

I/O-Platine – Bestückungsseite

Die folgende Abbildung zeigt das Layout der Bestückungsseite der I/O-Adapterplatine

I/O-Platine – Bestückungsplan

Bestückungsplan I/O-Adapterkarte

Bestücken Sie die Leiterplatte der I/O-Adapterkarte mit HiIfe des Bestückungsplans und der Stückliste.

Vorher sollten Sie die Leiterplatte mit einer Lupe auf Risse und Kurzschlüsse untersuchen und Fehler beseitigen.

Zur Funktionsprüfung der I/O-Adapterkarte benötigen Sie die auf dieser Seite abgebildete Schemazeichnung. Kontrollieren Sie vor der Funktionsprüfung die Leiterplatte auf Kurzschlüsse, die durch

Lötspritzer entstanden sein können.

Schemazeichnung der Adapterkarte

Für die Funktionsprüfung der I/O-Adapterkarte benötigen Sie einen Durchgangsprüfer mit akustischer Anzeige. Kontrollieren Sie jetzt die einzelnen Leiterbahnen zwischen den entsprechenden Anschlüssen der Messerleisten auf Durchgang. Danach sollten Sie jeweils zwei benachbarte Leiterbahnen auf Kurzschluss überprüfen.

Sichtkontrolle der Ein-/Ausgabekarte

Für die Sichtkontrolle sowie für die Inbetriebnahme muß der Stromlauf- und Bestückungsplan bereit liegen. Kontrollieren Sie alle Lötstellen auf der Leiterbahnseite und achten Sie auf Kurschlüsse, die beim Löten eventuelI zwischen den Leiterbahnen entstanden sein könnten.

Achten Sie bei der Kontrolle der Bauteile auf folgende Punkte:

- Sind alle Widerstände mit ihrem richtigen Wert eingebaut?

- Sind alle EIko’s richtig gepoIt?

- Der Elko C10 muss eine Spanungsfestigkeit von 35 Volt haben

- Die IC’s dürfen nicht gesteckt sein

Bestücken Sie das MFA-System, welches mit NetzteiI und Spannungsregelung ausgerüstet sein muss, mit folgenden Einschüben:

- Bus-Signalgeber

- Bus-Signalanzeige

- I/O-Adapterkarte

- Prozessorkarte CPU 8085

Stecken Sie die Ein/Ausgabekarte auf den Adapter und schalten Sie die Betriebsspannung des Systems ein. Kontrollieren Sie jetzt die Spannungsversorgung an allen IC-Sockeln und tragen Sie Ihre Messergebnisse in die Tabelle auf der nächsten Seite ein.

Der Schalter „HLT/RUN“ der Bus-Signalanzeige muss auf „HLT“ stehen!

Messwerttabelle zur Überprüfung der Betriebsspannung

Ausgabekanäle

| TYP | IC1 | IC2 | IC3 | IC4 | IC4 | IC5 | IC6 | IC7 | IC8 |

|---|---|---|---|---|---|---|---|---|---|

| Pos. Versorgungs- Spannung | | | | | | | | | |

| Masse an Pin | | | | | | | | | |

| Ub | | | | | | | | | |

| GND | | | | | | | | | |

Eingabekanäle

| TYP | IC9 | IC10 | IC11 | IC12 | IC13 | IC14 | IC15 | IC16 |

|---|---|---|---|---|---|---|---|---|

| Pos. Versorgungs- Spannung | | | | | | | | |

| Masse an Pin | | | | | | | | |

| Ub | | | | | | | | |

| GND | | | | | | | | |

Wenn die Spannungsversorgung an allen IC-Sockeln richtig ist, können Sie das MFA-System ausschalten und die Ein/Ausgabekarte mit allen ICs bestücken.

Der Operationsverstärker (IC3) und der A/D-Wandler (IC12) benötigen neben der positiven auch eine negative Versorgungsspannung. Überprüfen Sie deshaIb mit HiIfe eines Oszilloskops die Erzeugung der negativen Betriebsspannung. Machen Sie sich vorher die Funktionsweise der Schaltung mit Hilfe von Seite 9 noch einmal klar. Tragen Sie Ihre Messergebnisse in die Koordinatensysteme auf dieser Seite ein.

Messen Sie folgende Spannungen:

- IC11 PIN 12= f (t)

- Uso, = f (t)

- Uso2 = f (t)

- Uco, 12= f (t)

- UAV3 = f (t)

- UAV4 = f (t)

Messen Sie jetzt mit einem Vielfachmessinstrument die Spannung an folgenden Punkten:

Minuspol von

C3: U= ____________

IC12 (PIN5) U= ____________

IC3 PIN4 U= ____________

ERGEBNISSE ZU DEN MESSUNGEN VON SEITE 29 UND 30

HINWEIS ZU DEN MESSUNGEN

Die Triggerung des Oszilloskops erfolgt auf der positiven Flanke der Spannung an IC11 PIN12.

Die Gleichspannungen müssen ungefähr folgende Werte aufweisen:

- Minuspol von C3= -3,3V bis -3,8V

- IC3 PIN4= -3,3V bis -3,8V

- IC12 PIN5 = – 300mV bis -800mV

Wenn die vorhergehenden Messungen keine Fehler aufwiesen, können Sie jetzt die Adress- und die Datenleitungen überprüfen Entfernen Sie dazu nach Abschalten der Betriebsspannung die Prozessorkarte CPU 8085-aus dem MFA-System. Auf der Ein/Ausgabekarte werden nur die Adressleitungen A0 und A1 benutzt.

Stellen Sie mit HiIfe des Bussignalgebers die in folgender Tabelle angegebenen Adressen ein und überprüfen Sie mit der Bus- Signalanzeige die richtige Übertragung der eingestellten Adresssignale. Mit einem Logiktester können sie die Pegel an den einzelnen IC-Anschlüssen messen. Beachten Sie dabei die invertierende Wirkung von IC1 und IC10.

Messwerttabel le zur Überprüfung der Adressleitungen

Eingabekanäle

| Adress Signalgeber | Adress Signalanzeige | IC10 Pin 9 | IC10 Pin 8 | IC10 Pin 11 | IC10 Pin 10 | IC11 Pin 1 | IC11 Pin 13 | IC11 Pin 3 | IC11 Pin 5 | IC11 Pin 9 | IC11 Pin 10 |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 0000 | A0 L A1 L | L | H | L | H | L | L | H | L | L | H |

| 0001 | A0 H A1 L | H | L | L | H | H | L | L | L | H | H |

| 0002 | A0 L A1 H | L | H | H | L | L | H | H | H | L | L |

Ausgabekanäle

| Adress Signalgeber | Adress Signalanzeige | IC10 Pin 9 | IC10 Pin 8 | IC10 Pin 11 | IC10 Pin 10 | IC11 Pin 1 | IC11 Pin 13 | IC11 Pin 3 | IC11 Pin 5 | IC11 Pin 9 | IC11 Pin 10 |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 0000 | A0 L A1 L | L | H | L | H | L | L | H | L | L | H |

| 0001 | A0 H A1 L | H | L | L | H | H | L | L | L | H | H |

| 0002 | A0 L A1 H | L | H | H | L | L | H | H | H | L | L |

Überprüfung der Datenleitungen

Die Datenleitungen der Ein/Ausgabekarte werden ebenfalls mit Bus-Signalgeber und -anzeige überprüft. Zusätzlich werden Messungen mit dem Logiktester an den einzelnen IC’s durchgeführt. Dabei kann nur der interne Datenbus der Karte überprüft werden. Eine Überprüfung der Ein- und Ausgabedaten an den Lötnägeln der Karte erfolgt zu einem späteren Zeitpunkt.

Eingabekanäle

Ausgabekanäle

Überprüfen Sie die Richtigkeit Ihrer Messergebnisse. Falls bei einigen Messungen keine Übereinstimmung vorhanden ist, beseitigen Sie den entsprechenden Fehler auf der Karte

Überprüfung der Adressdecodierung

Wie auf Seite 5 schon beschrieben , ist die Adressdecodierung fest verdrahtet. Die einzelnen Kanäle haben je nach Typ die gleiche Adresse, wobei die beiden Steuerleitungen IOR und IOW die Unterscheidung zwischen Eingabe und Ausgabe ermöglichen.

Für die folgenden Messungen benötigen Sie das MFA-System mit den gleichen Einschüben wie bei den vorhergegangenen Messungen.

Achten Sie darauf, dass die CPU-Karte nicht im System steckt!

Adressdecodierung der Eingabekanäle Stellen Sie die in der folgenden Tabelle angegebenen Adressen am

Bus-Signalgeber ein und notieren Sie die an der Bus-Signalanzeige angezeigte Adresse. Mit einem Logiktester messen Sie an den vorgegebenen Anschlüssen der einzelnen Bausteine. Die Angabe IOR = H bedeutet, dass die entsprechende Taste des Bus-SignaIgebers nicht gedrückt ist; IOR = L bedeutet, dass die entsprechende Taste gedrückt ist.

Adressdecodierung der Ausgabekanäle

Diese Überprüfung erfolgt mit den gleichen Mitteln wie auf Seite

Zu beachten ist bei diesem Übungsteil, daß die Steuerleitung IOW und nicht die Steuerleitung IOR aktiviert werden muss.

Eingabekanäle

Ausgabekanäle

Dynamische Funktionsprüfung

Für die dynamische Funktionsprüfung muss das MFA-System mit folgenden Einschüben bestückt werden:

- Prozessorkarte CPU 8085

- 8 KByte EPROM mit MAT85 (Basisadresse 0000)

- 8 KByte RAM (Basisadresse E000)

- Video-Interface

Die Einschübe „Bus-Signalgeber“ und „Bus-Signalanzeige“ können Sie entfernen.

Außerdem benötigen Sie:

- Tastatur

- Monitor

Schalten Sie die Betriebsspannung ab und bestücken Sie das System mit den oben genannten Einschüben.

Verbinden Sie danach auf der Ein-Ausgabekarte die acht Anschlüsse 0-7 der TTL-Ausgabe mit den entsprechenden Anschlüssen der TTL-Eingabe.

Danach können Sie die Betriebsspannung wieder einschalten. Sie müssen jetzt zuerst mit Hilfe des Assemblers ein Prüfprogramm für die TTL-Ein/Ausgabe schreiben. Rufen Sie deshalb den Assembler

auf und geben Sie das folgende Programm ab der Adresse E000 ein:

ANF: MVI A, 55 ;Accu mit 55H laden

MOV C,A ;Wert retten

OUT 00 ;55H ueber TTL-Ausgabe ausgeben

IN 00 ;TTL-Eingabe lesen

CMP C ;ausgegebener Wert=gelesener Wert?

JNZ STOP ; NEIN !

MVI A, 0AA ;Ja, Accu mit AAH laden

MOV C,A ;Wert retten

OUT 00 ;AAH ueber TTL-Ausgabe ausgeben

IN 00 ;TTL-Eingabe lesen

CMP C ;ausgebener Wert=gelesener Wert?

JNZ STOP ;NEIN!

JMP ANF ;Ja, zurück zum Anfang

STOP: HLT ; Fehler!: Prozessor haelt an!

Durch das auf Seite 38 aufgelistete Programm werden erstens die beiden Bausteine IC8 und IC14 auf richtige Funktion überprüft. Zweitens werden die Datenleitungen auf Unterbrechung bzw. KurzschIuss überprüft. Starten Sie das Programm mit dem GO-Kommando und messen Sie mit Hilfe des Oszilloskops folgende Signale.

Tragen Sie ihre Messergebnisse in die Koordinatenkreuze auf der nächsten Seite ein.

TTL-Ausgabe

- UA0 = f ( t)

- UA1 = f ( t)

- UA2 = f ( t)

- UA3 = f ( t)

- UA4 = f ( t)

- UAS = f ( t)

- UA6 = f ( t)

- UA7 = f ( t)

- IC8 PIN11 = f(t)

- IC10 PIN12= f ( t)

Als Bezugspunkt für alle Messungen können Sie die GND-Anschlüsse der Analog-Ein/Ausgabe benutzen.

Bei richtiger Funktion beider Bausteine müssen sich an allen Anschlüssen (0-7) rechteckförmige Spannungen ergeben, wobei zwei benachbarte Leitungen immer gegenphasige Verläufe aufweisen.

HINWEIS ZU DEN MESSUNGEN

Die Triggerung des Oszilloskops erfolgte auf der Ausgabeleitung 0. Die Signale an IC8 PIN11 und IC10 PIN12 entsprechen den Steuersignalen IOW und IOR.

Dynamische Funktionsprüfung der Optokoppler-Ein/Ausgabe

Schalten Sie die Betriebsspannung des Systems ab. Benutzen Sie die acht Leitungen zur Verbindung der Punkte 0-7 der Optokoppler-Ausgabe mit den entsprechenden Punkten der Optokoppler-Eingabe. Danach schließen Sie eine externe Gleichspannungsquelle von 15V an die Anschlüsse „EXT.Vcc“ und „EXT.GND1“ an. Außerdem müssen Sie die Anschlüsse „EXT.GND1“ und „EXT.GND2“ miteinander verbinden. Sie müssen jetzt mit Hilfe des Assemblers ein neues Programm eingeben, das zwar im Prinzip die gleiche Wirkung wie das auf Seite 38 hat. Es muss bei der Überprüfung der Optokoppler aber eine Zeitverzögerung zwischen Ausgeben und Lesen des Datenwortes eingefügt werden, da die Optokoppler wesentlich größere Schaltverzögerungszeiten aufweisen als die TTL-Bausteine. Geben Sie, beginnend ab der Adresse E000, folgendes Programm ein:

ANF: MVI A, 55 ;Accu mit 55H laden

MOV C,A ;Wert retten

OUT 01 ;55H ausgeben

CALL ZEIT ; Zeitverzoegerung

IN 01 ;Opto-Eingabe lesen

CMP C ;gelesener Wert=ausgegebener Wert

JNZ STOP ; Nein !

MVI A,0AA ;Accu mit AAh laden

MOV C,A ;Wert retten

OUT 01 ;AAH ausgeben

CALL ZEIT ;Zeitverzoegerung

IN 01 ;Opto-Eingabe lesen

CMP C ;gelesener Wert=ausgegebener Wert

JNZ STOP ;NEIN!

JMP ANF ;JA, zurueck zum Anfang

STOP: HLT ;FEHLER!: Prozessor haelt an

ZEIT: MVI B,8F ; Zeitverzoegerung

Z1: DCR B

JNZ Z1

RET

Messen Sie jetzt die Signale an den Anschlüssen 0 – 7 der Optokoppler-Ausgabe. Benutzen Sie für die Zeichnungen die Koordinatenkreuze auf der nächsten Seite.

HINWEIS ZU DEN MESSUNGEN

Der Konstantstrom von 5,5 mA der Optokoppler-Eingabe stellt für die hochohmigen Kollektorwiderstände der Optokoppler-Ausgabe eine hohe Belastung dar. Bedingt dadurch erreicht die Ausgangsspannung nur einen Wert von ca. 2 Volt.

Funktionsprüfung des D/A-Wandlers

Im ersten Schritt werden der Minimal- und der Maximalwert der Ausgangsspannung des D/A-Wandlers gemessen. Dazu geben Sie folgendes Programm ab der Adresse E000 ein:

ANF: MVI A,00 ;Accu mit 00 laden

OUT 02 ;Wert wandeln

ANF1: CALL 0043 ;Tastatur lesen

CPI 20 ;Space-Taste betaetigt?

JNZ ANF1 ;Nein, Tastatur erneut lesen

MVI A,0FF ;Accu mit FFH laden

OUT 02 ;Wert wandeln

ANF2: CALL 0043 ;Tastatur abfragen

CPI 20 ;Space-Taste betaetigt?

JNZ ANF2 ;Nein, Tastatur erneut lesen

JMP ANF ;Ja, zum Anfang zurueck

Das Programm wirkt folgendermaßen:

Im ersten Schritt wird das Datenwort 00 umgewandelt. Danach erfoIgt eine Abfrage der Tastatur. SoIange auf der Tastatur die Space-Taste nicht betätigt wird, kann am Ausgang des D/A-Wandlers der minimale Spannungswert gemessen werden. Wird die Space-Taste betätigt, so wird das Datenwort FF umgewandelt, und am Ausgang des DIA-Wandlers kann der maximale Spannungswert gemessen werden. Wird die Space-Taste erneut betätigt, so beginnt der Vorgang wieder von vorn. Starten Sie das Programm mit dem GO-Kommando und messen Sie mit einem Vielfachinstrument die minimale und die

maximale Ausgangsspannung des DIA-Wandlers.

Die gemessenen Spannungen müssen ungefähr folgende Werte haben:

- UAmin: 0,3 VoIt

- UAmax: 2,5 VoIt

Jetzt muss der Operationsverstärker IC3 noch abgeglichen werden, damit am Analogausgang der Karte definierte Minimal- und Maximalspannungen auftreten. Für den Operationsverstärker muss ein „OFFSET-ABGLEICH“ und ein „VERSTÄRKUNGS-ABGLEICH“ durchgeführt werden. Starten Sie das o.g. Programm erneut ab der Adresse E000 und stellen Sie mit R28 am Analogausgang eine Spannung von 0 Volt ein. Nach Betätigung der Space-Taste stellen Sie mit R29 eine Spannung von 3,06 Volt ein. Die beiden Einstellungen müssen mehrmals hintereinander wiederholt werden, da sie sich gegenseitig beeinflussen.

Dynamische Funktionsprüfung des DIA-Wandlers

Bei der dynamischen Funktionsprüfung werden durch den DIA-Wandler fortlaufend alle 256 Bit-Kombinationen umgewandelt. Dazu müssen Sie folgendes Programm ab der Adresse E000 eingeben:

MVI A, 00 ;Accu mit 00H laden

ANF: OUT ;D/A-Wandlung

INR A ;Accu incrementieren

JMP ANF ;naechst hoeheren Wert wandeln

Starten Sie das Programm mit dem GO-Kommando und messen Sie mit dem Oszilloskop den Spannungsverlauf am Analogausgang der Karte. Den Spannungsverlauf zeichnen Sie in das Koordinatenkreuz auf dieser Seite ein.

HINWEIS ZU DER OBIGEN MESSUNG

Die Ausgangsspannung muss einen sägezahnförmigen Verlauf haben. Die Minimal- und die Maximalwerte müssen den Spannungswerten des Operationsverstärkerabgleichs entsprechen. Die Zeitablenkung des Oszilloskops muss auf 0,5ms/Div eingestellt sein.

Funktionsprüfung des A/D-Wandlers

Schalten Sie die Betriebsspannung des MFA-Systems aus und fügen Sie die 8Bit-Ausgabekarte mit der Adresse 03 in das MFA-System ein.

An den Analogeingang der Ein-Ausgabekarte schließen Sie die einstellbare Gleichspannungsquelle an. Danach können Sie die Betriebsspannung wieder einschalten und folgendes Programm ab der Adresse E000 eingeben:

ANF: OUT 03 ;Startimpuls A/D-Wandlung

MVI B,04 ;Zeitverzoegerung

S1: DCR B ;für Umwandlung

JNZ S1

IN 02 ;gewandelten Wert lesen

JMP ANF ;und ausgeben

Durch den ersten OUT-Befehl wird der A/D-Wandler gestartet (IOW nimmt kuzzeitig L-Pegel an). Durch die danach folgenden drei Befehle wird eine Wartezeit für die Umwandlung erzeugt. Mit dem IN-Befehl wird der gewandelte Spannungswert gelesen, und dann beginnt die Umwandlung erneut, wobei der gewandelte Wert auch ausgegeben wird.

Entscheidend für die richtige Funktion des Wandlers ist die Wartezeit, die mindestens neun Taktimpulse betragen muss. Spannungs-Zeit-Diagramme der A/D-Wandlung Oszilloskopieren Sie folgende Spannungsverläufe:

- Usc= f (t) (IC12 PIN4)

- Ususv = f(t) (IC12 PIN1)

- UEN = f(t) (IC12 PIN2)

Die Oszillogramme tragen Sie in die Koordinatenkreuze auf der nächsten Seite ein!

HINWEIS ZU DEN MESSUNGEN

Die Triggerung des Oszilloskops erfolgte auf der positiven Flanke von UEN.

Mit dem ersten lmpuls am PIN4 (SC) wird der A/D-Wandler gestartet. Das BUSY-Signal nimmt gleichzeitig L-Pegel an. Nachdem BUSY wieder H-PegeI angenommen hat, ist die WandIung beendet. Durch den IN-Befehl wird danach der PIN2 (EN) kurzzeitig H-Pegel gelegt, der gewandelte Spannungswert gelesen und mit dem OUT-Befehl ausgegeben.

Abgleich_des_A/D-Wandlers

Schließen Sie die Gleichspannungsquelle an den Analogeingang an und stellen Sie null Volt ein.

Verstellen Sie jetzt das Poti R7 solange, bis an der Ausgabe-Baugruppe die LED B0 gerade aufleuchtet. Danach das Poti R7 in umgekehrter Richtung verstellen, bis die LED B0 gerade erlischt. Im nächsten Schritt stellen Sie eine Gleichspannung von 10 Volt ein. Jetzt wird das Poti R9 soIange verstellt, bis alle LED’s der

Ausgabe-Baugruppe aufleuchten.

Führen Sie die beiden AbgIeicharbeiten mehrmals hintereinander durch, da sie sich gegenseitig beeinflussen.

Damit ist die Übung beendet!