Einleitung

Beim Aufbau eines Mikrocomputer-Baugruppen-Systems, das aus verschiedenen Baugruppen (wie Bus-System, Mikroprozessor, Speicher und Ein/Ausgabe-Schaltungen) besteht, werden die einzelnen Baugruppen nach der Fertigung zunächst getrennt voneinander geprüft und in Betrieb genommen.

Zu solchen Prüf- und Inbetriebnahme-Arbeiten benötigt man u. a. einen Bus-Signalgeber, mit dem man Adress-, Daten- und Steuersignale auf die entsprechenden Leitungen legt und dort ihre Wirkung kontrolliert. So läßt sich relativ leicht feststellen, ob z.B. Bus-Leitungen kurzgeschlossen sind oder ob sich Speicherinhalte lesen oder ändern lassen.

Darüber hinaus kann man mit dem Bus-Signalgeber die Arbeitsweise der CPU mit Einschränkungen nachbilden. Dies ist für das Verständnis der Funktionsweise der CPU sowie ihres Zusammenwirkens mit anderen Baugruppen hilfreich.

Zur Anzeige der Adress-, Daten- und Steuersignale dient eine weitere Baugruppe – die Bus-Signalanzeige-, die im Kapitel 5.2 beschrieben wird.

Blockschaltbild, Aufbau und Wirkungsweise des Bus-Signalgebers

Bild 1 : Das Blockschaltbild des Bus-Signalgebers

Wenn der Umschalter »Signalgeber ON/OFF« in Stellung ON steht, sind alle drei Bustreiber für eine Signalabgabe freigeschaltet. Die mit dem Adressen-Wahlschalter eingestellten Adreßsignale stehen auf den 16 Adreßleitungen des System-Busses (A0 … A15) zur Verfügung. Die mit dem Daten-Wahlschalter eingestellten Datensignale werden jedoch nur dann zum System-Bus durchgelassen, wenn der DatenbusTreiber zusätzlich, über die Leitung Schreibfreigabe, freigegeben ist. Diese Freigabe liegt immer dann vor, wenn über den Block Steuersignal-Taster keine Lesesignale eingegeben werden. Der Block Steuersignal-Taster liefert bei Betätigung der entsprechenden Tasten Signale zum

- Lesen von Speicherstellen (MEMR)

- Lesen von Eingabe-Baugruppen (IOR)

- Schreiben in Speicherstellen (MEMW)

- Schreiben in Ausgabe-Baugruppen (IOW)

Will man Daten von einer Speicherstelle (MEMR) oder einer Eingabe-Baugruppe

(IOR) lesen, wird der Datenbus-Treiber gesperrt, weil durch die Lese-Steuersignale

andere Baugruppen veranlasst werden, Daten auf den Systembus zu schalten. Schaltet man den Umschalter Signalgeber ON/OFF in Stellung OFF, werden alle drei Bustreiber für eine Signalabgabe gesperrt, und eingestellte Adress-, Daten- und Steuersignale gelangen nicht mehr auf den System-Bus. Bei dieser Schalterstellung ist die CPUBaugruppe die aktive Baugruppe, sofern sie sich gemeinsam mit dem Bus-Signalgeber im Baugruppenträger befindet.

Damit besteht die Möglichkeit, bei Schalterstellung ON mit dem Signalgeber kleine Programme in einen Speicher einzugeben und danach durch Umschaltung des Schalters in Stellung OFF die CPU zu veranlassen, das eingegebene Programm abzuarbeiten.

Durch das Umschalten wird die CPU in ihren Grundzustand gebracht. Dies wird durch die Reset-Steuerung über die CPU-Leitung RESET IN veranlaßt. Über die Leitung RESET OUT quittiert die CPU den Empfang dieses Signals und setzt die Reset-Steuerung in deren definierten Grundzustand zurück; zur Reset-Steuerung vgl. auch Kapitel 4.4.

Bild 2: Der Stromlaufplan des Bus-Signalgebers

Die Erzeugung der Adresssignale

Bild 3 zeigt den Stromlaufplan des Adressen-Wahlschalters und des Adreßbus-Treibers,

und zwar für die Adressleitungen A0 bis A7. Die Innenschaltung des AdreßbusTreibers

ist nur für eine Leitung dargestellt; sie ist im Baustein insgesamt achtmal vorhanden.

Bild 3: Der Stromlaufplan für den Adressen-Wahlschalter und den Adreßbustreiber, hier nur für die Adreßleitungen A0 bis A7 gezeigt.

Da der Baustein 74LS642 einen Signalfluß von Seite A nach Seite B, sowie auch von B

nach A, ermöglicht und dabei die Signalpegel invertiert, wird er in Datenbüchern als »Achtfach invertierender Bus-Sende-Empfänger« (Transceiver) bezeichnet. Die internen Inverter sind mit offenen Kollektoren am Ausgang aufgebaut. Die Kollektorwiderstände liegen daher auf beiden Seiten außerhalb des Bausteins. Auf der A-Seite sind es die Widerstände R1 bis R8 (bzw. R9 bis R16 in Bild 2), und auf der B-Seite sind es die 10k-Widerstände (hier nur einer der 16 Widerstände dargestellt) im

Bus-Abschluß (der hier nicht näher betrachtet wird).

Der Freigabe-Eingang für Signalübertragungen, /G, liegt auf L-Pegel; dadurch ist der Baustein für Signalverkehr freigeschaltet (siehe Funktionstabelle in Bild 3). Mit dem zweiten Steuereingang DIR läßt sich nun die Übertragungsrichtung einstellen. Befindet sich der Umschalter Signalgeber ON/OFF in Stellung ON, so wird dem DIR-Eingang H-Pegel geliefert, und der Baustein läßt einen Signalfluß von der A- zur B-Seite zu, wobei die Signalpegel jeweils invertiert werden.

Die Pegel auf den Bus-Leitungen sind abhängig von der Stellung der Kontakte der Schalter S1 und S2 sowie S3 und S4. Ein geschlossener Kontakt erzeugt auf dem System-Bus H-Pegel, ein offener dagegen L-Pegel. Ist z.B. von Schalter S2 der Kontakt 1, wie in Bild 3 dargestellt, geschlossen, dann erhält Pin 6 L-Pegel, und am Ausgang (Pin 14) erscheint H-Pegel. Alle anderen Ausgänge führen L-Pegel.

Bei L-Pegel am DIR-Eingang (Umschalter auf OFF, Übertragungsrichtung von der B- zur A-Seite) sind die Pegel auf der Bus-Seite nicht mehr von denen auf der Schalter-Seite abhängig, sondern führen alle H-Pegel.

Die Adress- und Daten-Wahlschalter

Die Angabe von Adressen und Daten erfolgt in der Mikrocomputer-Technik aus Gründen der einfacheren Lesbarkeit in hexadezimaler Schreibweise. Der Mikroprozessor und auch jeder andere Computer verarbeitet jedoch nur binäre Signale als Befehle oder Daten. Solche binären Signale sind die Pegel auf den genannten Adress- und Datenleitungen. Sie werden mit Hilfe der Kontakte der Schalter S1 bis S4 bzw. S5 und S6 erzeugt (siehe Bild 2). Die Schalter übernehmen dabei auch die Umcodierung von der hexadezimalen in die binäre Darstellungsweise.

Jeder dieser Schalter stellt in Abhängigkeit von der eingestellten Hexadezimal-Ziffer an seinen Ausgängen vier binäre Signale zur Verfügung. Für die 16 Adreßleitungen werden daher vier Schalter benötigt, und für die 8 Datenleitungen zwei Schalter

Bild 4: Aufbau, Schaltbild und Funktionsprinzip eines Adreß- bzw. Daten-Wahlschalters

Bei Betätigung der Tasten + oder – wird im Inneren des Schalters ein Schleifer bewegt, der den mit C bezeichneten Anschluss je nach eingestellter Ziffer mit den Anschlüssen 8, 4, 2 oder 1 verbindet. In der Stellung »3« z.B. wird C mit 1 und 2 verbunden, und in der Stellung D würde C mit 1; 4 und 8 verbunden.

Addiert man die Anschlussbezeichnungen der geschlossenen Kontakte, so erhält man die eingestellte Hexadezimal-Zahl. Sollen z.B. für eine Prüfung die Kontakte 1 und 4 geschlossen sein, so ist die einzustellende Hexadezimal-Zahl 5.

Die Erzeugung der Datensignale

Bild 5 zeigt den Stromlaufplan des Daten-Wahlschalters und des Datenbus-Treibers. Auch hier ist wieder nur ein Leitungsweg dargestellt. Die Schaltung funktioniert, was die Datensignalfreigabe betrifft, genauso wie die Schaltung für die Adresssignale.

Zusätzlich müssen hier aber die Datensignale gesperrt werden, wenn eine der Steuersignaltasten MEMR oder IOR betätigt wird, denn beiden Steuersignale veranlassen andere Baugruppen (Speicher, Eingabe), ihrerseits Daten auf den System-Bus zu schalten. Würden die Datensignale des Signalgebers nicht gesperrt, so käme es auf dem Datenbus zu Kurzschlüssen. Die Sperrung des Datenbus-Treibers erfolgt dadurch, daß bei Betätigung der MEMR- oder IOR-Taste H-Pegel an seinen Freigabeeingang G gelegt wird. In der dargestellten, nicht betätigten Stellung der beiden Taster MEMR und IOR (Lesen) führen die Q-Ausgänge der prellfreien Schalter H-Pegel, was am Ausgang des NAND-Gatters den für Signalfreigabe nötigen L-Pegel bewirkt.

Sobald eine der beiden Tasten betätigt wird, nimmt der Ausgang von IC3.1 H-Pegel an und alle Inverter werden gesperrt. Der Signalzustand des Datenbusses wird nun nicht mehr von der Stellung der Daten-Wahlschalter S5 und S6 bestimmt, sondern von den Datensignalen der gelesenen Speicher- oder Eingabe-Baugruppe.

Bild 5: Der Stromlaufplan für den Daten-Wahlschalter und den Datenbustreiber

Die Erzeugung der Steuerbus-Signale

Bild 6 zeigt am Beispiel des Steuersignals MEMW (Speicher schreiben), wie das im MC-Baugruppensystem benötigte Steuersignal erzeugt wird. Alle anderen Steuersignale -MEMR, IOR und IOW- werden genauso erzeugt.

Bild 6: Der Stromlaufplan zur Erzeugung der Steuersignale, hier nur für das Signal MEMW gezeigt

Bei nicht betätigten Steuersignal-Tasten führen die Ausgänge der NAND-Gatter (IC 8.1 … 8.4) H-Pegel. Betätigt man eine der Tasten, so ändert sich der Pegel des entsprechenden NAND-Gatter-Ausgangs von H auf L, und der Lese- oder Schreibvorgang wird ausgeführt. Voraussetzung dafür ist, daß die Gatter mit H-Pegel auf der Leitung »Signalausgabe frei« für Signaldurchgang freigeschaltet sind.

Die Funktions-Blöcke »Signalgeber ON/OFF« und »Reset-Steuerung«

Bild 7 zeigt den Block Reset-Steuerung mit dem Block Signalgeber ON/OFF, der bisher als einfacher Umschalter dargestellt war.

Das D-Flipflop IC 4.1 dient der Entprellung des Schalters Sll. In der Schalterstellung ON ist das Flipflop gesetzt und liefert an seinem Q-Ausgang einen H-Pegel, mit dem die Adress-, Daten- und Steuerbus-Treiber für eine Signalausgabe freigeschaltet werden. Die von diesem Ausgang abgehende Leitung wurde »Signalausgabe-frei-Leitung« genannt. Nimmt sie in der Schalterstellung OFF einen L-Pegel an, so werden alle Bus-Treiber für eine Signalausgabe gesperrt.

Das Signal vom Q-Ausgang des ICs 4.1 wirkt auf das D-Flipflop IC4.2 im Block Reset-Steuerung und wird gleichzeitig über die HOLD-Leitung zur CPU-Baugruppe geführt. Dort bewirkt ein L-Pegel (Signalgeber ON), daß die CPU-Baugruppe vom Systembus getrennt wird.

Schaltet man Sll in Stellung OFF, so bewirkt die L-H-Flanke des HOLD-Signals (Q von IC 4.1), daß der Q-Ausgang des D-Flipflops IC 4.2 H-Pegel und die RESET IN-Leitung L-Pegel annimmt (siehe Bild 8); hierdurch wird die CPU in den Grundzustand gebracht (Befehlszählerstand auf 0). Voraussetzung für einen L-Pegel auf der RESET IN-Leitung ist, daß das D-Flipflop vorher rückgesetzt war, d.h., dass der Q-Ausgang L-Pegel führte. Diese Bedingung wird aber beim Einschalten des MC-Systems automatisch über die Leitung RESET OUT erfüllt.

Bild 7: Die Reset-Steuerung und die Umschaltung »Signalgeber ON/OFF«

Bild 8: Das Impulsdiagramm der Reset-Steuerung

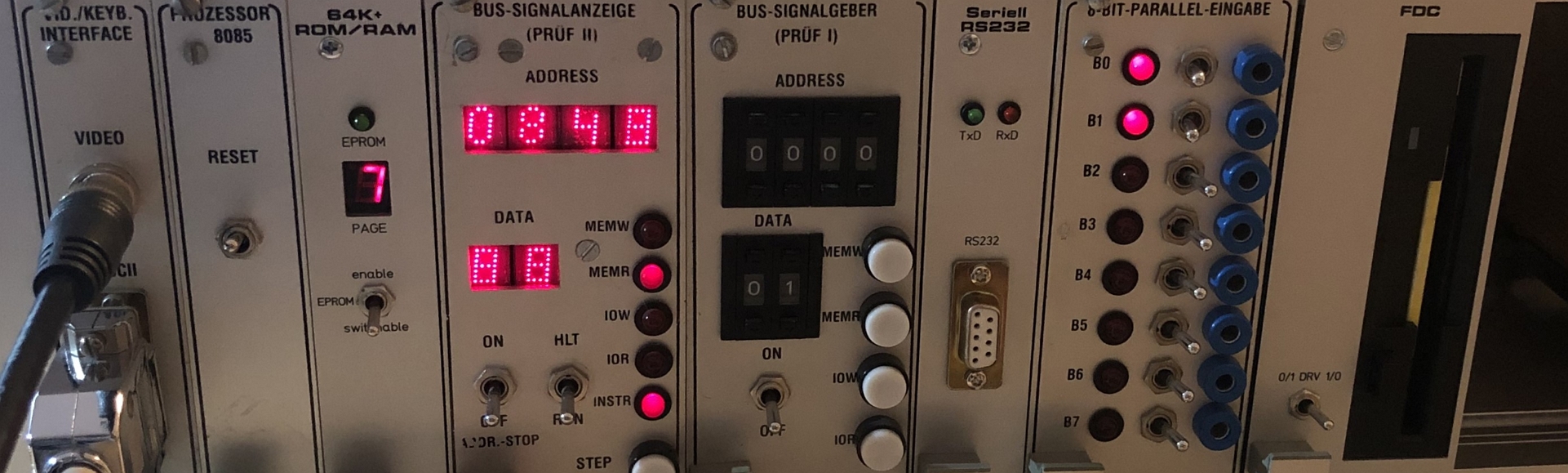

Die Baugruppe Bus-Signalanzeige wird innerhalb des Mikrocomputer-Baugruppensystems unter anderem für Funktionsprüfungen eingesetzt. Sie dient der Anzeige der auf dem System-Bus anstehenden Adress-, Daten- und Steuersignale, wobei die Signale der 16 Adressleitungen vierstellig und die der 8 Datenleitungen zweistellig angezeigt werden, jeweils als Hexadezimalzahl. Die Steuersignale werden direkt durch Leuchtdioden angezeigt.

Die Bus-Signalanzeige kann auch zusammen mit dem Mikroprozessor im vollständig aufgebauten System zur Fehlersuche eingesetzt werden. Aufgrund der hohen Arbeitsgeschwindigkeit des Prozessors ändern sich dann allerdings die Signale auf dem Bus so schnell, daß die Anzeige nicht mehr ablesbar ist. Eine Zusatzschaltung sorgt in diesem Fall dafür, daß die Bus-Signale für eine längere Zeit stabil sind. Der Mikroprozessor wird dazu auf die Betriebsart »Einzelschritt« umgeschaltet und führt dann nur jeweils einen Arbeitsschritt aus, wenn man die Taste »Step« betätigt.

Sobald sich die Baugruppe am System-Bus befindet, werden die auf dem Adressbus anstehende Adresse und der auf dem Datenbus anstehende Datenwert in hexadezimaler Form angezeigt. Jede hexadezimale Anzeige stellt die Bitkombination von vier Signalleitungen dar. Daher ist die Adressanzeige vierstellig (16 Bit) und die Datenanzeige zweistellig (8 Bit) .

Bestückungsplan

Verdrahtungsplan