Der Video 8.2-Karte Beine machen

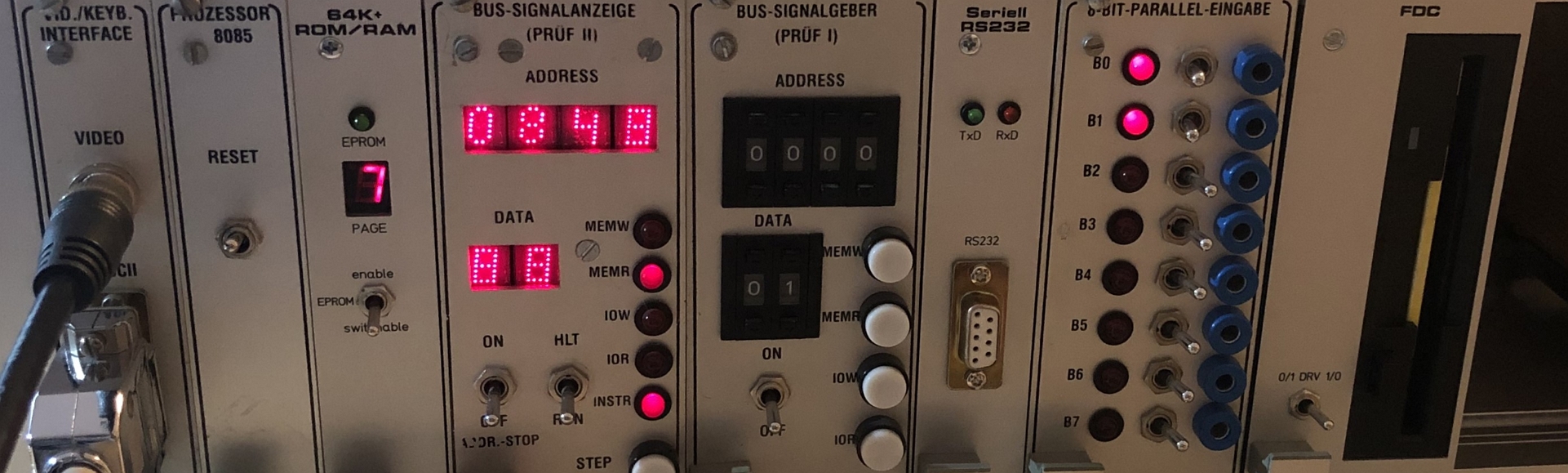

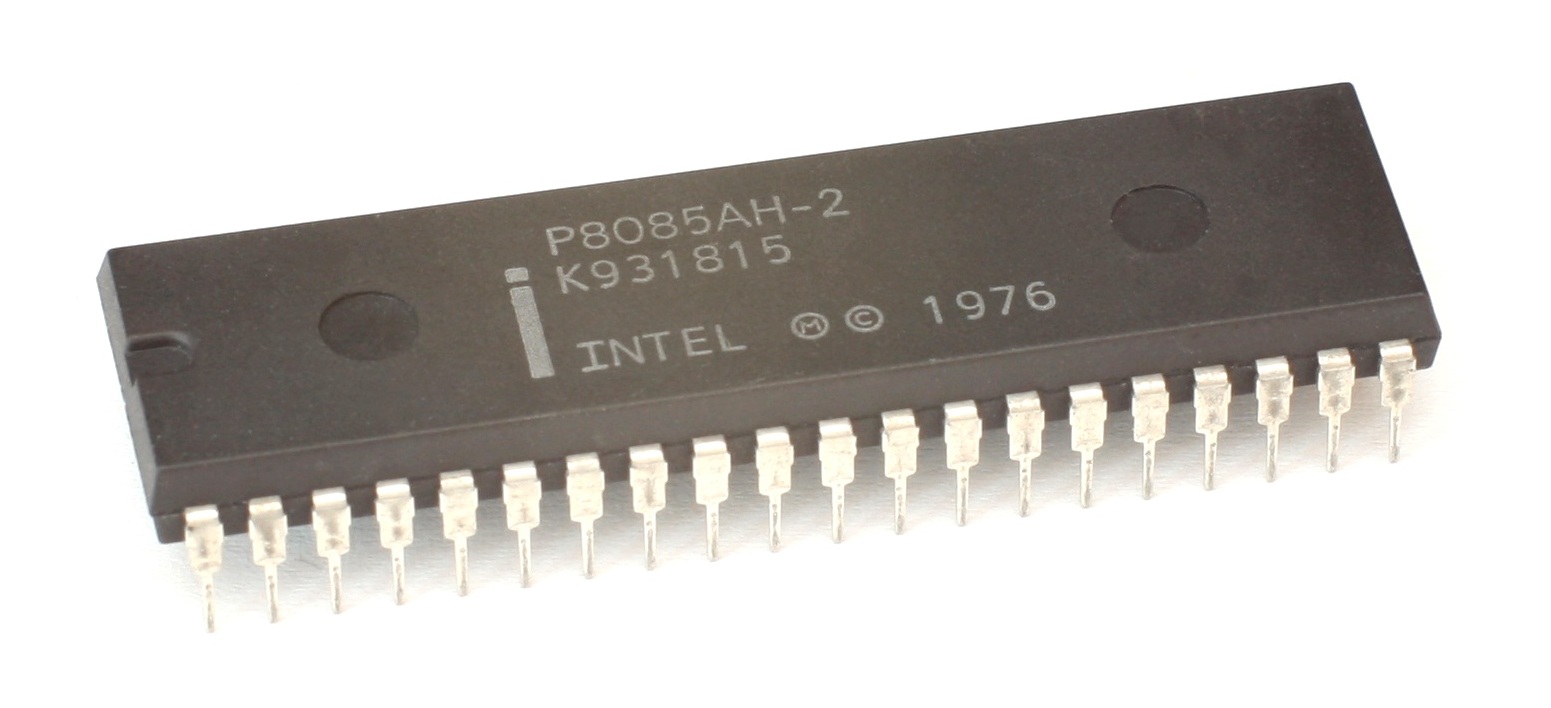

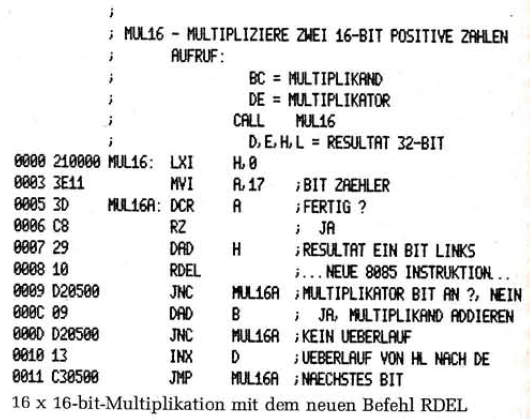

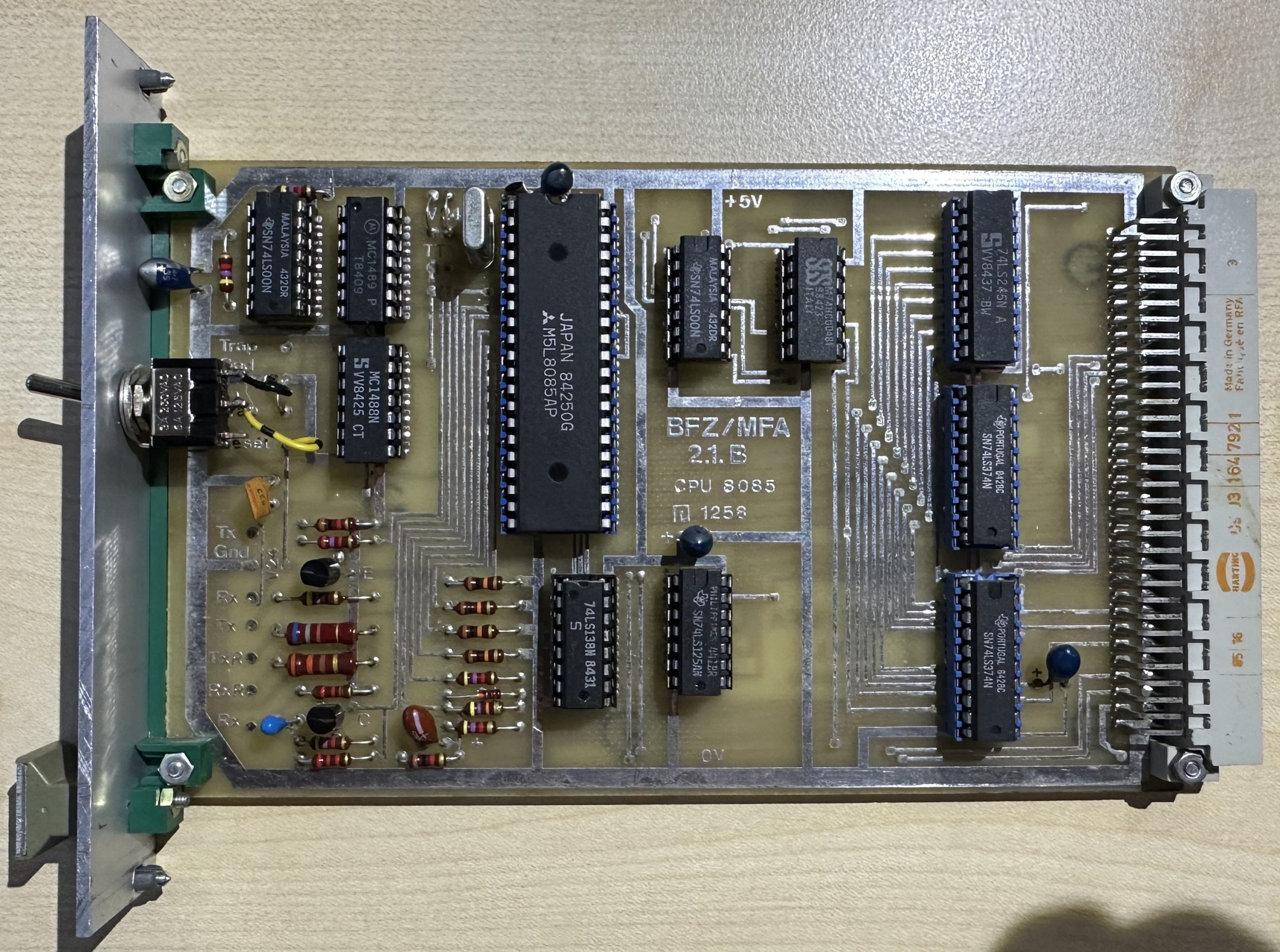

Beschreibung zur Umrüstung „MAT85 V1.8/S“ Betrieb der Standard 8.2-Videobaugruppe mit einer höheren Datenübertragung betreiben. Die Umrüstung „MAT85 V1.8/S“ erhöht die Geschwindigkeit der Zeichenübertragung zwischen CPU-Baugruppe und des Video-Interface BFZ/MFA-8.2 bzw. BFZ/MFA-8.4 von 1200 Bit/s auf 9600 Bit/a. Dieses wird durch Änderung der „Seriellen Ein-/Ausgabe-Routinen“ des Betriebsprogrammes MAT85 erreicht. Diese Software-Anpassung …