# **Einleitung**

Jeder Mikrocomputer enthält neben Prozessor und Speicher auch Eingabe- und Ausgabe-Einheiten, über die der Datenverkehr mit Geräten außerhalb des Mikrocomputers stattfindet. Häufig bezeichnet man die Eingabe- und Ausgabe-Einheiten auch als Eingabe- bzw. Ausgabe-Ports oder als Eingabe- bzw. Ausgabe-Schnittstellen, und die Geräte außerhalb des Mikrocomputers nennt man Peripheriegeräte.

Die zu übertragenden Daten können entweder seriell oder parallel übermittelt werden. Bei der seriellen Übertragung werden die einzelnen Bits eines Datenbytes nacheinander über eine einzige Leitung gesendet oder empfangen, während dies bei der parallelen Datenübertragung gleichzeitig über entsprechend viele Leitungen geschieht. Innerhalb einer bestimmten Zeit kann mit der parallelen Datenübertragung eine größere Datenmenge übermittelt werden als mit der seriellen.

Bei großen Entfernungen zwischen Peripheriegerät und Mikrocomputer bevorzugt man die serielle Übertragung. Sollen große Datenmengen in kurzer Zeit übermittelt werden, so wählt man die parallele Übertragung.

In den Kapiteln 4.1 und 4.2 wurden Eingabe- und Ausgabe-Einheiten für einen parallelen Datenaustausch beschrieben. Die Anzahl ihrer Ein- bzw. Ausgänge ist auf acht beschränkt und damit an die Datenbus-Breite des Mikrocomputers angepaßt.

Derartige einfache Ein- und Ausgabebaugruppen werden meist dort eingesetzt, wo man einzelne Signale (z.B. für Relais, Schütze, Anzeigelampen und Motoren) benötigt oder wo nur wenige Rückmeldesignale von Schaltern und Endlage-Meldern aus einer Maschine oder Anlage zu verarbeiten sind.

Zur Steuerung umfangreicher Maschinen oder Peripheriegeräte reicht die Anzahl der Ein- und Ausgänge der genannten Ports oft nicht aus. In diesen Fällen muß man entweder mehrere Ein- und Ausgabeports verwenden oder aber Ein/Ausgabe-Baugruppen mit Bausteinen speziell für solche Anwendungsfälle. In ihnen sind mehrere 8-Bit-Ports zusammengefaßt, wobei die Funktion der einzelnen Ports vom Anwender durch Programmierung bestimmt werden kann. Diese Programmierbarkeit führte zu Bezeichnungen wie programmierbarer Schnittstellen-Baustein oder programmierbarer Input/Output-Baustein.

- 6. Interfaces

- 6.1 Parallele Ein/Ausgabe, universell programmierbar

# Blockschaltbild und Arbeitsweise der Parallel-Baugruppe

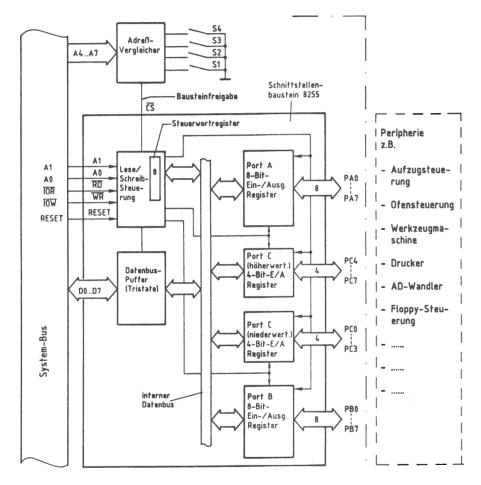

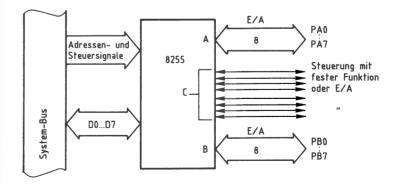

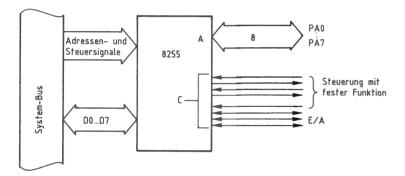

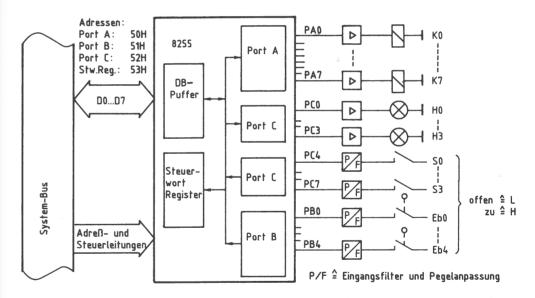

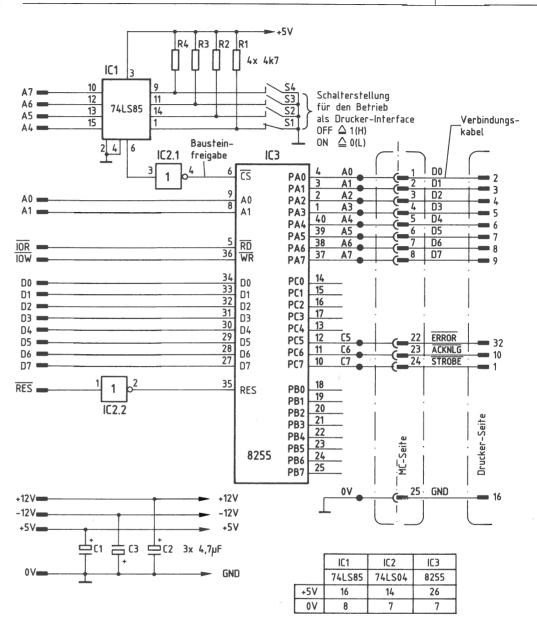

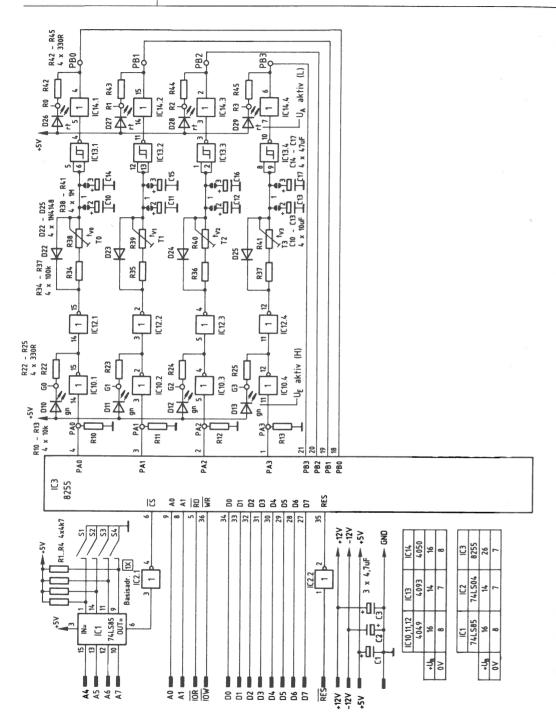

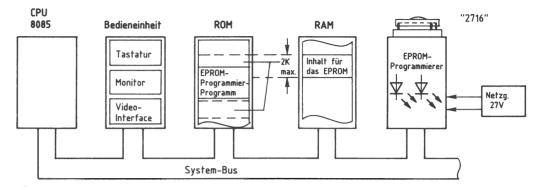

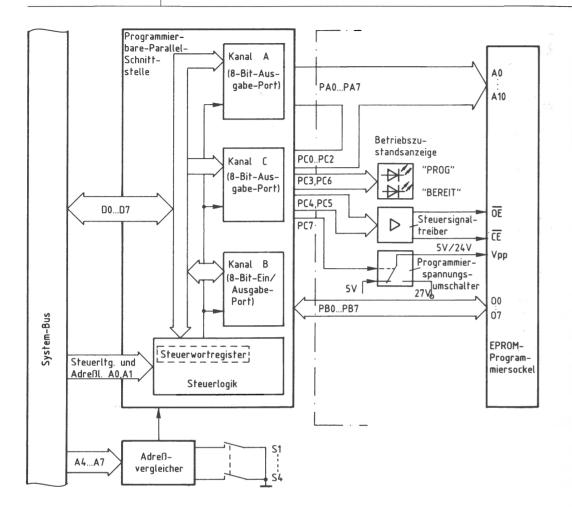

Bild 1 zeigt das Blockschaltbild der programmierbaren Parallel-Schnittstelle, die aus den Schaltungsteilen Adreßvergleicher und programmierbarer Schnittstellenbaustein (8255) besteht. Zunächst wird die grundsätzliche Wirkungsweise der Baugruppe anhand dieses Blockschaltbildes erklärt.

Bild 1: Das Blockschaltbild der programmierbaren Parallelschnittstelle.

6. Interfaces

6.1 Parallele Ein/Ausgabe, universell programmierbar

353

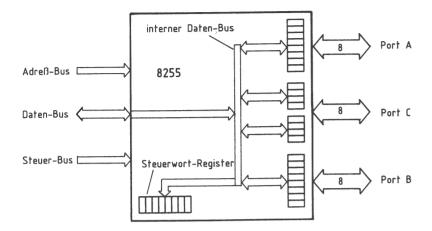

Der programmierbare Schnittstellenbaustein mit der Bezeichnung 8255 enthält drei voneinander unabhängige Datenkanäle (Ports), die durch Laden eines Steuerwortes in das interne Steuerwort-Register als Eingabe- oder Ausgabe-Ports programmiert werden können.

Alle Daten, die vom Mikroprozessor über Ausgabeports zur Peripherie oder von der Peripherie über Eingabe-Ports zum Mikroprozessor gelangen, werden über den internen Datenbus und den Datenbus-Puffer transportiert. Die Adressierung der Ports und des Steuerwort-Registers erfolgt über die Adreßleitungen A0 und A1. Mit Hilfe der Steuerleitung  $\overline{\text{IOR}}$  bzw.  $\overline{\text{IOW}}$  wird der Datentransport in die jeweilige Richtung ausgelöst. Ein Datentransport ist jedoch nur möglich, wenn der Baustein durch den Adreßvergleicher über die Bausteinfreigabe-Leitung freigegeben ist. Andernfalls ist der Datenbus-Puffer hochohmig.

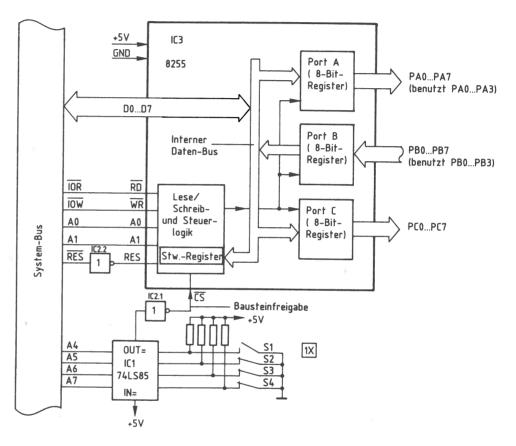

## Der Adreßvergleicher und die Baugruppennummer

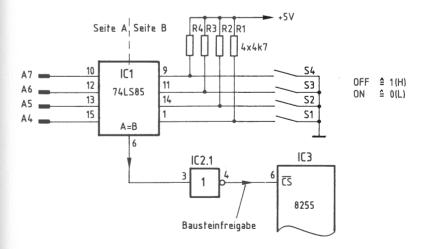

Der Mikroprozessor steuert die parallele Schnittstelle wie jede andere Eingabe- und Ausgabe-Einheit an. Da in einem Mikrocomputer-System nur jeweils eine einzige Einheit aktiviert sein darf, müssen alle im System vorhandenen Eingabe- und Ausgabe-Einheiten unterschiedliche Baugruppennummern besitzen. Aus diesem Grund ist die Baugruppennummer mit Hilfe von Schaltern einstellbar. Ein Adreßvergleicher übernimmt die Aufgabe, die Baugruppe nur dann zu aktivieren, wenn der Prozessor diejenige Adresse aussendet, die der eingestellten Baugruppennummer entspricht: Bild 2.

Bild 2: Der Adreßvergleicher.

- 6. Interfaces

- 6.1 Parallele Ein/Ausgabe, universell programmierbar

Nur wenn die Bitkombination auf den Adreßleitungen A4 bis A7 gleich der mit den Schaltern S1 bis S4 eingestellten Bitkombination ist, gibt der 4-Bit-Vergleicher IC1 an seinem Ausgang »A=B« ein H-Signal ab (Bild 2). Da zur Aktivierung des 8255 jedoch ein L-Signal am  $\overline{\text{CS}}$ -Eingang notwendig ist, wird das Ausgangssignal von IC1 durch IC2.1 invertiert.

Der Prozessor gibt beim Ansprechen einer Eingabe- oder Ausgabe-Baugruppe stets eine vollständige 8-Bit-Adresse an den Adreßleitungen A0 bis A7 aus. Bei dem hier realisierten Adreßvergleich werden jedoch die Adreßleitungen A0 bis A3 nicht berücksichtigt. Daher steht nicht der volle Adreßbereich von 00H bis FFH mit 256 verschiedenen Adreßwerten zur Verfügung. Mit den Schaltern S1 bis S4 lassen sich lediglich 16 verschiedene Signalzustände (Baugruppennummern) einstellen. Da diese Schalter den vier höherwertigen Adreßbits A4 bis A7 zugeordnet sind, kann die Baugruppennummer nur Werte von 0XH bis FXH annehmen. Das »X« steht hier für die vier niederwertigen Adreßbits A0 bis A3, die beim Adreßvergleich nicht benutzt werden: Bild 3.

|   | A 7<br>(S4) | A 6<br>(S3) | A 5<br>(S2) | A 4<br>(S1) | A 3<br>- u | A 2<br>nberüc | A 1<br>ksichti | A O | HEX -<br>Adresse |                                         |

|---|-------------|-------------|-------------|-------------|------------|---------------|----------------|-----|------------------|-----------------------------------------|

|   | 0           | 0           | 0           | 0           |            | _             |                | _   | 0 X              |                                         |

|   | 0           | 0           | 0           | 1           | _          | _             | _              | _   | 1 X              |                                         |

|   | 0           | 0           | 1           | 0           | _          |               |                |     | 2 X              |                                         |

|   | 0           | 0           | 1           | 1           | _          | _             | _              | _   | 3 X              |                                         |

|   | 0           | 1           | 0           | 0           | _          |               | _              |     | 4 X              |                                         |

| ~ | _           |             |             | i<br>i      |            | <br>          | <br> <br>      |     |                  |                                         |

|   | 1           | 0           | 1           | 1           |            | _             |                | _   | ВХ               |                                         |

|   | 1           | 1           | 0           | 0           |            |               |                | _   | C X              |                                         |

|   | 1           | . 1         | 0           | 1           | _          |               | _              |     | D X              | 12                                      |

|   | 1           | 1           | 1           | 0           | _          | _             |                | _   | EX               |                                         |

|   | 1           | 1           | 1           | 1           | ,—         | _             | _              | _   | FΧ               | niederwertiger                          |

|   |             |             |             |             |            |               |                |     |                  | Adreßteil<br>höherwertiger<br>Adreßteil |

Bild 3: Die Bildung der Baugruppen-Nummern auf der programmierbaren Parallelschnittstelle.

|    |           |              |            | 0.   | Interfaces  |

|----|-----------|--------------|------------|------|-------------|

| .1 | Parallele | Ein/Ausgabe. | universell | prog | grammierbar |

355

Im folgenden werden diese Schalterstellungen zugrundegelegt:

| S4(A7) | S3(A6) | S2(A5) | S1(A4) |

|--------|--------|--------|--------|

| ON     | OFF    | ON     | OFF    |

| 0      | 1      | 0      | 1      |

Hierdurch ergibt sich die Baugruppennummer 5XH. Grundsätzlich kann jede der 16 möglichen Baugruppennummern verwendet werden. Es ist aber darauf zu achten, daß alle Eingabe- oder Ausgabe-Baugruppen eines Mikrocomputer-Systems unterschiedliche Adressen besitzen, da es andernfalls zu Schäden am Gerät kommen kann.

### Die Adressierung der drei Ports und des Steuerwort-Registers

Beim Lesen der einzelnen Eingabeports, beim Ausgeben von Daten über die Ausgabeports und beim Einschreiben von Steuerworten in das Steuerwort-Register muß dem Baustein 8255 über die Adreßanschlüsse A0 und A1 mitgeteilt werden, welcher der vier internen Blöcke (drei Ports und ein Steuerwort-Register, siehe Bild 1) am gewünschten Datenverkehr beteiligt sein soll. Bild 4 zeigt die Adressierung der Blökke durch die Adreßleitungen A0 und A1.

| A1 | A0 | Port/Register       |

|----|----|---------------------|

| 0  | 0  | Port A              |

| 0  | 1  | Port B              |

| 1  | 0  | Port C              |

| 1  | 1  | Steuerwort-Register |

Bild 4: Die Adressierung der Ports und des Steuerwort-Registers.

| 2 |   | 6 |

|---|---|---|

| J | U | U |

### 6. Interfaces

### 6.1 Parallele Ein/Ausgabe, universell programmierbar

| A7 | A6                                                                                                                                                                      | A5 | Α4 | А3 | A2 | A1 | AO. | Adressen (Hex) | angesprochen wird   |  |  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|----|----|-----|----------------|---------------------|--|--|

| 0  | 1                                                                                                                                                                       | 0  | 1  | Χ  | χ  | 0  | 0   | 50, 54, 58, 50 | Port A              |  |  |

| 0  | 1                                                                                                                                                                       | 0  | 1  | Х  | Χ  | 0  | 1   | 51, 55, 59, 5D | Port B              |  |  |

| 0  | 1                                                                                                                                                                       | 0  | 1  | Х  | Χ  | 1  | 0   | 52, 56, 5A, 5E | Port C              |  |  |

| 0  | 1                                                                                                                                                                       | 0  | 1  | Х  | χ  | 1  | 1   | 53, 57, 5B, 5F | Steuerwort-Register |  |  |

|    | Port- und Steuerwort-Register-Auswahl  nicht angeschlossen, daher 0 oder 1 möglich  Baugruppennummer, mit \$1 bis \$4 einstellbar  von OXH bis FXH, hier gewählt: "5XH" |    |    |    |    |    |     |                |                     |  |  |

Bild 5: Die Adreßbildung mit den Adreßleitungen A0 bis A7.

Die Bitkombination an A4 bis A7 (siehe Bild 5) entspricht der mit den Adreßschaltern S1 bis S4 eingestellten Baugruppennummer. Die Bitkombination an A0 und A1 bestimmt, ob eines der drei Ports oder das Steuerwort-Register des Schnittstellenbausteins 8255 angewählt wird.

Die Adreßleitungen A2 und A3 sind nicht angeschlossen; daher kann ihr Signalzustand 1 oder 0 sein. Hieraus ergeben sich vier mögliche Adressen für jedes Port und das Steuerwort-Register. Port A kann beispielsweise unter den Adressen 50H, 54H, 58H und 5CH angesprochen werden. Diese Mehrfach-Adressierung ist durch die einfache Schaltung bedingt. Alle Adressen beginnen aber stets mit der durch S1 bis S4 gebildeten Hex-Zahl (hier 5). Um Verwirrungen zu vermeiden, sollten die Ports und das Steuerwort-Register fortlaufend, z.B. unter den Adressen 50H, 51H, 52H und 53H, angesprochen werden. (Es wäre natürlich auch möglich, sie z.B. unter den Adressen 58H, 55H, 5EH und 57H zu erreichen.)

# Die Steuerung der Datenübertragungs-Richtung

Nachdem der Mikroprozessor die Adresse eines der drei Ports oder des Steuerwort-Registers ausgegeben hat, steuert er durch L-Pegel auf einer der beiden Steuerleitungen  $\overline{IOR}$  oder  $\overline{IOW}$ , ob er Daten aus dem Baustein lesen oder zum Baustein senden will. Die beiden Steuerleitungen sind mit den Bausteinanschlüssen  $\overline{RD}$  und  $\overline{WR}$  verbunden (Bild 1). Mit den Pegeln an diesen Eingängen wird innerhalb des Bausteins über die Lese/Schreib-Steuerung die Datenübertragungs-Richtung gesteuert.

# 6. Interfaces 6.1 Parallele Ein/Ausgabe, universell programmierbar

357

In Zusammenwirken mit den Pegeln auf den Bausteineingängen A0, A1 und  $\overline{\text{CS}}$  erfolgt der Zugriff zu den einzelnen Ports und dem Steuerwort-Register wie in Bild 6 dargestellt.

| A1 | A0 | cs | RD | WR | Datenübertr.Richtung, DBus-Puffer-Zustand   |

|----|----|----|----|----|---------------------------------------------|

| 0  | 0  |    |    |    | Daten von Port A zum System-Bus             |

| 0  | 1  | Ö  | Ò  | 1  | Daten von Port B zum System-Bus             |

| 1  | 0  |    |    |    | Daten von Port C zum System-Bus             |

| 1  | 1  | 0  | 0  | 1  | Ungültige Bedingung                         |

| 0  | 0  | 1  |    |    | Daten vom System-Bus an Port A              |

| 0  | 1  |    |    |    | Daten vom System-Bus an Port B              |

| 1  | 0  | 0  | i  | Ó  | Daten vom System-Bus an Port C              |

| 1  | 1  |    |    |    | Daten vom System-Bus an das Steuerwort-Reg. |

| X  | Χ  | 1  | Χ  | Χ  | Datenbus-Puffer vom System-Bus getrennt     |

Bild 6: Die Steuerung der Datenübertragungs-Richtung und des Datenbus-Puffers.

In das Steuerwort-Register kann nur geschrieben werden. Bei H-Pegel am  $\overline{\text{CS}}$ -Eingang wird der Datenbus-Puffer in den hochohmigen Zustand geschaltet und dadurch vom System-Bus getrennt. Die Pegel auf den Eingängen A0, A1,  $\overline{\text{RD}}$  und  $\overline{\text{WR}}$  sind dann für die Funktion des Bausteins bedeutungslos.

### Die Betriebsarten des Schnittstellen-Bausteins 8255

Zur Anpassung an die vielfältigen Erfordernisse der Peripherie kann man den Schnittstellenbaustein in den Betriebsarten 0, 1 und 2 benutzen. Zunächst werden die wesentlichen Merkmale dieser drei Betriebsarten dargestellt.

Betriebsart 0 (einfache Ein/Ausgabe; vgl. Bild 7):

- Die Ports A, B und C werden wahlweise als Eingabe- oder als Ausgabe-Ports betrieben:

- Port C ist in zwei 4-Bit-Kanäle aufteilbar;

- je ein 4-Bit-Kanal von Port C kann in Verbindung mit den Ports A und B verwendet werden (siehe auch Bild 1);

- die Port-Ausgänge haben Zwischenspeicher;

- die Port-Eingänge arbeiten ohne Zwischenspeicher.

### 6. Interfaces

### 6.1 Parallele Ein/Ausgabe, universell programmierbar

Bild 7: Die Betriebsart 0 des Bausteins 8255.

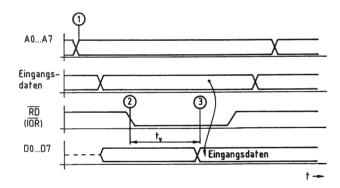

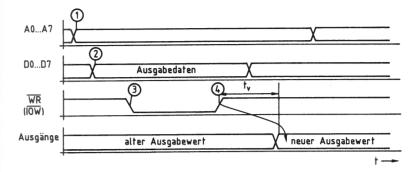

In der Betriebsart 0 werden die drei Ports wie Ein- oder Ausgabebaugruppen behandelt, d.h. Daten werden an das ausgewählte Port ausgegeben oder aus ihm gelesen. Bild 8 zeigt den Signalverlauf für das Lesen von Daten aus einem Eingabe-Port.

Bild 8: Das Lesen eines Eingabe-Ports.

- ① Der Prozessor gibt auf den Leitungen A0 bis A7 die Portadresse aus.

- 2 Der Prozessor schaltet das Steuersignal IOR auf L-Pegel.

- (3) Nach einer Verzögerungszeit t<sub>v</sub> wird der zu diesem Zeitpunkt an den Eingängen vorhandene Signalzustand auf den Datenbus durchgeschaltet (und in den Akku der CPU übernommen).

# 6. Interfaces 6.1 Parallele Ein/Ausgabe, universell programmierbar

359

Bild 9: Die Ausgabe von Daten an ein Ausgabe-Port.

- 1 Der Prozessor gibt auf den Leitungen A0 bis A7 die Adresse des Ausgabe-Ports aus.

- (2) Der Prozessor stellt das auszugebende Datenwort bereit.

- (3) Mit dem L-Pegel auf der Steuerleitung <del>IOW</del> zeigt der Prozessor an, daß er Daten in das adressierte Ausgabe-Port schreiben will.

- (4) Mit der L-H-Flanke des Steuersignals wird das Datenwort in den Ausgabe-Zwischenspeicher übernommen und erscheint nach einer Verzögerungszeit t<sub>v</sub> (ca. 70 ns) am Ausgang des Ports.

Betriebsart 1 (Ein-/Ausgabe mit zusätzlichen Steuerleitungen; vgl. Bild 10):

Diese Betriebsart dient zum Austausch von Ein-Ausgabe-Daten zu oder von einem Port in Verbindung mit zusätzlichen Steuersignalen bzw. »Quittungs-Signalen«. Hierzu werden die drei Ports wie folgt verwendet:

- Die Ports A und/oder B werden als Eingabe- oder als Ausgabe-Port betrieben.

- Jedem dieser beiden Ports sind vier Leitungen des Ports C mit teilweise fester Funktion zugewiesen.

Bild 10: Die Betriebsart 1 des Bausteins 8255.

6. Interfaces

6.1 Parallele Ein/Ausgabe, universell programmierbar

Die Betriebsart 1 wird z.B. dazu verwendet, über die Parallelschnittstelle einen Matrix-Drucker anzusteuern. Hierbei dient Port A als Datenkanal und eine Hälfte von Port C zur Übertragung der notwendigen Steuersignale; siehe Seite 367ff.

Betriebsart 2 (Getastete Zweiweg-Bus-Ein-/Ausgabe; vgl. Bild 11):

Diese Betriebsart, die nur mit Port A möglich ist, gestattet einen 8-Bit-Datenaustausch mit der Peripherie, wobei Daten gesendet und empfangen werden können. Hierbei sind dem Port A fünf Leitungen des Ports C mit fest vorgegebener Funktion zugeordnet, womit der Datenfluß von Port A gesteuert werden kann. Diese Betriebsart wird in diesem Buch nicht weiter behandelt.

Bild 11: Die Betriebsart 2 des Bausteins 8255.

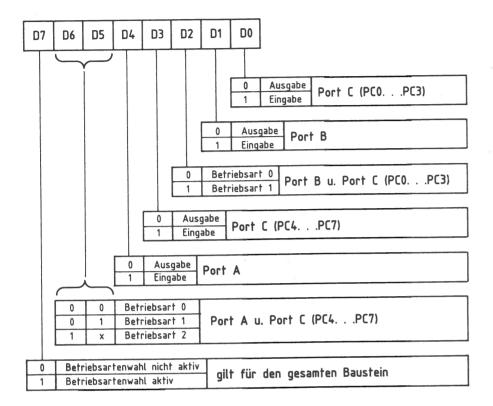

# Die Initialisierung des Schnittstellenbausteins

Die gewünschte Betriebsweise muß vor dem Betrieb der einzelnen Ports programmiert werden. Dies geschieht grundsätzlich durch Senden eines sogen. Steuerwortes an das Steuerwort-Register, das sich innerhalb der Lese/Schreib-Steuerung befindet (Bild 1). Die Lese/Schreib-Steuerung gibt daraufhin entsprechende Steuersignale an die Ports aus. Das Einschreiben des Steuerwortes in das Steuerwort-Register nennt man Initialisieren des Bausteins (Setzen von Anfangsbedingungen).

6. Interfaces

6.1 Parallele Ein/Ausgabe, universell programmierbar

361

Hierzu sind folgende Schritte erforderlich:

- Der Akkumulator des Prozessors muß mit dem Wert des erforderlichen Steuerwortes geladen werden. Hierzu eignet sich der Befehl »MVI A,konst« des Prozessors 8085.

- Zu dem Akku muß das Steuerwort nun an das Steuerwort-Register ausgegeben werden. Hierzu dient der Befehl »OUT adr« des Prozessors 8085. Die Adresse für das Steuerwort-Register ist 53H, da hier von der Baugruppennummer 5X ausgegangen wird; siehe Seite 355ff.

Bei der Initialisierung ist folgendes zu beachten:

- Durch kurzzeitigen H-Pegel am Reset-Eingang des Bausteins wird das Steuerwort-Register gelöscht, und alle Ports werden in den Eingabezustand gebracht. Nach jeder Betätigung der Reset-Taste oder nach einem Kaltstart des Mikrocomputers muß der Baustein daher neu initialisiert werden.

- Die Betriebsarten der Ports A und B können unabhängig voneinander definiert werden. Port A kann z.B. in Betriebsart 1 arbeiten und Port B in Betriebsart 0.

Port C wird entsprechend den Erfordernissen der Ports A und B in zwei Teile aufgeteilt.

Jedes Steuerwort zur Initialisierung besitzt acht Bits (D0 bis D7), wobei jedes einzelne Bit eine bestimmte Funktion des Bausteins steuert. Bild 12 stellt den Aufbau des Steuerwortes dar. Die Bezeichnungen der einzelnen Bits sind dem Datenbuch des Baustein-Herstellers entnommen.

### 6. Interfaces

6.1 Parallele Ein/Ausgabe, universell programmierbar

Bild 12: Der Aufbau des Steuerwortes für den 8255 und die Bedeutung der einzelnen Bits.

Das folgende Beispiel zeigt, wie ein Steuerwort mit Hilfe dieser Tabelle gebildet wird. Dabei soll der programmierbare Schnittstellenbaustein wie folgt arbeiten:

Betriebsart 0

Port A Eingabeport

Port B Ausgabeport

Port C, PC0 bis PC3 1/2 Ausgabeport (4 Ausgabeleitungen)

Port C, PC4 bis PC7 1/2 Eingabeport (4 Eingabeleitungen)

Mit Hilfe von Bild 12 wird das Steuerwort gebildet, das sich aus den gewünschten Betriebsbedingungen wie folgt ergibt:

D7 D6 D5 D4 D3 D2 D1 D0

$$1 0 0 0 1 1 0 0 0 0 = 98 \text{ im Hexadezimal-Code}$$

6. Interfaces

6.1 Parallele Ein/Ausgabe, universell programmierbar

363

Bevor die Ports A, B und C entsprechend den genannten Anforderungen als Eingabeund Ausgabe-Ports betrieben werden können, muß das Steuerwort an das Steuerwort-Register ausgegeben werden. Hierzu dienen folgende Befehle:

| Befehl                 | Kommentar                                                    |

|------------------------|--------------------------------------------------------------|

| <br>MVI A,98<br>OUT 53 | Steuerwort in den Akku laden und an Steuerwort-Reg. ausgeben |

| • • •                  | •••                                                          |

Die Adresse des Steuerwort-Registers (53H) ergibt sich aus Bild 5.

## Ein Anwendungsbeispiel für die Betriebsart 0

Das folgende Beispiel zeigt, wie mit Hilfe eines einzigen Schnittstellenbausteins eine recht umfangreiche Steuerung aufgebaut werden kann.

Bild 13: Die Verbindung von einer externen Anlage zum Schnittstellenbaustein 8255.

| 2 | 6 | 1 |

|---|---|---|

| J | U | 4 |

- 6. Interfaces

- 6.1 Parallele Ein/Ausgabe, universell programmierbar

Aus der Schaltung von Bild 13 ergeben sich für den Schnittstellenbaustein die folgenden Betriebsbedingungen:

| Betriebsart 0       |             |

|---------------------|-------------|

| Port A              | Ausgabeport |

| Port B              | Eingabeport |

| Port C, PC0 bis PC3 | Ausgabeport |

Port C, PC4 bis PC7 Eingabeport

Mit Hilfe der Tabelle in Bild 12 ergibt sich für das Steuerwort der hexadezimale Wert 8A. Zur Initialisierung des Schnittstellenbausteins wird dieses Steuerwort in das Steuerwort-Register (Adresse 53H) geschrieben.

Der daran anschließende Programmausschnitt (Bild 14) bewirkt in der Anlage, daß Relais K2 und Signallampe H3 nur dann eingeschaltet werden, wenn Schalter S0 und Endschalter Eb2 geschlossen sind.

| Label         | Befehl                                                                      | Kommentar                                                                                                                                                                                                                                                                                                                                                                                                            | 11 11                                         |

|---------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| WARTE:        | IN 52 ANI 10 JZ WARTE IN 51 ANI 04 JZ WARTE MVI A,04 OUT 50 MVI A,08 OUT 52 | Steuerwort in den Akku laden und an das Steuerwort-Register mit der Adresse 53H übergeben (Initialisierung des 8255) Port C lesen Maske zur Abfrage, ob S0 geschl. Nein: Weiter abfragen Ja: Port B lesen Maske zur Abfrage, ob Eb2 geschl. Nein: Wieder Zustand S0 abfragen Ja: Ausgabewert zum Einsch. von K2 in den Akku und an Port A ausgeben Ausgabewert zum Einsch. von H3 in den Akku und an Port C ausgeben | NEIN SO Ein ?  NEIN Eb2 Ein ?  NEIN Eb2 Ein ? |

| Bild 14: Befe | l<br>hlsfolge und Flußdiag<br>annten Aufgabenstellu                         | gramm zur Lösung der im Text<br>ung; vgl. Bild 13.                                                                                                                                                                                                                                                                                                                                                                   | K2 u. H3<br>einschalt.<br>(Port A)            |

6. Interfaces

365

6.1 Parallele Ein/Ausgabe, universell programmierbar

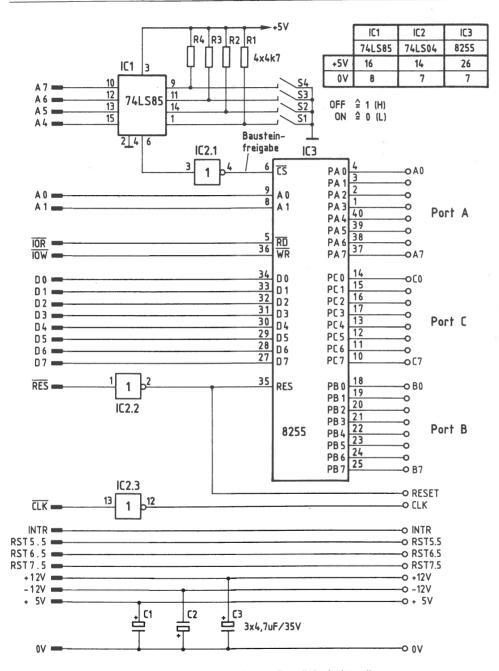

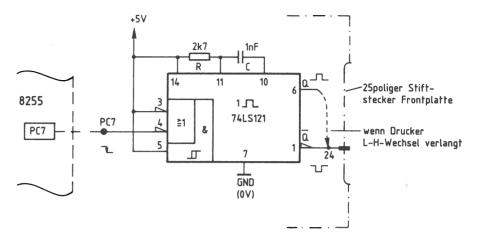

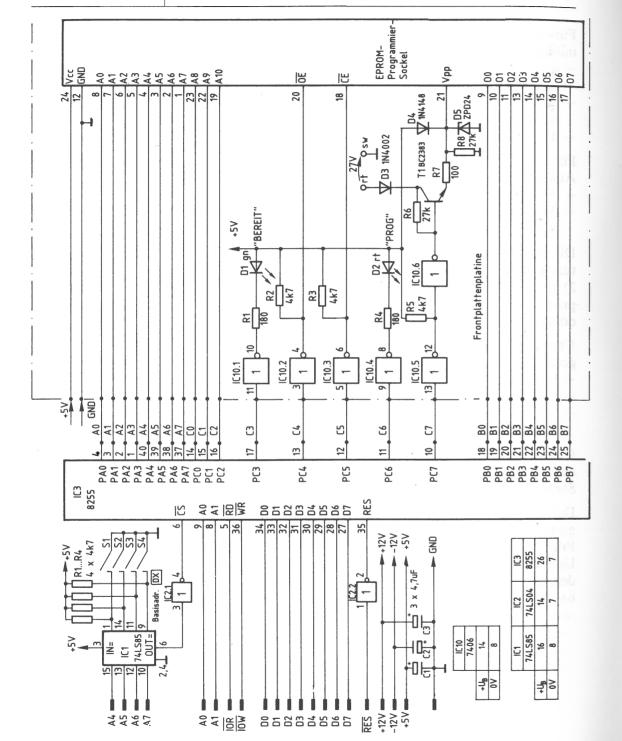

# Die Schaltung der universell programmierbaren Parallel-Schnittstelle

Bild 15 zeigt den Stromlaufplan. Der Adreßvergleicher wird gebildet durch IC1, die Widerstände R1 und R4 und die Schalter S1 bis S4. Durch L-Signal an Pin 6 wird der Schnittstellenbaustein 8255 bei Adressengleichheit freigegeben und kann über die Datenleitungen D0 bis D7 Daten vom Prozessor empfangen oder an ihn ausgeben.

Die Adreßleitungen A0 und A1 dienen zur Auswahl der im Inneren von IC3 vorhandenen Ports A bis C und des Steuerwort-Registers. Die Leitungen  $\overline{\text{IOR}}$  und  $\overline{\text{IOW}}$  lösen das Lesen bzw. Schreiben der Daten aus.

Das vom Prozessor gelieferte Reset-Signal (L-aktiv) wird durch IC2.2 invertiert, da IC3 zum Zurücksetzen ein H-Signal benötigt. Hierdurch werden beim Einschalten des Mikrocomputers alle Ports auf Eingabe geschaltet.

Jeder Ausgang des Schnittstellenbausteins 8255 (Port A bis Port C) kann mit einem Strom von etwa 1 mA belastet werden. Weitere Hinweise müssen den Datenbüchern der Bausteinhersteller entnommen werden.

In den nächsten Abschnitten werden drei Anwendungen der universell programmierbaren Parallel-Schnittstelle behandelt:

Drucker-Interface (ab Seite 367), 4fach-Zeitwerk (ab Seite 382), EPROM-Programmierer (ab Seite 391).

### 6. Interfaces

### 6.1 Parallele Ein/Ausgabe, universell programmierbar

Bild 15: Der Stromlaufplan der programmierbaren Parallelschnittstelle.

6. Interfaces 6.1 Parallele Ein/Ausgabe, Drucker-Interface

367

Beim Erstellen längerer Programme entsteht sehr schnell der Wunsch, die Programmtexte (Quellcode) auszudrucken. Arbeiten wie Fehlersuche im Programm, Berichtigungen, Einbringen von Erweiterungen und Programmdokumentation lassen sich wesentlich besser durchführen, wenn der Programmtext zusammenhängend überschaut werden kann.

In der Mikrocomputertechnik werden häufig Matrixdrucker verwendet, die eine Vielzahl von Druckoperationen (Zeichensätze, Schriftarten, Sonderfunktionen) bieten, ferner eine hohe Druckgeschwindigkeit besitzen und oft preisgünstig sind.

Drucker erfordern als Mikrocomputer-Ausgabegeräte eine Interface-Baugruppe, die den speziellen Ablauf der Datenübertragung zwischen Mikrocomputer und Drucker unterstützt; außerdem muß hierzu ein Programm zur Verfügung stehen.

Das hier beschriebene Drucker-Interface ist für den Anschluß von Matrix-Druckern mit Centronics-Schnittstelle vorgesehen. Das Programm zur Steuerung der Datenübertragung ist jeweils im Betriebsprogramm des Mikrocomputers enthalten.

# Wirkungsweise und Blockschaltbild eines Matrix-Druckers

Punktmatrix-Nadeldrucker besitzen einen Druckkopf mit z.B. 9 übereinanderliegenden Drucknadeln, die mit gleichmäßiger Geschwindigkeit an einem Farbband und am Papier vorbeibewegt werden. Zum Darstellen eines Zeichens sorgt eine elektronische Steuerung dafür, daß die entsprechenden Nadeln zur richtigen Zeit auf das Farbband schlagen und dabei einen Farbpunkt auf dem Papier erzeugen. Bild 16 zeigt als Beispiel den Buchstaben A, dargestellt in einer 9×9-Punktmatrix.

Bild 16: Die Darstellung des Buchstabens A in einer 9×9-Matrix.

- 6. Interfaces

- 6.1 Parallele Ein/Ausgabe: Drucker-Interface

Nachdem die Drucknadeln einer Punktspalte betätigt wurden, wartet die Steuerung eine bestimmte Zeit, bevor sie die Nadeln zur Darstellung der nächsten Punktspalte aktiviert. Durch Veränderung dieser Wartezeit lassen sich unterschiedliche Schriftbreiten erzeugen. Eine entsprechende Ansteuerung der Drucknadeln ermöglicht mehrere Zeichensätze (z.B. deutsch, englisch, dänisch), und zum Ändern der Zeilenabstände können unterschiedliche Papiervorschübe gewählt werden.

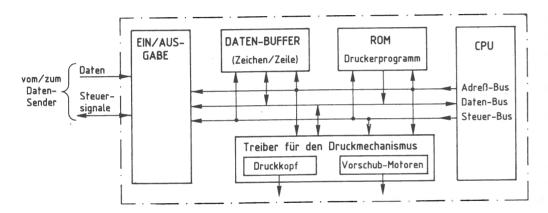

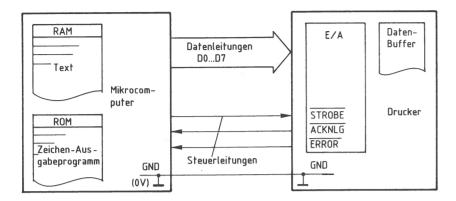

Die Steuerung der internen Druckfunktionen und des Datenverkehrs zwischen Drukker und Sendegerät, das dem Drucker die darzustellenden Zeichen im ASCII-Code übermittelt, erfolgt innerhalb des Druckers durch ein eigenes Mikrocomputer-System: Bild 17.

Bild 17: Prinzipielles Blockschaltbild eines Matrix-Druckers.

Das Programm zur Steuerung des Druckers befindet sich im ROM-Speicher. Über das Ein/Ausgabe-Port findet der Verkehr mit dem Datensender statt. Der Daten-Buffer (Puffer) enthält jeweils den Code für die gerade zu druckende Zeile.

#### **Die Centronics-Schnittstelle**

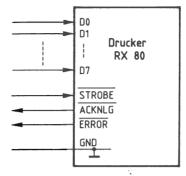

Damit der Datensender die Datenbytes der zu druckenden Zeichen nicht alle auf einmal an den Drucker sendet, besitzt dieser neben den Datenleitungen eine Reihe von Steuerleitungen, mit deren Hilfe der Datenverkehr zwischen Datensender und Drucker gesteuert wird; siehe Bild 18.

6. Interfaces 6.1 Parallele Ein/Ausgabe: Drucker-Interface

369

Bild 18: Die Anschlußleitungen der Centronics-Schnittstelle, z.B. beim Epson RX80.

Die in Bild 18 gezeigten Anschlüsse haben folgende Bedeutung:

D0 bis D7 Über diese 8 Datenleitungen werden die Datenbytes der zu druckenden Zeichen vom Datensender zum Drucker gesendet (Parallelübertragung). Sie werden in den Daten-Buffer übernommen, wenn das STROBE-Signal low ist.

STROBE Mit dem STROBE-Signal (strobe = Markierung, Impuls) wird dem Drucker signalisiert, daß Daten auf den Datenleitungen bereit stehen und übernommen werden sollen.

ACKNLG Mit einem low-Impuls (12 μs) auf der ACKNLG-Leitung (von acknowledge = bestätigen) meldet der Drucker, daß er die Daten verarbeitet hat und wieder empfangsbereit ist.

ERROR Durch low-Pegel auf dieser Leitung (error = Fehler) meldet der Drukker dem Datensender, daß er nicht empfangsbereit ist. Gründe für diese Meldung sind:

- Drucker im OFF-LINE-Betrieb (vom Datensender getrennt),

- Papier zu Ende,

- interner Fehler.

## Der Ablauf des Datenverkehrs zwischen Mikrocomputer und Drucker

Bild 19 zeigt, wie der Drucker über die oben beschriebenen Leitungen an ein Mikrocomputer-System angeschlossen wird.

Im RAM-Speicher des Mikrocomputers befinden sich die Datenbytes des Textes, den der Drucker ausdrucken soll. Dieser Text muß Byte für Byte mit Hilfe eines Programms, das sich im ROM- oder im RAM-Speicher des Mikrocomputers befindet, über die Datenleitungen zum Drucker übertragen werden.

- 6. Interfaces

- 6.1 Parallele Ein/Ausgabe: Drucker-Interface

Bild 19: Der Anschluß des Druckers an ein Mikrocomputer-System.

Die Steuerung dieser Datenübertragung erfolgt durch die Signale der beiden Steuerleitungen STROBE und ACKNLG. Die ERROR-Leitung wird später betrachtet.

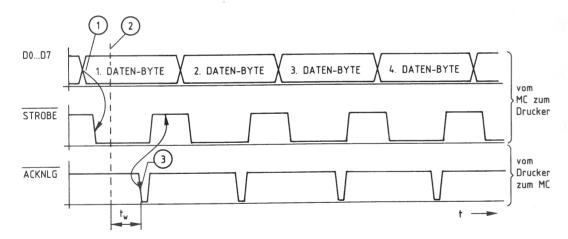

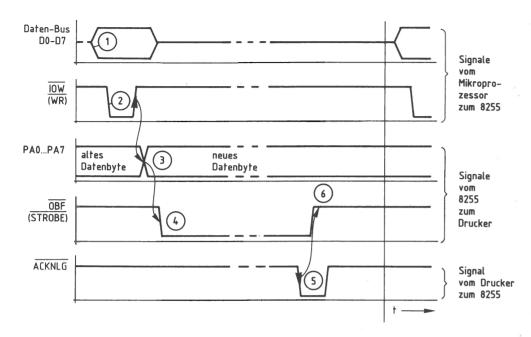

Bild 20: Der zeitliche Ablauf der Übertragung von Datenbytes vom Mikrocomputer zum Drucker; Erklärung im Text.

Erklärungen zu Bild 20:

① Zu diesem Zeitpunkt hat der Mikrocomputer den ASCII-Code des ersten Datenbytes auf die Datenleitungen D0 bis D7 geschaltet. Kurz danach schaltet er das STROBE-Signal auf L-Pegel. Hierdurch signalisiert er dem Drucker, daß ein Datenbyte übernommen werden kann.

6. Interfaces

6.1 Parallele Ein/Ausgabe: Drucker-Interface

371

- ② Ist der Drucker empfangsbereit, so übernimmt er das angebotene Datenbyte und verarbeitet es. Der genaue Zeitpunkt der Übernahme hängt von drucker-internen Aktivitäten ab.

- (3) Nachdem der Drucker das empfangene Datenbyte intern verarbeitet hat, schaltet er das  $\overline{ACKNLG}$ -Signal kurzzeitig auf L-Pegel. Die Zeit, die der Drucker intern zur Verarbeitung des Datenbytes benötigte, ist hier mit  $t_w$  bezeichnet worden. Sie hängt von drucker-internen Gegebenheiten ab. Mit der abfallenden Flanke des  $\overline{ACKNLG}$ -Signals wird innerhalb des Mikrocomputers das  $\overline{STROBE}$ -Signal wieder auf H-Pegel geschaltet. Dies ist für den Mikrocomputer das Zeichen, daß er mit der Übertragung des nächsten Datenbytes beginnen kann.

Durch das beschriebene Verfahren der Datenübertragung mit Hilfe der beiden Steuerleitungen STROBE und ACKNLG ist sichergestellt, daß der Mikrocomputer erst dann ein neues Datenbyte in den Speicher seines Ausgabeports schreibt und dies dem Drucker meldet (STROBE), wenn der Drucker die Übernahme des vorigen Datenbytes ausdrücklich quittiert hat (ACKNLG).

In Anlehnung an die alte Sitte, den Abschluß eines Geschäftes durch Handschlag zu besiegeln, wird das beschriebene Verfahren der Datenübertragung auch Handshake-Verfahren genannt (handshake = Handschlag).

### Das Ausgabeport des Mikrocomputers

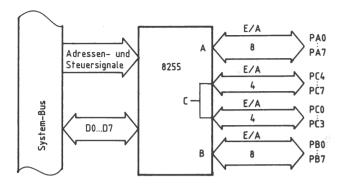

Da für den Datenverkehr zwischen Mikrocomputer und Drucker mehr als acht Leitungen benötigt werden, ist der Drucker nicht über eine einfache 8-Bit-Parallel-Ausgabe an den Mikrocomputer angeschlossen, sondern über den programmierbaren Schnittstellen-Baustein 8255. Bild 21 zeigt ein stark vereinfachtes Blockschaltbild dieses Bausteins; vgl. auch Seite 352ff.

Er enthält die drei voneinander unabhängigen 8-Bit-Daten-Ports A, B und C, die zur Anpassung an die vielfältigen Erfordernisse der Peripheriegeräte in den drei Betriebsarten 0, 1 und 2 benutzt werden können. Die gewünschte Betriebsart muß vor dem ersten Betrieb der einzelnen Ports programmiert werden. Dies geschieht durch Senden eines entsprechenden Steuerwortes an das Steuerwort-Register.

### 6. Interfaces

### 6.1 Parallele Ein/Ausgabe: Drucker-Interface

Bild 21: Vereinfachtes Blockschaltbild des Bausteins 8255; vgl. Bild 1.

Die wesentlichen Merkmale der drei möglichen Betriebsarten sind:

Betriebsart 0: Die drei Ports werden wie Ein- oder Ausgabebaugruppen behandelt, d.h. Daten werden an das ausgewählte Port ausgegeben oder aus ihm gelesen.

Betriebsart 1: Die Ports A und/oder B werden als Eingabe- oder Ausgabe-Port betrieben, wobei jedem der beiden Ports vier Leitungen des Ports C als Steuer- und Quittungssignale mit festgelegter Funktion zugeordnet sind (siehe Bild 22).

Betriebsart 2: Diese Betriebsart, die nur mit Port A möglich ist, gestattet einen 8-Bit-Datenaustausch mit der Peripherie, wobei Daten gesendet und empfangen werden können. Hierbei sind dem Port A fünf Leitungen des Ports C mit fest vorgegebener Funktion zugeordnet, womit der Datenfluß von Port A gesteuert werden kann.

Für die Ansteuerung des Druckers wird die Betriebsart 1 verwendet, die deshalb zunächst näher erklärt wird. Informationen zur Betriebsart 0 finden Sie im vorangegangenen Abschnitt.

# Die Betriebsart 1 des Schnittstellenbausteins 8255

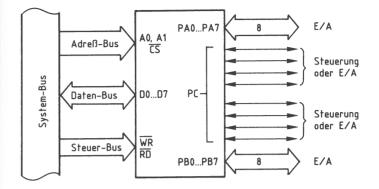

Bild 22 zeigt die grundsätzlichen Einsatzmöglichkeiten des Schnittstellenbausteins 8255 in der Betriebsart 1 und seinen prinzipiellen Anschluß an den System-Bus des Mikrocomputers.

6. Interfaces

6.1 Parallele Ein/Ausgabe: Drucker-Interface

373

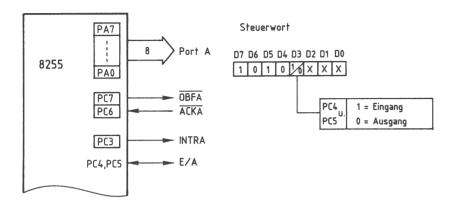

Bild 22: Die Grundfunktionen des 8255 in der Betriebsart 1.

Für den Einsatz des Bausteins als Druckerschnittstelle soll Port A als Ausgabeport dienen. Nach Angaben des Bausteinherstellers haben dann die Portleitungen PC7, PC6 und PC3 fest vorgegebene Funktionen, und die Portleitungen PC4 und PC5 können als Ein- oder Ausgabeleitungen verwendet werden. Eine der Leitungen (PC5) dient als Eingang für das vom Drucker stammende ERROR-Signal.

Die Bildung des für die gewünschte Aufgabe notwendigen Steuerwortes wird später erklärt. Bild 23 zeigt zunächst das für den Druckerbetrieb zutreffende Innenschaltbild des 8255 sowie den Anschluß des Druckers.

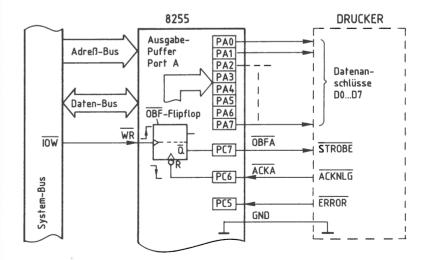

Bild 23: Der Einsatz des Schnittstellenbausteins 8255 in einem Drucker-Interface.

### 6. Interfaces

### 6.1 Parallele Ein/Ausgabe: Drucker-Interface

Bild 24: Das Signal-Zeit-Diagramm zum Datenverkehr zwischen Mikroprozessor und Schnittstellenbaustein 8255 sowie zwischen 8255 und Drucker.

Erklärungen zum Signal-Zeit-Diagramm (Bild 24; siehe hierzu auch Bild 23):

- 1 Der Mikroprozessor stellt das an den Drucker auszugebende Datenbyte auf dem Daten-Bus bereit.

- (2) Mit L-Pegel auf der Steuerleitung  $\overline{\text{IOW}}$  zeigt der Prozessor an, daß er das Datenbyte in den Ausgabe-Puffer von Port A schreiben will.

- ③ Mit der L-H-Flanke des Steuersignals  $\overline{\text{IOW}}$  wird das Datenbyte in den Puffer übernommen und erscheint (nach kurzer Verzögerungszeit) an den Port-Ausgängen PA0 bis PA7. Mit der gleichen Signalflanke wird innerhalb des 8255 das  $\overline{\text{OBF}}$ -Flipflop (Output Buffer Full, Ausgabe-Puffer gefüllt) gesetzt.

- 4 Das Ausgangssignal Q des OBF-Flipflops nimmt L-Pegel an. Es ist über die Portleitung PC7 mit dem STROBE-Eingang des Druckers verbunden und signalisiert dem Drucker mit L-Pegel, daß ein Datenbyte für ihn bereitsteht.

6. Interfaces

6.1 Parallele Ein/Ausgabe: Drucker-Interface

375

- (5) Nachdem der Drucker das Datenbyte übernommen und verarbeitet hat, schaltet er sein ACKNLG-Signal kurzzeitig auf L-Pegel. Mit der H-L-Flanke dieses Signals wird das OBF-Flipflop bzw. das STROBE-Signal wieder auf H-Pegel zurückgesetzt.

- 6 Ab diesem Zeitpunkt kann die Übertragung eines neuen Datenbytes zum Drucker beginnen. Hierzu ist allerdings erforderlich, daß dem Mikroprozessor der H-Pegel der STROBE-Leitung bzw. der Zustand des OBF-Flipflops bekannt ist. Das Programm, das für die gesamte Datenübertragung zwischen Mikroprozessor und Drucker verantwortlich ist, muß also durch Abfrage der Portleitung PC7 den Ausgangszustand des OBF-Flipflops ermitteln. Nur wenn dieser Ausgang H-Pegel führt, darf ein neues Datenbyte an den Drucker übertragen werden.

Die Portleitungen PC4 und PC5 können in der gewählten Betriebsweise als Ein- oder Ausgänge programmiert werden. Da die  $\overline{ERROR}$ -Leitung (PC5) ein Druckerausgang ist und PC4 nicht benötigt wird, werden beide Leitungen als Eingänge programmiert.

Durch Abfrage der Leitung PC5 und Auswertung ihres Signalzustandes (L-Pegel bedeutet »Fehler«) läßt sich z.B. eine Meldung wie »Drucker nicht betriebsbereit« auf dem Bildschirm ausgeben.

## Die Bildung des Steuerwortes für die Betriebsart 1

Die gewünschte Betriebsweise muß vor dem Betrieb der einzelnen Ports programmiert werden. Dies geschieht grundsätzlich durch Senden eines Steuerwortes an das Steuerwort-Register, das sich innerhalb des Schnittstellenbausteins befindet (Bilder 21 und 12). Das Einschreiben des Steuerwortes in das Steuerwort-Register nennt man »Initialisieren« des Bausteins (Setzen von Anfangsbedingungen). Hierzu sind folgende Schritte erforderlich:

- Der Akkumulator des Prozessors muß mit dem Wert des erforderlichen Steuerwortes geladen werden. Hierzu eignet sich der Befehl »MVI A,konst« des Prozessors 8085.

- Aus dem Akku muß das Steuerwort nun an das Steuerwort-Register ausgegeben werden. Hierzu dient der Befehl »OUT adr« des Prozessors 8085. Die Adresse für das Steuerwort-Register ist E3H (hier ist gegenüber Bild 5 A7=1 gesetzt [S4 auf OFF], damit sich die Adresse EXH von denen anderer Ein/Ausgabe-Baugruppen – wie z.B. 5XH in Bild 5 – unterscheidet).

### 6. Interfaces

### 6.1 Parallele Ein/Ausgabe: Drucker-Interface

Bild 25: Die Betriebsart 1 für Port A des 8255.

Die mit X versehenen Signalzustände der Bits D0 bis D2 dienen zur Bestimmung der Funktion von Port B, sofern dieses Port auch in der Betriebsart 1 arbeiten soll. Der Ausgang PC3 wird hier nicht benutzt.

Aus folgenden Bedingungen soll nun das erforderliche Steuerwort gebildet werden; vgl. dazu Bilder 12 und 25:

- Port A und die zugehörigen Leitungen von Port C sollen in Betriebsart 1 arbeiten,

- Port A soll als Ausgabe-Port dienen,

- die nicht mit festen Funktionen belegten Leitungen von Port C, also PC4 und PC5, sollen Eingänge sein,

- Port B und die restlichen Leitungen von Port C sollen in der Betriebsart 0 und als Eingänge betrieben werden.

Hieraus ergibt sich

| für Bit            |   | D6 |   |   |   | 1 |   |   |

|--------------------|---|----|---|---|---|---|---|---|

| der Signalzustand  | 1 | 0  | 1 | 0 | 1 | 0 | 1 | 1 |

| und das Steuerwort |   | A  | A |   |   | I | 3 |   |

Mit der folgenden Befehlssequenz wird das gefundene Steuerwort AB an das Steuerwort-Register mit der Adresse E3 übergeben:

| Befehl          | Kommentar                                                    |  |  |  |  |  |

|-----------------|--------------------------------------------------------------|--|--|--|--|--|

| MVI A,AB OUT E3 | Steuerwort in den Akku laden und an das StwRegister ausgeben |  |  |  |  |  |

| • • •           | •••                                                          |  |  |  |  |  |

6. Interfaces 6.1 Parallele Ein/Ausgabe: Drucker-Interface

377

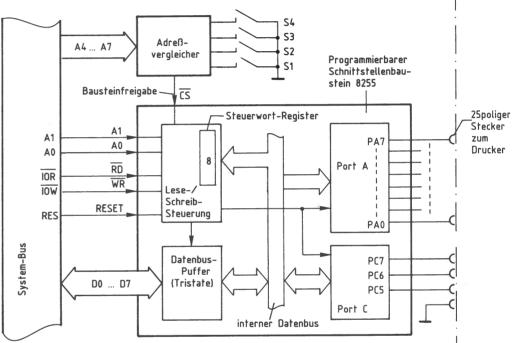

### Blockschaltbild und Arbeitsweise des Drucker-Interfaces

Die Baugruppe Drucker-Interface besteht, wie die programmierbare Parallel-Schnittstelle (Bild 1) aus den Schaltungsteilen Adreßvergleicher und programmierbarer Schnittstellenbaustein (8255). Die zum Anschluß des Druckers notwendigen Datenund Steuer-Leitungen sind auf einen 25poligen Stecker zu führen. Da das Zusammenwirken von Mikroprozessor, Schnittstellenbaustein und Drucker bereits behandelt wurde, wird bei den folgenden Erklärungen nur noch auf die Eingangssignale des Schnittstellenbausteins eingegangen.

Bild 26: Das Blockschaltbild des Drucker-Interfaces.

Alle Signale, die vom Mikroprozessor an den Drucker oder vom Drucker zum Mikroprozessor gelangen, werden über den internen Datenbus und den Datenbus-Puffer transportiert. Die Adressierung der Ports A und C und des Steuerwort-Registers erfolgt über die Adreßleitungen A0 und A1.

Mit Hilfe der Steuerleitungen  $\overline{IOR}$  bzw.  $\overline{IOW}$  wird der Datentransport in die jeweilige Richtung ausgelöst. Ein Datentransport ist jedoch nur möglich, wenn der Schnittstellenbaustein durch den Adreßvergleicher über die Leitung Bausteinfreigabe freigegeben ist. Andernfalls ist der Datenbus-Puffer hochohmig. Zu Adreßvergleicher, Baugruppen-Nr. und Adressierung siehe Seite 353ff.; jedoch ist für das Drucker-Interface die Baugruppen-Nr. EXH einzustellen.

6. Interfaces

6.1 Parallele Ein/Ausgabe: Drucker-Interface

# Die Steuerung der Datenübertragungs-Richtung

Nachdem der Mikroprozessor die Adresse eines der beiden Ports (A oder C) oder des Steuerwort-Registers ausgegeben hat, steuert er durch L-Pegel auf einer der beiden Steuerleitungen  $\overline{IOR}$  oder  $\overline{IOW}$ , ob er Daten aus Port C lesen oder zum Port A bzw. dem Steuerwort-Register senden will. Die beiden Steuerleitungen sind mit den Bausteinanschlüssen  $\overline{RD}$  und  $\overline{WR}$  verbunden (Bild 26). Mit den Pegeln an diesen Eingängen wird innerhalb des Bausteins über die Lese/Schreib-Steuerung die Datenübertragungs-Richtung gesteuert. Im Zusammenwirken mit den Pegeln auf den Bausteineingängen A0, A1 und  $\overline{CS}$  erfolgt der Zugriff zu den beiden Ports und dem Steuerwort-Register folgendermaßen:

| <b>A</b> 1 | <b>A</b> 0 | CS | $\overline{\mathrm{RD}}$ | WR | DatenübertrRichtung, Datenbus-Puffer-Zustand |  |

|------------|------------|----|--------------------------|----|----------------------------------------------|--|

| 1          | 0          | 0  | 0                        |    | Daten von Port C zum System-Bus              |  |

| 0          | 0          | 0  | 1                        | 0  | Daten vom System-Bus an Port A               |  |

| 1          | 1          | 0  | 1                        | 0  | Daten vom System-Bus an das Steuerwort-Reg.  |  |

| X          | X          | 1  | X                        | X  | Datenbus-Puffer vom System-Bus getrennt      |  |

In das Steuerwort-Register kann nur geschrieben werden. Bei H-Pegel am  $\overline{CS}$ -Eingang wird der Datenbus-Puffer in den hochohmigen Zustand geschaltet und dadurch vom System-Bus getrennt. Die Pegel auf den Eingängen A0, A1,  $\overline{RD}$  und  $\overline{WR}$  sind dann für die Funktion des Bausteins bedeutungslos.

Bild 27 zeigt den Stromlaufplan des Drucker-Interfaces. Die Betriebsspannung für die ICs der Baugruppe beträgt 5 V. Sie wird durch den Kondensator C1 abgeblockt. Der Adreßvergleicher wird durch IC1, die Widerstände R1 bis R4 und die Schalter S1 bis S4 gebildet. Durch L-Signal an Pin 6 wird der Schnittstellenbaustein 8255 bei Adressengleichheit freigegeben und kann über die Datenleitungen D0 bis D7 Daten vom Prozessor empfangen oder an ihn ausgeben.

6. Interfaces

6.1 Parallele Ein/Ausgabe: Drucker-Interface

379

Bild 27: Der Stromlaufplan des Drucker-Interfaces; vgl. Bild 15. Das Verbindungskabel zum Drucker führt die 8 Datenbits D0...D7 und einige Steuersignale; vgl. Text.

6. Interfaces

6.1 Parallele Ein/Ausgabe: Drucker-Interface

Die Adreßleitungen A0 und A1 dienen zur Auswahl der im Inneren von IC3 vorhandenen Ports A bis C und des Steuerwort-Registers (Bild 18). Die Leitungen  $\overline{\text{IOR}}$  und  $\overline{\text{IOW}}$  lösen das Lesen bzw. Schreiben der Daten aus.

Das vom Prozessor gelieferte RESET-Signal ist L-aktiv und wird durch IC2.2 invertiert, da IC3 zum Zurücksetzen ein H-Signal benötigt. Hierdurch werden beim Einschalten des Mikrocomputers alle Ports auf Eingabe geschaltet.

Das Betriebsprogramm des Mikrocomputers muß alle notwendigen Programmschritte enthalten, die zum Betrieb des Druckers erforderlich sind; insbesondere muß der Zeitablauf der Signale gemäß Bild 24 realisiert werden. Darauf kann in diesem Buch nicht weiter eingegangen werden.

Für den anzuschließenden Drucker mit Centronics-Schnittstelle muß aus dessen Bedienungshandbuch ermittelt werden, ob die Steuersignale STROBE und ACKNLG den gleichen zeitlichen Verlauf besitzen wie oben beschrieben. Die Centronics-Schnittstelle ist nur hinsichtlich der Steckerbelegung genormt, nicht aber in bezug auf die zeitlichen Bedingungen der Steuersignale.

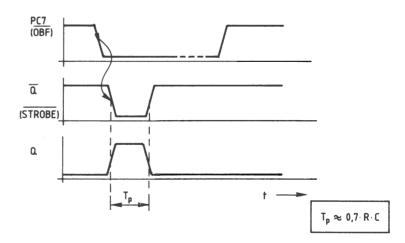

Manche Drucker benötigen als <u>STROBE</u>-Signal einen Impuls von bestimmter Mindestdauer, den der Schnittstellenbaustein 8255 nicht abgeben kann. In diesem Fall muß in die vorhandene <u>STROBE</u>-Leitung eine monostabile Kippstufe eingebaut werden: Bild 28.

6. Interfaces

6.1 Parallele Ein/Ausgabe: Drucker-Interface

381

Bild 28: Der Einbau einer monostabilen Kippstufe in die STROBE-Leitung.

Das folgende Signal-Zeit-Diagramm zeigt den Zusammenhang zwischen dem  $\overline{STRO}$ - $\overline{BE}$ -Signal, das der 8255 erzeugt, und den Ausgangssignalen der zusätzlich eingebauten monostabilen Kippstufe. Es ist darauf zu achten, ob der Drucker einen H-L-Wechsel oder einen L-H-Wechsel an seinem  $\overline{STROBE}$ -Eingang benötigt. Entsprechend ist Q oder  $\overline{Q}$  zu beschalten; siehe Bild 28.

Bild 29: Die Wirkung der monostabilen Kippstufe aus Bild 28. Die Verweildauer ist Tp.

6. Interfaces

6.1 Parallele Ein/Ausgabe: 4fach-Zeitwerk

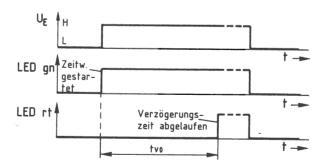

Für viele Anwendungen in der Steuerungstechnik ist die Einhaltung von Verzögerungen zwischen zwei Ereignissen notwendig. Das 4fach-Zeitwerk dient dazu, vier Ausgangssignale zu erzeugen, die nach Ansteuerung durch entsprechende Eingangssignale zeitverzögert auftreten. Die Verzögerungszeiten zwischen Eingangs- und Ausgangs-Signalen können mit Trimm-Potentiometern in weiten Bereichen eingestellt werden. Außerdem wird durch LEDs angezeigt, in welchem Zustand sich die Einund Ausgänge der Zeitstufen befinden.

Das Zeitwerk besteht aus der programmierbaren Parallelschnittstelle (siehe Seite 351ff.) und zusätzlichen Zeitstufen mit Anzeigen. Hierdurch wird es möglich, die Wirkungsweise des Schnittstellenbausteins anhand eines weiteren konkreten Anwendungsbeispiels kennenzulernen.

Ein Einsatzgebiet der Baugruppe besteht z.B. darin, sie als Zeitgeber- und Anzeige-Funktionsgruppe innerhalb einer sogen. Speicherprogrammierbaren Steuerung (SPS) einzusetzen; vgl. Kapitel 3.

### Blockschaltbild und Arbeitsweise des Zeitwerks

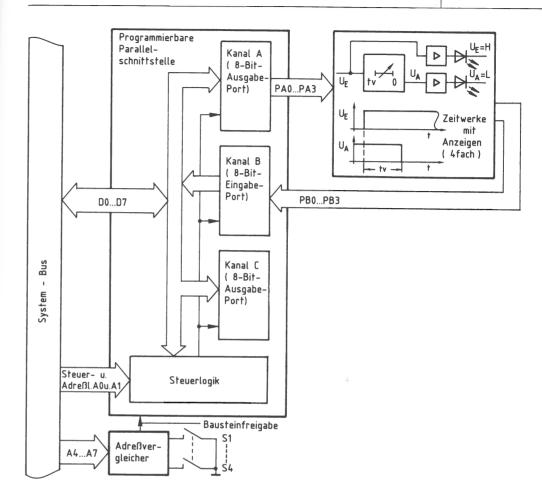

Bild 30 zeigt das Blockschaltbild der Baugruppe. Sie besteht aus den Schaltungsteilen Adreßvergleicher, programmierbare Parallelschnittstelle und Zeitwerke mit Anzeigen. Zunächst wird die Wirkungsweise der Baugruppe anhand dieses Blockschaltbildes erklärt.

Die programmierbare Parallelschnittstelle enthält – wie eingangs dieses Kapitels 6.1 erklärt – drei Datenkanäle, die durch Laden eines Steuerwortes in die interne Steuerlogik als Eingabe- oder als Ausgabe-Ports programmiert werden können. Für den hier vorgesehenen Anwendungsfall wird Kanal A als Ausgabeport und Kanal B als Eingabeport programmiert.

Die Adresse der Steuerlogik und die Portadressen sind durch den schaltungstechnischen Aufbau (Hardware) bestimmt. Der Adreßvergleicher gibt den Schnittstellenbaustein nur dann für den Datenaustausch mit dem Mikroprozessor frei, wenn auf dem Adreß-Bus eine gültige Adresse für eines der drei Ports oder die Steuerlogik ausgegeben wird.

6. Interfaces 6.1 parallele Ein/Ausgabe: 4fach-Zeitwerk

383

Bild 30: Das Blockschaltbild des 4fach-Zeitwerks.

Über die Ausgabeleitungen PA0 bis PA3 des Ports A wird der Block »Zeitwerke mit Anzeigen« angesteuert. Er enthält vier voneinander unabhängige einstellbare Verzögerungsglieder (Zeitwerke), jeweils mit dazugehöriger Anzeige für das Start-Signal ( $U_E = H$ ) und der Anzeige, daß die Verzögerungszeit abgelaufen ist ( $U_A = L$ ).

Die Ausgangssignale der Verzögerungsglieder werden dem Eingabeport B über die Leitungen PB0 bis PB3 zugeführt und können durch Abfrage dieses Ports vom Prozessor gelesen werden.

Bild 31: Der Stromlaufplan des 4fach-Zeitwerks.

6. Interfaces

6.1 Parallele Ein/Ausgabe: 4fach-Zeitwerk

385

# Die programmierbare Parallelschnittstelle und der Adreßvergleicher

Es wird der Schnittstellenbaustein 8255 verwendet. Bild 32 zeigt ein vereinfachtes Innenschaltbild dieses Bausteins, die zu seinem Betrieb notwendigen Verbindungen zum System-Bus und den Anschluß des Adreßvergleichers.

Bild 32: Der Anschluß des Schnittstellenbausteins 8255 und des Adreßvergleichers.

Grundsätzlich können die Datenkanäle A, B und C als Eingabe- oder als Ausgabe- Ports programmiert werden. Je nach gewünschter Betriebsart ist zur Programmierung ein vom Bausteinhersteller vorgeschriebenes Steuerwort in das Steuerwort-Register zu laden, das sich in der Lese/Schreib- und Steuer-Logik des Bausteins befindet. Dieses Laden des Steuerwortes nennt man Initialisieren des Bausteins (initial = am Anfang stehend). Um die in Bild 32 dargestellte Funktion des Bausteins zu erhalten, muß das Steuerwort 82H verwendet werden; zur Bildung der Steuerworte siehe Seite 360ff.

6. Interfaces

6.1 Parallele Ein/Ausgabe: 4fach-Zeitwerk

Das Einschreiben des Steuerwortes in das Steuerwort-Register erfolgt grundsätzlich genauso wie die Übergabe eines Datenwortes an ein Ausgabeport: Man gibt zuerst die Port-Adresse auf dem Adreß-Bus aus und stellt dann das Steuerwort auf dem Daten-Bus bereit. Mit dem Steuersignal  $\overline{IOW}$  wird anschließend die Übernahme des Steuerwortes in das adressierte Register ausgelöst.

Die Tabelle in Bild 33 zeigt, welche Signalpegel an den Leitungen A0, A1 und  $\overline{\text{CS}}$  zur Erzielung der gewünschten Funktionen für unseren Anwendungsfall benötigt werden.

| A1 | AO | RD | WR | CS | Funktion                                    |

|----|----|----|----|----|---------------------------------------------|

| L  | L  | Н  | L  | L  | Daten vom Daten-Bus nach Port A             |

| L  | Н  | L  | Н  | L  | Daten von Port B zum Daten-Bus              |

| Н  | L  | Н  | L  | L  | Daten vom Daten-Bus nach Port C             |

| Н  | Н  | Н  | L  | L  | Daten vom Daten-Bus zum Steuerwort-Register |

| X  | Х  | Х  | X  | Н  | Baustein vom Daten-Bus getrennt             |

Bild 33: Die Signalpegel an den Adreß- und Steuer-Leitungen des Bausteins 8255, abhängig von den Bausteinfunktionen.

X bedeutet, daß die Pegel der damit bezeichneten Leitungen für die Funktion bedeutungslos sind.

Ein Datentransport zwischen Daten-Bus und Baustein ist nur möglich, wenn der  $\overline{\text{CS}}$ -Eingang (Chip-Select = Bausteinauswahl) L-Pegel führt. Das Signal an diesem Eingang, das Bausteinfreigabe-Signal, kommt vom Adreßvergleicher und wird durch IC2.1 invertiert, weil der Adreßvergleicher an seinem Ausgang »OUT« H-Pegel abgibt.

Dieser H-Pegel tritt jedoch nur auf, wenn die Signalkombination auf den Adreßleitungen A4 bis A7 gleich derjenigen Signalkombination ist, die mit den Schaltern S1 bis S4 eingestellt ist. Mit der in Bild 32 dargestellten Schaltereinstellung und den aus Bild 33 entnommenen Pegeln für die Adreßleitungen A0 und A1 ergeben sich nun die Adressen für die drei Ports A, B und C und für das Steuerwort-Register wie in Bild 34 dargestellt.

# 6. Interfaces 6.1 Parallele Ein/Ausgabe: 4fach-Zeitwerk

387

| Α7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | Adressen *) | Angespr. Register |

|----|----|----|----|----|----|----|----|-------------|-------------------|

| 0  | 0  | 0  | 1  | Х  | Χ  | 0  | 0  | 10 14 18 1C | Port A            |

| 0  | 0  | 0  | 1  | Х  | χ  | 0  | 1  | 11 15 19 1D | Port B            |

| 0  | 0  | 0  | 1  | Χ  | χ  | 1  | 0  | 12 16 1A 1E | Port C            |

| 0  | 0  | 0  | 1  | Χ  | Χ  | 1  | 1  | 13 17 1B 1F | Steuerwort-Reg.   |

Bild 34: Die Bildung der Adressen aus den Pegeln der Adreßleitungen A0 bis A7.

\* Die Adreßleitungen A2 und A3 werden hier nicht benutzt. Da ihr Pegel 0 oder 1 sein kann, ergeben sich mehrere gültige Adressen für die Ports bzw. das Steuerwort-Register.

Die Initialisierung des Schnittstellenbausteins kann nun z.B. mit dem Bus-Signalgeber (siehe Kapitel 5.1) in folgenden Schritten vorgenommen werden:

- 1. Adresse 13H (Steuerwort-Register) auf den Adreß-Bus geben

- 2. Steuerwort 82H auf den Daten-Bus geben

- 3. Steuersignal IOW auslösen

Nach dieser Initialisierung haben die Datenkanäle folgende Funktion:

- Kanal A wird Ausgabeport (Adr. 10)

- Kanal B wird Eingabeport (Adr. 11)

- Kanal C wird Ausgabeport (Adr. 12)

Wird die Baugruppe innerhalb eines Mikrocomputer-Systems als Ein/Ausgabe-Baugruppe verwendet, so kann ihre Initialisierung z.B. durch folgendes Programm erfolgen:

| Befehl             | Kommentar                                                                              |

|--------------------|----------------------------------------------------------------------------------------|

| MVI A,82<br>OUT 13 | Akku mit dem Wert des Steuerwortes laden Akkuwert in das Steuerwort-Register schreiben |

|                    | •••                                                                                    |

6.1 Parallele Ein/Ausgabe: 4fach-Zeitwerk

# Die Zeitwerke mit Anzeigen

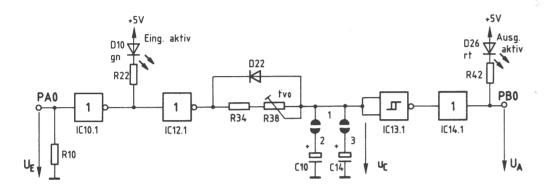

Bild 35 zeigt die Schaltung eines der vier Zeitwerke mit seiner Anzeige. An den Eingang dieser Stufe wird der Ausgang PA0 des Ausgabeports A angeschlossen. Der Ausgang der Stufe wird mit dem Eingang PB0 des Eingabeports B verbunden.

Bild 35: Das Zeitwerk T0 mit seiner Anzeige.

Wenn das Zeitwerk T0 über die Portleitung PA0 einen L-Pegel erhält oder wenn PA0 hochohmig ist (Tristate-Ausgänge!), so befindet sich die Schaltung in ihrer Ruhelage. An ihrem Ausgang PB0 stellt sich dann H-Pegel ein, und die beiden LEDs D10 und D26 leuchten nicht.

Schaltet der Mikrocomputer durch Aussenden eines geeigneten Datenwortes über Port A den Eingang auf H-Pegel, so wird das Zeitwerk gestartet.

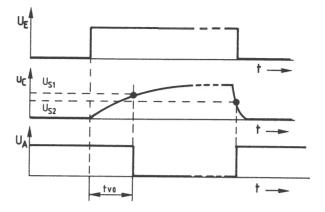

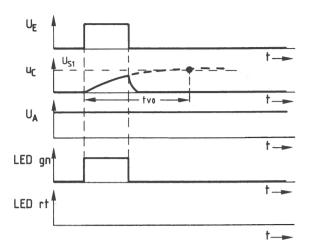

Der Ausgang des ersten Inverters IC10.1 führt dann L-Pegel, so daß die grüne LED D10 leuchtet. Hiermit wird der Start des Zeitwerks angezeigt. Der Ausgang des folgenden Inverters IC12.1 führt den gleichen Signalpegel wie der Eingang des Zeitwerks. Dieser H-Pegel wird durch das RC-Glied verzögert dem Eingang des Schmitt-Triggers IC13.1 zugeführt. Erst wenn sich die Kondensatoren C10 und C14 soweit aufgeladen haben, daß die Schaltschwelle ( $U_{S1}$ ) des Schmitt-Triggers erreicht ist, dann erfolgt ein Signalwechsel von H- nach L-Pegel am Ausgang des Schmitt-Triggers. Gleichzeitig leuchtet LED D26 auf und zeigt den Ablauf der Zeitverzögerung an. Die Verzögerungszeit  $t_{\rm v}$  ist mit dem Trimmpotentiometer R38 einstellbar und hängt von der Wahl der Widerstände R34 und R38 und der Kapazität der Kondensatoren C10 und C14 ab: Bild 36 zeigt die zeitlichen Verläufe der Spannungen  $U_{\rm E}$ ,  $U_{\rm A}$  und  $U_{\rm C}$ .

389

Bild 36: Der zeitliche Verlauf von UE, UA und UC.

Ein Rücksetzen des Zeitwerks kann durch Ausgabe eines geeigneten Datenwortes über Port A erfolgen, indem der Eingang des Zeitwerks wieder L-Pegel erhält. Hierdurch wird der Stromfluß durch die LED D10 unterbrochen. Der Ausgang des Inverters IC12.1 nimmt dann ebenfalls L-Pegel an, und die Kondensatoren entladen sich sehr schnell über die Diode D22 nach Masse. Unterschreitet die Kondensatorspannung  $U_C$  die Ausschaltschwellenspannung  $U_{S2}$  des Schmitt-Triggers, so nimmt dessen Ausgang H-Pegel an. Das folgende Bild 37 zeigt den zeitlichen Zusammenhang zwischen dem Leuchten der beiden LEDs und dem Eingangspegel.

Bild 37: Der Zusammenhang zwischen U<sub>E</sub> und dem Leuchten der LEDs zur Anzeige des gestarteten Zeitwerks und der **a**bgelaufenen Verzögerungszeit.

- 6. Interfaces

- 6.1 Parallele Ein/Ausgabe: 4fach-Zeitwerk

Bild 38: Der zeitliche Verlauf von UE, UC und UA für den Fall, daß UE kürzer als tvo ansteht.

Da die Kondensatorspannung in der zur Verfügung stehenden Zeit die Eingangsschwellenspannung  $U_{S1}$  des Schmitt-Triggers nicht erreicht, faßt dieser den Pegel der Spannung als L-Pegel auf und liefert an seinem Ausgang H-Pegel, so daß die grüne LED nicht leuchten kann.

Die rote LED leuchtet nur so lange, wie die Eingangsspannung ansteht.

# Die Einstellung der Verzögerungszeit

Die Verzögerungszeit  $t_{v0}$  wird durch zwei Einstellmöglichkeiten bestimmt. Durch die Brücken 1-2 und 1-3 ist eine Grobeinstellung in drei Stufen möglich. Eine Feineinstellung kann mit dem Trimmwiderstand R38 vorgenommen werden (Bild 35).

Den kürzesten Zeitbereich  $(2\dots 12~s)$  erzielt man, wenn nur die Brücke zum Kondensator mit der kleinsten Kapazität  $(10~\mu F)$  geschlossen wird (1-2). Der längste Zeitbereich  $(6\dots 65~s)$  ergibt sich durch die Parallelschaltung beider Kondensatoren  $(57~\mu F)$ , indem die Brücken 1-2~und~1-3~geschlossen werden. Wird nur die Brücke 1-3~geschlossen  $(47~\mu F)$ , so ergeben sich  $5\dots 54~s$ .

6. Interfaces

6.1 Parallele Ein/Ausgabe: EPROM-Programmierer

391

Mikrocomputer und andere mikroprozessorgesteuerte Anlagen besitzen zwei Arten von Speicherbausteinen: RAM- und ROM-Speicher; vgl. Kapitel 4.3.

RAM-Speicher sind Schreib/Lese-Speicher, in die Informationen geschrieben und aus denen Informationen gelesen werden können. Nach dem Ausschalten des Gerätes gehen alle Informationen eines RAM-Speichers verloren, wenn die Betriebsspannung nicht z.B. durch Batterien erhalten bleibt.

ROM-Speicher (Read Only Memory, Nur-Lese-Speicher) verlieren ihren Inhalt nicht. Sie können nur gelesen, nicht aber mit aktuellen Daten beschrieben werden.

Es gibt verschiedene Arten von ROM-Speichern: solche, die bereits ab Werk programmiert (»maskenprogrammiert«) sind, und solche, die zunächst unprogrammiert geliefert und erst später bei der Verarbeitung programmiert werden. Diese werden PROM genannt (Programmable ROM, programmierbares ROM).

Maskenprogrammierte ROMs werden wegen des hohen Fertigungsaufwandes nur bei großen Stückzahlen (ab mehreren tausend Exemplaren) hergestellt und besitzen innerhalb einer Serie stets den gleichen Speicherinhalt. Angewendet werden diese ROMs in Serienprodukten, die bestimmte feste Funktionen besitzen (z.B. Heim- und Personalcomputer, Videorecorder, Taschenrechner und Telespiele).

Bei den PROMs gibt es Bauarten, die nur einmal programmiert werden, und solche, die wieder gelöscht und dann erneut programmiert werden können. Der zweite Typ wird EPROM genannt; dies stammt von Erasable PROM, löschbares PROM.

EPROMs speichern Informationen auf Dauer. Falls es erforderlich ist, können sie etwa 10 – 50mal gelöscht und danach wieder neu programmiert werden. Dieser Vorteil hat zu einer breiten Anwendung von EPROMs geführt. Hinzu kommt, daß bestimmte EPROM-Typen »pinkompatibel« zu RAM-Bausteinen sind, d.h. sie besitzen das gleiche Anschlußschema wie diese. Hierdurch können Speicherbaugruppen wahlweise mit RAM- oder EPROM-Speichern bestückt werden, je nach Bedarf.

In diesem Abschnitt wird eine Baugruppe beschrieben, mit der EPROMs des Typs 2716 programmiert werden können. Zunächst wird der Programmiervorgang und das Löschen dieser EPROMs beschrieben. Anschließend werden Schaltung und Funktion der EPROM-Programmier-Baugruppe vorgestellt (ab Seite 397). Die softwaremäßige Ansteuerung geht dagegen über den Rahmen dieses Buches hinaus, da sie stark vom verwendeten Mikrocomputer-System abhängt.

6. Interfaces

6.1 Parallele Ein/Ausgabe: EPROM-Programmierer

### **Das EPROM 2716**

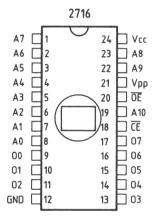

Das EPROM vom Typ 2716 gehört zu einer ganzen Serie von EPROMs, deren Bezeichnung mit 27 beginnt. Die weiteren Bezeichnungsziffern geben die zur Verfügung stehende Speicherkapazität an. So besagt die 16 hier, daß es 16 K (genau 16 × 1024 = 16.384) Speicherzellen besitzt. Da diese entsprechend der Datenbusbreite in 8-Bit-Speicherzeilen (Bytes) angeordnet sind, lassen sich 2048 Datenworte mit je 8 Bits in diesem EPROM speichern. Andere EPROMs dieser Typenreihe, auf die jedoch hier nicht näher eingegangen wird, haben die Bezeichnungen 2732, 2764, 27128 und 27256 mit den entsprechenden Speicherkapazitäten von 32, 64, 128 und 256 K Bit. Bild 39 zeigt die Pin-Belegung des EPROMs 2716. Die Bedeutung der einzelnen Anschlüsse wird anschließend erklärt.

Bild 39: Die Pin-Belegung des EPROM-Bausteins 2716.

## A0 bis A10 (11 Adreβ-Eingänge):

Hier werden die Adreßleitungen A0 bis A10 des MC-Systembus angeschlossen. Mit Hilfe der 2<sup>11</sup> möglichen Signalkombinationen auf diesen Leitungen lassen sich die vorhandenen 2048 Speicherzeilen des EPROMs beim Programmieren und Lesen anwählen.

# O0 bis O7 (8 Daten-Ein/Ausgänge):

Hier werden die Datenleitungen des MC-Systembus angeschlossen. Beim Lesen des EPROMs erscheint an diesen Anschlüssen der Inhalt derjenigen Speicherzeile, die über die Adreßleitungen angewählt ist. Beim Programmieren des EPROMs ist an die Datenleitungen die Information (Datenwort) anzulegen, mit der die adressierte Speicherzeile beschrieben (»programmiert«) werden soll.

6. Interfaces

6.1 Parallele Ein/Ausgabe: EPROM-Programmierer

393

V<sub>cc</sub> und GND:

Anschlüsse für 5 V und 0 V (Versorgungsspannung).

V<sub>pp</sub> (Programmierspannungs-Anschluß):

Während der Programmierung des EPROMs muß die Spannung an diesem Anschluß 25 V betragen. Im übrigen Betrieb, d. h. im Lese- oder im Standby-Betrieb (EPROM nicht angesprochen), muß an  $V_{\rm pp}$  eine Spannung von 5 V anliegen.

$\overline{\text{CE}}$  und  $\overline{\text{OE}}$  (Steuereingänge):

Mit Hilfe der Pegel an diesen Eingängen wird das Programmieren und das Lesen des EPROMs gesteuert.

# Die Betriebsarten des 2716

Abhängig von den Signal-Pegeln an den Steuereingängen und von der Spannung am Anschluß  $V_{pp}$  ergeben sich für das EPROM 2716 die in Bild 40 dargestellten vier Betriebsarten, die anschließend erläutert werden.

| EPROM in der  | Pegel | /Spann | ung an          | Wirkung an   |

|---------------|-------|--------|-----------------|--------------|

| Betriebsart   | CE    | ŌĒ     | V <sub>pp</sub> | 0Ø bis 07    |

| Lesen         | L     | L      | 5 V             | Datenausgabe |

| Standby       | Н     | Х      | 5 V             | hochohmig    |

| Programmieren |       | Н      | 25 V            | Dateneingabe |

| Progr. Prüfen | L     | L      | 5/25 V          | Datenausgabe |

(X: Der Pegel ist für diese Funktion bedeutungslos)

Bild 40: Die Betriebsarten des EPROMs 2716.

#### Lesen:

An den Datenanschlüssen wird der Inhalt der durch die Signalkombination an den Adreßeingängen ausgewählten Speicherzeile ausgegeben. Dies ist die »normale« Betriebsart für ein programmiertes EPROM.

## Standby:

In dieser Betriebsart befindet sich das EPROM im Bereitschaftszustand. Es ist jedoch nicht aktiv, da die Daten-Ein/Ausgänge hochohmig geschaltet sind. Im Standby-Betrieb hat der Speicherbaustein nur eine Leistungsaufnahme von etwa 130 mW gegenüber 520 mW im aktiven Betriebszustand. Dies trägt bei großen Speichereinheiten zu einer erheblichen Entlastung der Stromversorgung bei.

6. Interfaces

6.1 Parallele Ein/Ausgabe: EPROM-Programmierer

Programmieren:

Während der Programmierung muß die Spannung am Anschluß V<sub>pp</sub> 25 V betragen; dies ist die Programmierspannung des EPROMs. Beim Programmieren müssen die Pegel der Steuer-, Adreß- und Datenanschlüsse des EPROMs einen bestimmten zeitlichen Verlauf besitzen, der weiter unten näher erklärt wird.

Programmierung prüfen:

Nach der Programmierung eines EPROMs ist es üblich, seinen Inhalt mit dem gewünschten Inhalt, den Quelldaten, zu vergleichen. Dies kann entweder nach jedem programmierten Byte oder zum Schluß der gesamten Programmierung geschehen. Das Ergebnis dieser Überprüfung führt zu einer Meldung, die besagt, ob der Programmiervorgang erfolgreich war oder nicht. Beim Prüfen des EPROMs kann die Programmierspannung in Höhe von 25 V weiterhin angelegt bleiben.

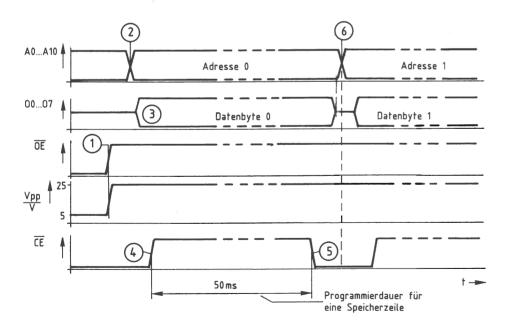

# Der Programmiervorgang beim 2716

In den Datenbüchern der EPROM-Hersteller findet man Signal-Zeit-Diagramme zur Programmierung der Bausteine. Wichtig ist die Einhaltung der in Bild 40 gezeigten Signalpegel: Zum Programmieren muß der Eingang OE einen H-Pegel besitzen, und die Spannung am Anschluß V<sub>pp</sub> muß 25 V betragen. Durch einen H-Impuls von 50 ms Dauer am Anschluß  $\overline{CE}$  wird die Programmierung bewirkt; siehe Bild 41.

Bild 41: Das Signal-Zeit-Diagramm beim Programmieren des 2716.

6. Interfaces 6.1 Parallele Ein/Ausgabe: EPROM-Programmierer

395

Beschreibung des Signal-Zeit-Diagramms von Bild 41:

(1) Zunächst wird das Signal am Steuereingang OE auf H-Pegel geschaltet und die Spannung an V<sub>DD</sub> von 5 V auf 25 V erhöht.

(2) Nun wird die Adresse der ersten zu programmierenden Speicherzeile (hier z.B.

Adresse 0) auf die Adreßleitungen A0 bis A10 gelegt.

(3) Zu diesem Zeitpunkt gelangt das zu programmierende Datenbyte an die Bausteinanschlüsse O0 bis O7; es wird aber noch nicht sofort programmiert.

(4) Nach einer Wartezeit, die garantiert, daß das Datenbyte stabil anliegt, wird das

Signal am Steuereingang  $\overline{CE}$  für 50 ms auf H-Pegel geschaltet.

(5) Nach Ablauf der 50 ms führt CE wieder L-Pegel. Das Datenbyte ist nun im EPROM gespeichert. Vor der Programmierung des nächsten Bytes muß wieder eine Pause von einigen  $\mu$ s abgewartet werden. Die Spannung an  $V_{pp}$  bleibt dabei auf 25 V geschaltet, und OE führt weiterhin H-Pegel.

(6) Der weitere Ablauf gleicht dem ab (2): Zur Programmierung der nächsten Speicherzeile wird die neue Adresse auf die Leitungen A0 bis A10 geschaltet usw.

Da die Wartezeiten zwischen den einzelnen Schritten mit einigen µs gegenüber der 50-ms-Programmierzeit sehr gering sind, wird zur Programmierung eines Bytes (einer Speicherzeile) eine Gesamtzeit von etwa 50 ms benötigt. Die Programmierung aller 2048 Speicherzeilen dauert ungefähr 2 Minuten.

Die in Bild 41 angegebene Reihenfolge beim Anlegen der einzelnen Signale kann auch geändert werden. Zu beachten ist, daß der Programmiervorgang beginnt, wenn die Signale an  $\overline{OE}$  und  $\overline{CE}$  H-Pegel annehmen und an  $V_{pp}$  25 V anliegen.

### Das Löschen des 2716

Die einzelnen Speicherzellen innerhalb eines EPROMs sind aus MOS-Feldeffekt-Transistoren aufgebaut. Ein leitender Transistor stellt den Informationsgehalt einer logischen 0, ein gesperrter den einer logischen 1 dar. Bei einem fabrikneuen EPROM sind alle Transistoren gesperrt, d.h. jede Speicherzeile (8 Bits) enthält den Inhalt 11111111; dies entspricht hexadezimal FF.

Durch die Programmierung werden diejenigen Transistoren, die logisch 0 annehmen sollen, in den leitenden Zustand gebracht. Infolge der hohen Programmierspannung gelangen hierbei Ladungsträger auf das isolierte Gate des bisher gesperrten Transistors und sorgen für eine leitende Verbindung zwischen Source und Drain. Durch die extrem gute Isolierung des Gates bleibt die nur einmal aufgebrachte Ladung und damit der programmierte Zustand des Transistors nach Angaben der EPROM-Hersteller für etwa 10 Jahre erhalten.

6. Interfaces

6.1 Parallele Ein/Ausgabe: EPROM-Programmierer

Durch intensive Bestrahlung der Transistoren mit ultraviolettem Licht ist es möglich, die Gate-Ladung aller Transistoren wieder zu beseitigen. Zu diesem Zweck besitzen EPROMs ein Quarzglasfenster, das UV-Licht durchläßt. Die verwendetete UV-Lichtquelle muß bezüglich ihrer Strahlungswellenlänge, Strahlungsdichte und Leistung bestimmte Anforderungen erfüllen. Die im Handel angebotenen EPROM-Löschgeräte sind hierfür ausgelegt und meist für die gleichzeitige Löschung mehrerer EPROMs geeignet. Ein Löschvorgang dauert etwa 15 bis 25 Minuten.

Da das Sonnenlicht und Leuchtstofflampen ebenfalls UV-Anteile besitzen, ist eine Bestrahlung programmierter EPROMs mit diesen Lichtquellen zu vermeiden. Leuchtstofflampen können EPROMs bei direkter Einwirkung innerhalb von 2 bis 3 Jahren löschen; bei Sonnenlicht ist dies schon innerhalb einer Woche möglich. Das Quarzglasfenster eines programmierten EPROMs ist deshalb grundsätzlich mit einem Aufkleber abzudecken, der mit Hinweisen zum einprogrammierten EPROM-Inhalt versehen werden sollte. Vor dem Löschen eines EPROMs ist das Quarzglasfenster sorgfältig von Klebstoffresten zu reinigen (z. B. mit Spiritus).

# Der Mikrocomputer als Programmiergerät für EPROMs

Aus der Beschreibung des Programmiervorgangs ergibt sich die grundsätzliche Arbeitsweise eines Programmiergerätes; es muß unter Einhaltung bestimmter Zeiten der Reihe nach alle Speicherzeilen des EPROMs adressieren, ferner das für jede Speicherzeile vorgesehene Datenbyte bereitstellen und mit Hilfe einiger Steuersignale den Programmiervorgang auslösen. Vor, während und nach der Programmierung des EPROMs können Meldungen über den Betriebszustand des Programmiergerätes und das Ergebnis einer Programmierkontrolle ausgegeben werden.

Da sich viele der Arbeitsschritte ständig wiederholen, liegt es nahe, zu ihrer Bewältigung einen Mikrocomputer einzusetzen. Bild 43 zeigt den Blockaufbau eines Programmiergerätes, das auf der programmierbaren Parallel-Schnittstelle (siehe Seite 351ff.) basiert.

Die Baugruppe EPROM-Programmierer enthält einen von außen zugänglichen Spezial-IC-Sockel, der das zu programmierende (oder zu lesende) EPROM 2716 aufnimmt. Die erforderliche Programmierspannung muß von einem separaten Netzgerät zur Verfügung gestellt werden. Außerdem sind im EPROM-Programmierer einige LEDs für Betriebszustandsanzeigen und die erforderliche Steuerelektronik vorhanden.

# 6. Interfaces 6.1 Parallele Ein/Ausgabe: EPROM-Programmierer

397

Bild 42: Der Mikrocomputer als EPROM-Programmiergerät.

Im ROM-Speicher des Mikrocomputers befindet sich innerhalb des Betriebssystems oft ein spezielles EPROM-Programmierprogramm, das alle erforderlichen Signale für die Programmierung eines EPROMs bereitstellt; vgl. Bild 41.

Die Bytes, mit denen ein EPROM programmiert werden soll, befinden sich meistens im RAM des Mikrocomputers. Der Benutzer des Programmiergerätes muß vor dem Programmieren dafür sorgen, daß sie dorthin gelangen. Wie schon erwähnt, kann die Software hier nicht behandelt werden.

# Blockschaltbild und Arbeitsweise des EPROM-Programmierers

Bild 43 zeigt das Blockschaltbild der Baugruppe. Sie besteht aus den Schaltungsteilen Adreßvergleicher, programmierbare Parallelschnittstelle, Betriebszustandsanzeige, Steuersignaltreiber und Programmierspannungs-Umschalter.

### 6. Interfaces

### 6.1 Parallele Ein/Ausgabe: EPROM-Programmierer

Bild 43: Das Blockschaltbild des EPROM-Programmierers.

Die programmierbare Parallelschnittstelle (vgl. Seite 351ff.) enthält drei Datenkanäle, die durch Laden eines Steuerwortes in das Steuerwortregister (innerhalb der Steuerlogik) als Eingabe- oder als Ausgabe-Ports programmiert werden können. Dieses Einschreiben des Steuerwortes in das Steuerwortregister nennt man Initialisieren des Bausteins. Da mit dem EPROM-Programmierer sowohl leere EPROMs programmiert als auch programmierte EPROMs überprüft oder gelesen werden sollen, sind die Betriebsfälle Programmieren und Prüfen oder Lesen eines 2716 zu unterscheiden.

6. Interfaces

6.1 Parallele Ein/Ausgabe: EPROM-Programmierer

399

Für das Programmieren des 2716 müssen die Kanäle A, B und C als Ausgabeports initialisiert sein, weil

- die acht Leitungen von Kanal A und drei Leitungen von Kanal C als Adreßleitungen für das zu programmierende EPROM dienen sollen,

- die restlichen Leitungen von Kanal C als Steuer- und Signalleitungen vorgesehen sind,

- die acht Leitungen von Kanal B die Datenbytes zum EPROM übertragen sollen.

Für das Prüfen oder Lesen des 2716 müssen die Kanäle A und C ebenfalls als Ausgabeports, Kanal B jedoch als Eingabeport initialisiert sein, weil

- die Leitungen der Kanäle A und C wie beim Programmieren benutzt werden,

- die Leitungen von Kanal B die Daten vom EPROM zum Systembus übertragen sollen.

Die Adresse des Steuerwort-Registers und die Portadressen sind durch den schaltungstechnischen Aufbau der Baugruppe bestimmt. Der Adreßvergleicher (siehe Bild 2) gibt den Schnittstellenbaustein nur dann für den Datenaustausch mit dem Mikroprozessor frei, wenn auf dem Adreßbus eine gültige Adresse für eines der drei Ports oder das Steuerwortregister ausgegeben wird.

Über die Portleitungen PC3 und PC6 wird die Betriebszustandsanzeige (siehe Bild 43) gesteuert, die mit zwei LEDs die drei folgenden Meldungen ausgibt:

- LED grün, wenn das Programmiergerät initialisiert wurde,

- LED rot, wenn gerade ein EPROM programmiert wird,

- beide LEDs, wenn das Programmiergerät nicht initialisiert ist, d.h. direkt nach dem Einschalten des Gerätes.

Die Steuersignaltreiber, die durch die Portleitungen PC4 und PC5 angesteuert werden, haben die Aufgabe, die erforderlichen Signalpegel und Ströme für die EPROMSteueranschlüsse  $\overline{OE}$  und  $\overline{CE}$  bereitzustellen.

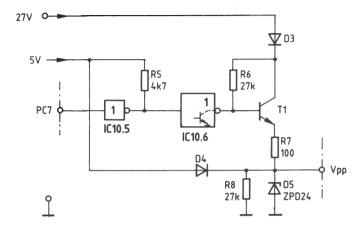

Der elektronische Programmierspannungs-Umschalter, der durch die Portleitung PC7 gesteuert wird, schaltet während des Programmiervorgangs 24 V und während des Prüf- oder Lesevorgangs 5 V auf den EPROM-Anschluß  $V_{\rm pp}$ . Hierzu muß dem Umschalter eine externe Gleichspannung von 27 V zugeführt werden. Die gegenüber den Herstellerangaben um 1 V geringere Programmierspannung (statt 25 V nur 24 V) ist ausreichend.

### 6. Interfaces

## 6.1 Parallele Ein/Ausgabe: EPROM-Programmierer

Bild 44: Der Stromlaufplan des EPROM-Programmierers.

6. Interfaces

6.1 Parallele Ein/Ausgabe: EPROM-Programmierer

401

# Die Programmierbare Parallelschnittstelle und der Adreßvergleicher

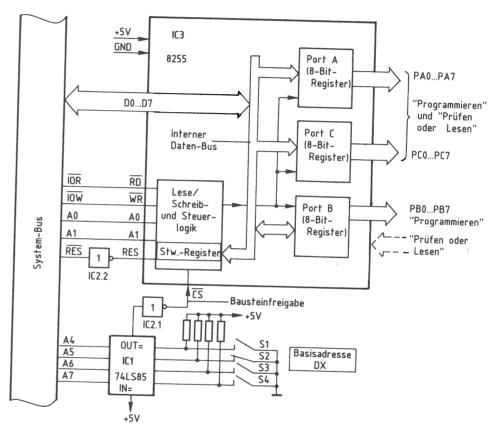

Es wird der Schnittstellenbaustein 8255 verwendet. Bild 45 zeigt ein vereinfachtes Innenschaltbild dieses Bausteins, die zu seinem Betrieb notwendigen Verbindungen zum System-Bus und den Anschluß des Adreßvergleichers.

Bild 45: Der Anschluß des Schnittstellenbausteins 8255 und des Adreßvergleichers.

Grundsätzlich können die Datenkanäle A, B und C als Eingabe- oder Ausgabeports programmiert werden. Je nach gewünschter Betriebsart ist zur Programmierung ein vom Bausteinhersteller vorgeschriebenes Steuerwort in das Steuerwort-Register des 8255 zu laden, das sich in der Lese/Schreib- und Steuer-Logik des Bausteins befindet. Dieses Laden des Steuerwortes nennt man Initialisieren des Bausteins (initial = am Anfang stehend).

6. Interfaces

6.1 Parallele Ein/Ausgabe: EPROM-Programmierer

Um den Baustein für das Programmieren eines EPROMs zu initialisieren, muß das Steuerwort 80H verwendet werden. Für das Prüfen oder Lesen eines EPROMs ist das Steuerwort 82H erforderlich. Die Bildung der Steuerworte wurde ab Seite 360 erklärt.

Das Einschreiben des Steuerwortes in das Steuerwort-Register erfolgt wie die Übergabe eines Datenwortes an ein Ausgabeport: Man gibt zuerst die Port-Adresse auf dem Adreß-Bus aus und stellt dann das Steuerwort auf dem Daten-Bus bereit. Mit dem Steuersignal  $\overline{\text{IOW}}$  wird anschließend die Übernahme des Steuerwortes in das Steuerwort-Register ausgelöst.

Ein Datentransport zwischen Daten-Bus und Baustein ist nur möglich, wenn der  $\overline{\text{CS}}$ -Eingang (Chip Select = Bausteinauswahl) L-Pegel führt (Bild 45). Das Signal an diesem Eingang, das Bausteinfreigabe-Signal, kommt vom Adreßvergleicher und wird durch IC2.1 invertiert, weil der Adreßvergleicher an seinem Ausgang OUT einen H-Pegel abgibt.

Dieser H-Pegel tritt jedoch nur auf, wenn die Signalkombination auf den Adreßleitungen A4 bis A7 gleich derjenigen Signalkombination ist, die mit den Schaltern S1 bis S4 eingestellt wurde. Mit der in Bild 45 dargestellten Schalter-Einstellung ergeben sich die Adressen für die drei Ports A, B und C und für das Steuerwort-Register wie in Bild 46 dargestellt.

| Α7 | A6 | A5 | A4 | А3 | A2 | A1 | Α0 | Adressen    | angespr. Register |

|----|----|----|----|----|----|----|----|-------------|-------------------|

| 1  | 1  | 0  | 1  | Х  | Χ  | 0  | 0  | DO D4 D8 DC | Port A            |

| 1  | 1  | 0  | 1  | Х  | Χ  | 0  | 1  | D1 D5 D9 DD | Port B            |

| 1  | 1  | 0  | 1  | Х  | Χ  | 1  | 0  | D2 D6 DA DE | Port C            |

| 1  | 1  | 0  | 1  | Χ  | Χ  | 1  | 1  | D3 D7 DB DF | Steuerwort-Reg.   |