Einleitung

Die Baugruppe 16K RAM/ROM ist vom Grundaufbau identisch mit der Baugruppe 8K RAM/ROM.

Der wesentliche Unterschied besteht in den unterschiedlichen Speicherbausteinen und einer optionalen Abschalttechnik.

In der 16K-Variante kommen die Bausteine 6264 (RAM) bzw. 2764 (EPROM) zum Einsatz, im Gegensatz zu den in der 8K-Variante verwendeten Chips 6116 (RAM) bzw. 2716 (EPROM).

Um die Anzahl der Speicherbaugruppen in einem Mikrocomputer-System möglichst klein zu halten, werden besonders für Anwendungen mit umfangreichen Programmen Speicherbaugruppen mit höherer Speicherkapazität benötigt.

Die in diesem Abschnitt beschriebene 16-K-RAM/EPROM-Speicherbaugruppe kann mit maximal 8 Speicherbausteinen zu je 2 K Byte Speicherkapazität bestückt werden. Die Bausteine können sowohl RAM- als auch EPROM-Speicher sein. Eine gemischte Bestückung ist ebenfalls möglich. Zusätzlich ist die Baugruppe mit einem 2-K-Urladerspeicher (s. u.) bestückbar.

Schaltung und Funktionsbeschreibung

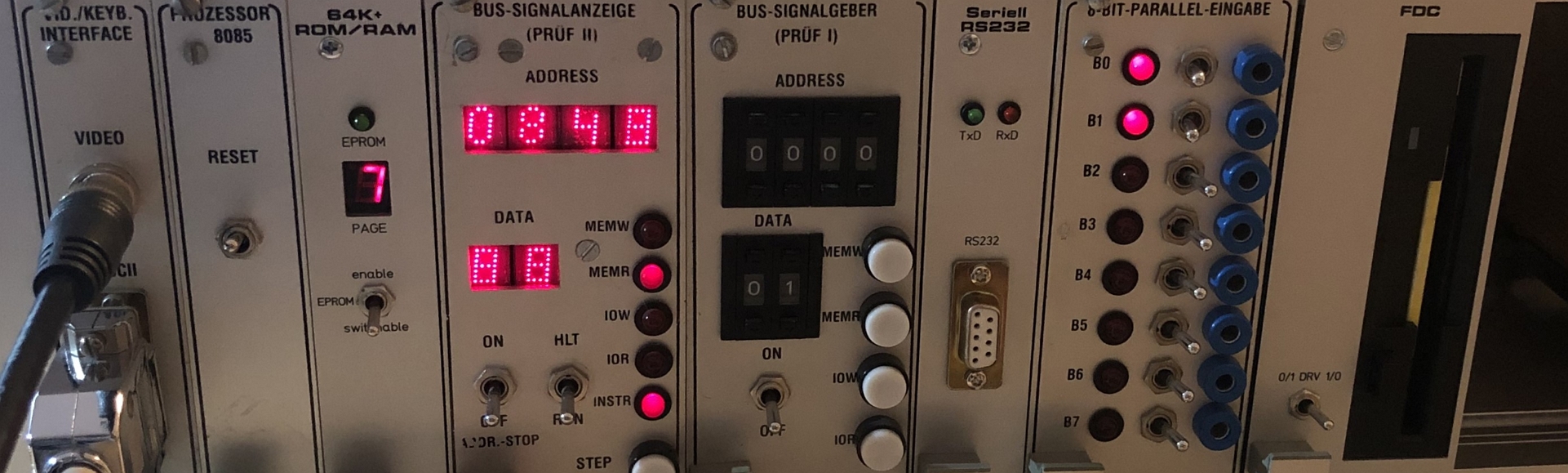

Bild 35 zeigt den Stromlaufplan der Baugruppe. Sie sollten diesen Plan bei allen folgenden Erklärungen mitbenutzen.

Hinweise zur Urlader-Einrichtung (siehe Bild 41):

Sie wird immer dann erforderlich, wenn der Systemspeicher des Mikrocomputers ab der Adresse 0000 mit Schreib-Lese-Speicher ausgerüstet werden soll. Da der Mikroprozessor nach einem System-Start oder einem Reset den ersten auszuführenden Befehl unter der Adresse 0000 erwartet, muß zunächst ab dieser Adresse ein ROM eingeblendet werden. Dieses ROM bezeichnet man als Urlader-ROM, weil darin üblicherweise ein Programm abgelegt wird, welches das eigentliche Verarbeitungsprogramm in den Systemspeicher des Mikrocomputers laden soll, z.B. von einem Massenspeicher (Floppy Disk). Nach Beendigung dieses Ladevorgangs wird der Prozessor durch einen Sprungbefehl veranlasst, zum geladenen Verarbeitungsprogramm zu verzweigen. Nach Ausführung des Sprungbefehls wird das Urlader-ROM abgeschaltet.

Bild 35: Der Stromlaufplan der 16-K-RAM/EPROM-Baugruppe

Baugruppen-Auswahl

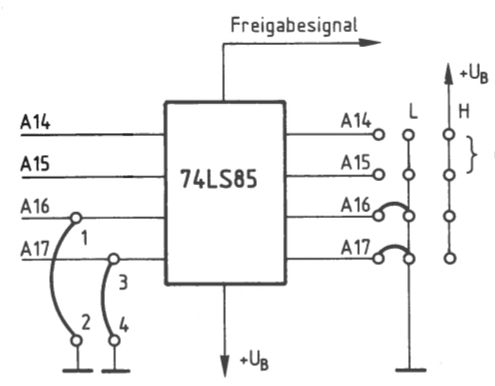

Bei dieser Speicherbaugruppe wurde eine Volldecodierung angewendet, bei der alle 16 Adressleitungen an der Decodierung der Baugruppe bzw. der Speicherbausteine beteiligt sind. Die zusätzlichen Anschlüsse für A16 und Al7 sind für spätere Anwendungen vorgesehen.

Die Baugruppenauswahl erfolgt über die Adressleitungen A14 und A15, mit denen sich vier Baugruppen zu je 16 K Byte Speicherkapazität adressieren lassen. Bild 36 zeigt den 4-Bit-Komparator 74LS85, der zur Baugruppenauswahl dient.

Bild 36: Die Auswahl von 16-K-Speicherbaugruppen.

Einstellung des Adressbereiches über die Lötbrücken

| A17 | A16 | A15 | A14 | Adressbereich |

|---|---|---|---|---|

| L | L | L | L | 0000 – 3FFF |

| L | L | L | H | 4000 – 7FFF |

| L | L | H | L | 8000 – BFFF |

| L | L | H | H | C000 – FFFF |

Mit Hilfe der Lötbrücken A14 und A15 lässt sich der Adressbereich einstellen, in dem die Speicherkarte arbeiten soll.

Baustein-Auswahl

Der 1-aus-8-Decoder 74LS138 (Bild 35) dient zur Auswahl der Speicherbausteine. Er decodiert die Adresssignale A11 … A13. Sein Enable-Eingang (EN) wird vom Freigabesignal des 4-Bit-Komparators 74LS85 aktiviert.

Sobald der Mikrocomputer eine Adresse auf den Adressbus gibt, die im Adressbereich der Speicherbaugruppe liegt, steht das CS-Signal unmittelbar am ausgewählten Speicherbaustein an.

Schreib-Lese-Steuerung

Mit Hilfe der Speicher-Steuereingänge CS, WE und OE (siehe Bild 35) werden die Speicher gelesen (EPROM) bzw. gelesen oder beschrieben (RAM) oder auch gesperrt. Die hierzu an den Steuereingängen erforderlichen Pegel können Sie Bild 37 entnehmen. Von den fünf dargestellten Signalkombinationen kommen im hier betrachteten System nur die Kombinationen 2, 3 und 5 vor.

Funktion der Steuereingänge der Speicherbausteine

| Kombi-Nr | /CS | /OE | /WE Vpp | Funktion RAM | Funktion ROM |

|---|---|---|---|---|---|

| 1 | L | L | L | WRITE | Baustein gesperrt |

| 2 | L | L | H | READ | READ |

| 3 | L | H | L | WRITE | Baustein gesperrt |

| 4 | L | H | H | Baustein gesperrt | Baustein gesperrt |

| 5 | H | X | X | Baustein gesperrt | Baustein gesperrt |

Baustein gesperrt: Ausgänge hochohmig

Die Bedeutung der Anschlussbezeichnungen:

- CS: Chip Select = Bausteinauswahl, low-aktiver Steuereingang. Ein H-Signal an diesem Eingang bewirkt, dass die Datenanschlüsse des Speicherbausteins hochohmig werden.

- OE: Output Enable = Datenausgangs-Freigabe, low-aktiver Steuereingang. Ein H-Signal an diesem Eingang verhindert ein Lesen der gespeicherten Daten.

- WE: Write Enable = Schreibfreigabe, low-aktiver Steuereingang

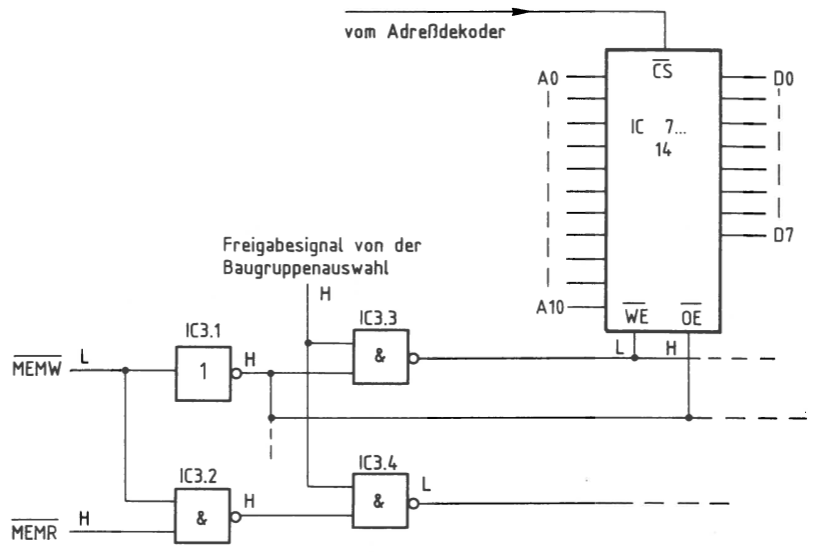

Steuerung des Schreibvoganges

Bild 38 zeigt den Schaltungsteil, der für die Steuerung des Schreibvorgangs sorgt. Zum Einschreiben von Daten in die Speicherbausteine ist entsprechend Bild 37 die Signalkombination Nr. 3 erforderlich. Das CS-Signal liefert der Adressdecoder.

Bild 38: Die Steuerung des Schreibvorgangs.

Führt MEMW L-Pegel, so tritt nach dem Inverter IC3.l ein H-Pegel auf. Dieser H-Pegel gelangt an die OE-Eingänge (Output Enable) der Speicherbausteine, wo- durch ihre Datenanschlüsse intern auf »Einschreiben in den Speicher« geschaltet werden. Nach außen hin wirken sie dadurch hochohmig. Die UND-Verknüpfung des invertierten MEMW-Signals mit dem Freigabesignal der Baugruppenauswahl durch IC3.3 erzeugt einen L-Pegel an den WB-Eingängen (Write Enable) der Speicherbau- steine. L-Pegel an diesem Eingang eines RAM-Bausteins ermöglicht das Einschreiben von Daten in den Speicher.

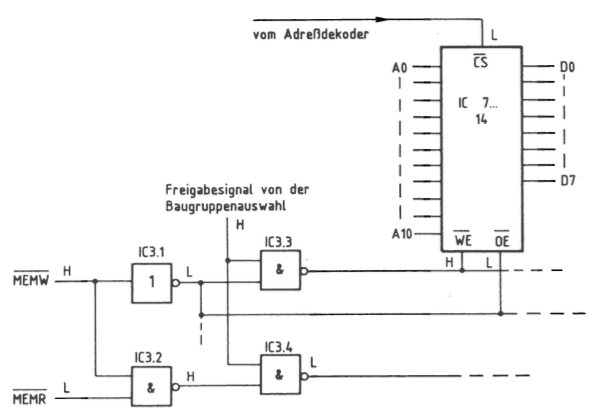

Die Steuerung des Lesevorgangs

Soll der Inhalt einer Speicherzeile gelesen werden, so müssen die Pegel der drei Steuereingänge der Signalkombination Nr. 2 (CS = L, OE = L, WE = H) entsprechen; siehe Bild 37. Dieser Signalzustand ist in Bild 39 eingetragen.

Das CS-Signal wird vom Adreßdecoder erzeugt. Führt zusätzlich das Steuersignal MEMR L-Pegel, so hat MEMW einen H-Pegel, weil der Zustand MEMW = MEMR = L bei normalem Betrieb nicht vorkommt.

Bild 39: Die Steuerung des Lesevorgangs.

Die Steuerung der Datenflussrichtung

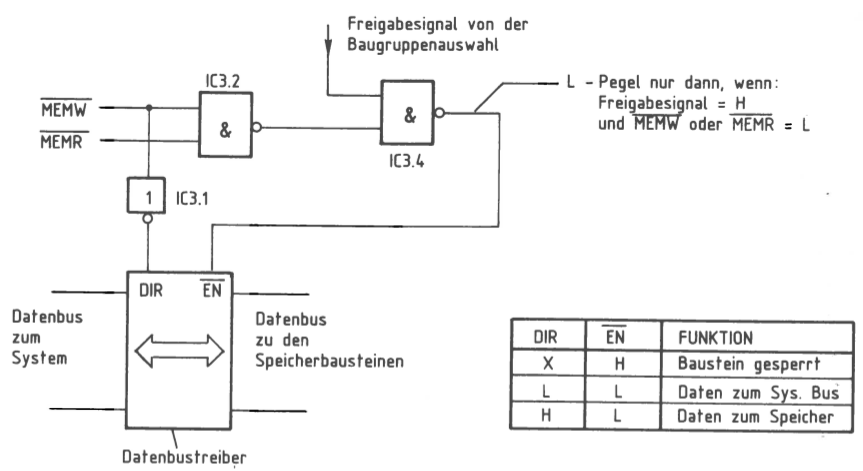

Der Datenbustreiber 74LS245 (Bild 40) besitzt die beiden Steuereingänge DIR und EN. Ein H-Pegel am EN-Eingang (Enable = ermöglichen) schaltet die Datenleitungen auf beiden Seiten des Treiberbausteines in den hochohmigen Zustand (Tristate). Ein L-Pegel gibt den Datenfluss in einer der beiden möglichen Richtungen frei. Diese Datenflussrichtung wird mit dem Steuersignal MEMW über den Steuereingang DIR (Direction = Richtung) bestimmt. Bei einem Schreibvorgang (MEMW = L) liegt am DIR-Eingang ein H-Pegel an, und die Daten gelangen vom System-Bus in den Speicher. Bei einem Lesevorgang liegt am DIR-Eingang L-Pegel an, und die Daten gelangen vom Speicher zum System-Bus.

Die Freigabe des Datentransportes erfolgt allerdings nur dann, wenn

- die Baugruppe freigegeben ist, d. h. eine für die Baugruppe gültige Adresse auf dem Adreßbus ansteht, und

- entweder das Steuersignal MEMW oder MEMR einen L-Pegel führt.

Bild 40: Die Steuerung der Datenflussrichtung.

Stromlaufplan

Bild 41: Der Stromlaufplan der 16-K-RAM/EPROM-Baugruppe mit Urlader-Einrichtung.

Leiterplatte

Lötseite

Bestückungsseite

Bestückungsplan

Die Lötbrücken 1-2, 3-4 sind zu schließen.

Die Lötbrücke 5-6, sofern das Ur-Lade-EPROM nicht verwendet wird.